강의 주소 : 연남대 최규상 교수님 컴퓨터 구조 강의 (2015년)

Chapter 3. Arithmetic for Computers

3.1 Introduction

1) Arithmetic for Computers

정수 영역의 operation

- 덧셈과 뺄셈

- 곱셈과 나눗셈

- 오버플로우 주의

Floating-point real numbers

- 표현과 연산

3.2 Addition and Substraction

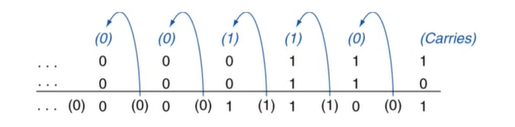

1) Integer Addtition

- 정수형 표현 가능 범위를 벗어나면 오버플로우 발생

- 피연산자가 양의 값(+ve)과 음의 값(-ve)인 덧셈에서는 오버플로우가 발생하지 않는다. 하지만 피연산자 2개 모두 양의 값이거나 음의 값인 경우 오버플로우가 발생할 수도 있다.

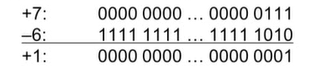

2) Integer Substraction

- 2번째 피연산가 음의 값인 덧셈처럼 비트 계산 -> 2번째 피연산자를 음수로 만든 후 비트 덧셈

- 정수형 표현 가능 범위를 벗어나면 오버플로우 발생

- 피연산자가 양의 값(+ve)과 음의 값(-ve)인 덧셈에서는 오버플로우가 발생하지 않는다. 하지만 피연산자 2개 모두 양의 값이거나 음의 값인 경우 오버플로우가 발생할 수도 있다.

3) Dealing with Overflow

- C언어의 경우 오버플로우를 무시한다.

- 다른 언어(Ada, Fortan)에서는 오버플로우 발생 시 예외를 발생시킨다.

- 오버플로우 발생 시 exception handler 호출

- PC(프로그램 카운터)를 exception program counter(EPC) 레지스터에 저장

- 미리 정의된 handler 주소로 점프

- mfc0(coprocessor 레지스터로부터 move) instruction은 corrective action 후 return하기 위해 EPC의 값을 찾아낼 수 있다.

-> 4장에서 자세히

4) Arithmetic for Multimedia

-

graphics와 media는 8-bit, 16-bit 데이터의 벡터 기반 작업을 수행한다.

- partitioned carry chain을 사용해 작업

- SIMD(Single-Instruction, Multiple-Data) = 하나의 instruction으로 여러 데이터 처리

-

Saturating operations

- 오버플로우 발생 시 결과를 표현 가능 범위에서 최대값을 준다.

- 예) 오디오의 clipping, 비디오의 saturation

3.3 Multiplication

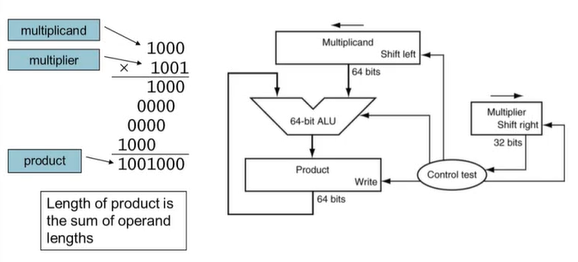

1) Multiplication

곱셈 하드웨어의 초기 버전

-> ALU가 64-bit으로 32-bit 두 수를 곱하는데 64-bit의 ALU를 사용하게 된다.

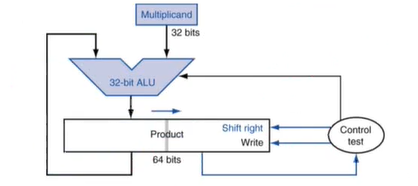

Optimized Multiplier(Sequencial version)

-> 병렬 단계를 수행 : add & shift

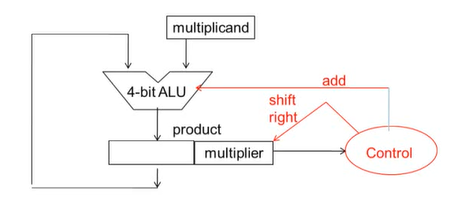

Add & Right Shift Multiplier HW

덧셈과 오른쪽 shift의 반복을 통한 곱셈기

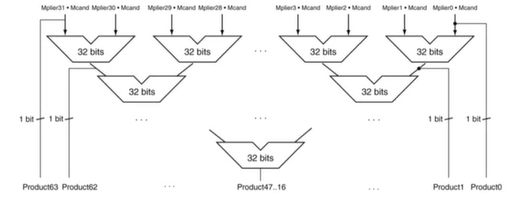

Faster Multiplier

Sequencial version은 4-bit의 수를 곱하려면 4번의 반복 필요 -> 여러 adder 사용 : 결과를 빨리 얻을 수 있지만, HW resource를 많이 사용하게 되므로 비용이 많이 든다.

-> pipeline화가 가능하다. 각각의 곱셈을 병령적으로 수행해 적은 HW resource로도 빠른 연산이 가능하다.

2) MIPS Multiplication

- product 2개의 32-bit 레지스터 사용

- HI : most-significant 32-bits

- LO : least-significant 32-bits

명령어

- mult rs, rt / multu rs, rt : HI와 LO로 64-bit의 product 생산(곰셈 수행)

- mfhi rd / mflo rd : HI와 LO로부터 rd로 move(만약 product가 32 bits보다 커서 오버플로우가 될지 HI 값을 미리 확인할 때 사용)

- mul rd, rs, rt : product의 하위 32-bit를 rd로 -> mult, multu가 64-bit 결과라면 mul은 32-bit 결과

3.4 Division

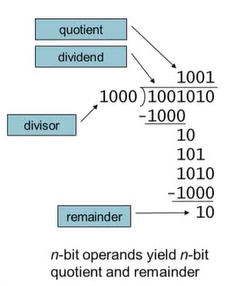

1) Division

- divisor(나누는 수)가 0인지 확인

- 긴 나눗셈의 접근 법

- 현재까지의 dividend 자릿수가 divisor 자릿수보다 크거나 같으면 몫의 현재 비트에 1을 넣고 dividend에서 divisor만큼 뺀다.

- 그렇지 않다면 몫의 현재 비트에 0을 넣고 dividend의 비트자리를 한 단계 뒤로 추가한다.

- Restoring division : dividend에서 divisor만큼 뺐는데 음수가 된 경우, 다시 divisor를 더해서 복원해줘야 한다.

- Signed division : 절대값을 사용해 나눗셈을 한다. 그리고 몫, 나머지의 부호를 조정한다.

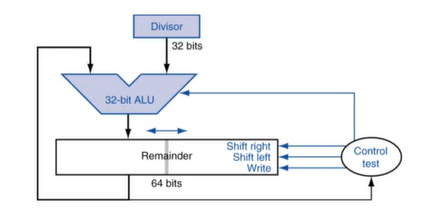

나눗셈 하드웨어의 초기 버전

-> 곱셈기의 초기버전처럼 64-bit의 ALU와 64-bit의 Divisor 사용

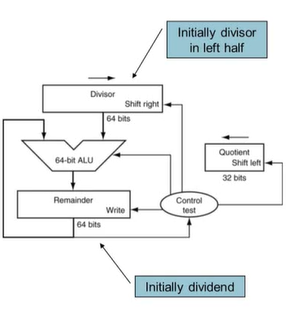

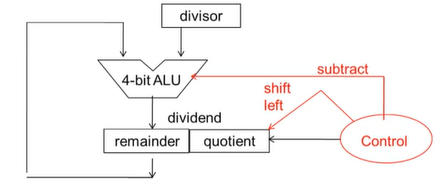

Optimized Divider(Sequencial version)

-> partial-remainder에 뺄 때마다 하나의 사이클 진행

-> 곱셈기와 유사하다.

Left Shift & Subtract Division HW

Faster Divider

- multiplier처럼 병렬적인 HW를 사용할 수 없다. -> 나눗셈에서는 remainder에 divisor를 뺀 결과가 음수인지 아닌지에 따라 다르게 동작하기 때문

- SRT division과 같은 새로운 알고리즘을 사용해 단계마다 동시에 여러 개의 quotient(몫) 비트를 구할 수 있다. -> 여전히 여러 단계 필요

2) MIPS Division

- product 2개의 32-bit 레지스터 사용

- HI : 32-bits remainder(나머지)

- LO : 32-bits quotient(몫)

명령어

- div rs, rt / divu rs, rt : 오버플로우는 발생하지 않는지, 0으로 나누는지 확인 -> 결과에 접근하기 위해 mfhi, mflo 사용

3.5 Floating Point

1) Floating Point(부동소수점)

- 정수가 아닌 아주 작은 수나 아주 큰 수를 표현하기 위해 사용

- Like scientific notation

- -2.34 * 10^56 (normalized) = -2.34e56

- 0.002 * 10^(-4) (not normalized) = 2.0e-7

- 987.02 * 10^9 (not normalized) = 9.8702e11

- binary : ±1.xxxxxxx_2 * 2^(yyyy)

- C언어에서 float형, double형

2) Floating Point Standard

- Defined by IEEE Std 754-1985

- 표현하는 방식이 많아지자 개발됨 : scientific code의 이식성 문제를 해결하기 위해

- 현재 대부분 보편적으로 체택하고 있음

- 2개의 표현법

- single-precision(32-bit)

- double-precision(64-bit)

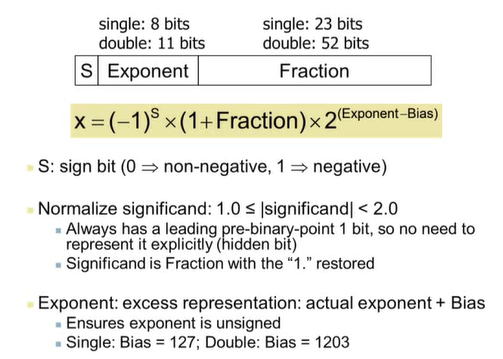

3) IEEE Floating-Point Format

4) Floating-Point Precision

Relative precision

- 모든 fraction(기수) 비트는 significant

- single : fraction이 23비트 -> 2^(-23)의 정확도, 10진법 기준 소숫점 6자리까지

- double : fraction이 52비트 -> 2^(-52)의 정확도, 10진법 기준 소숫점 16자리까지

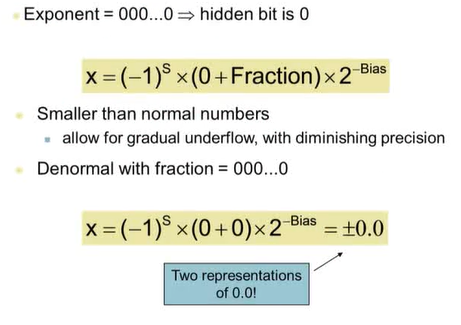

5) Denormal Numbers

비정규 숫자

6) Infinities and NaNs

Infinity

- Exponent = 111...1, Fraction = 000...0

- subsequent calculation에 사용될 수 있다.

NaNs

- Exponent = 111...1, Fraction != 000...0

- illegal 혹은 undefined result 표현

- subsequent calculation에 사용될 수 있다.

7) Floating-Point Addition

- 소숫점 정렬 : 작은 수를 큰 수에 맞춤

- significands끼리 더함

- 결과를 정규화하고 오버플로우, 언더플로우 검사

- 필요하다면 반올림 혹은 비정규화

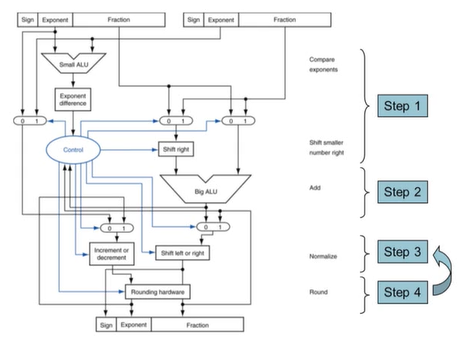

8) FP Adder HW

- 정수 가산기보다 훨씬 더 복잡하다.

- 한 번의 clock cycle에 작업을 하기에는 cycle이 오래 걸릴 수 있다.

- integer operation보다 훨씬 더 느림

- 느린 clock은 전체 instruction들을 느리게 만듬

- 따라서 FP adder는 여러 번의 cycle로 동작한다.

- pipeline화 될 수 있다. = 병렬적

- 하나의 명령에는 여러 cycle이 걸리지만 throughput을 높여 여러 개의 명령어를 동시에 실행하므로 단위 시간당 FP adder의 가능한 작업 수는 증가

9) Floating-Point Multiplication

- Add exponents

- Multiply significands

- 결과를 정규화하고 오버플롱, 언더플로우 검사

- 필요하다면 반올림 혹은 비정규화

- 피연산자들의 부호로부터 결과 부호 결정

10) FP Arithmetic HW

- FP multiplier의 복잡도는 FP adder와 비슷하다.

- FP 산술 HW는 보통 다음 기능들을 지원한다. : 덧셈, 뺄셈, 나눗셈, 역수, 분모, 제곱 등

- FP operation은 일반적으로 여러 cycle로 동작한다.