Vitrual Memory

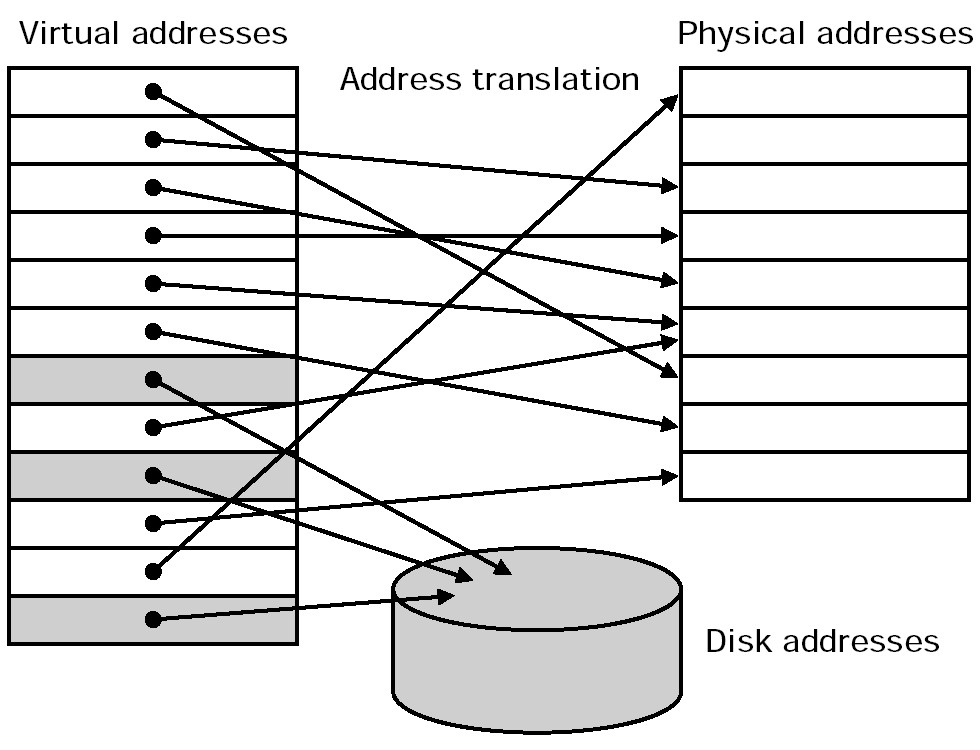

개요

하나의 컴퓨터에서 1개의 프로그램만 실행시키면

프로그램을 메모리에 통째로 올리고 실행시키면 편리함

하지만 1컴퓨터, 1프로그램은 절대로 실행되지 않는다.

logical memory

memory with infinite capacity

위의 글처럼 논리적 메모리는 무한한 주소를 가진 메모리 공간이고 이 논리적 주소 공간을 물리적 메모리에 할당하는것이 바로 과제이다.

방법

주소가 쭉 있으면 paging 함

특정 page 크기로 나눔

예를 들어 0~2^(n-1) 까지의 주소가 있다면

0~2^32 -1 = 4GB짜리 메모리이고,

이를 페이지 사이즈로 나누고 페이지 번호를 붙인다.

physical memory 역시 page 크기로 분할함

하나의 단위를 일반적으로 Frame이라 부름

virtual 한 page를 물리적 frame에 놔도 배치가 가능함

배치 프레임 넘버를 table로 만들어서 관리를 하면 가상 주소에 대해서 실제 메모리 주소가 어디에 배치되어있는지 찾아갈 수 있기 때문이다.

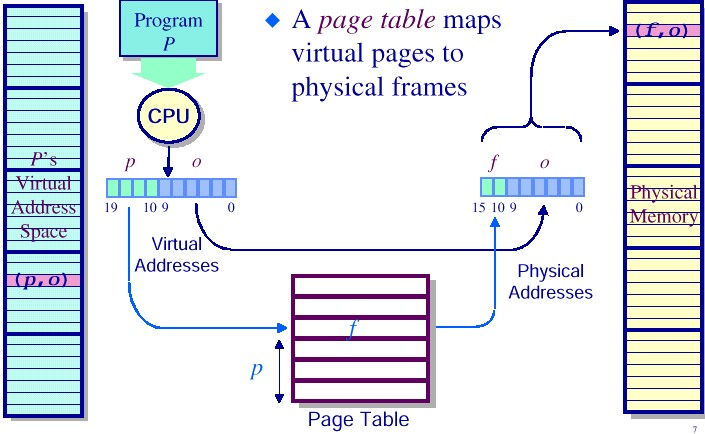

page table maps virtual pages to physical frames

가상 CPU로 접근이 일어나면 page table을 통해 실제 물리적 주소를 찾을 수 있음

페이지 테이블은 누가 관리 하는가?

운영체제에서 관리하고 잇음

각 프로세스마다 page table이 어디올라가는 알아야함

이 정보는 CPU가 가지고 있음

페이지테이블 베이스 주소와 virtual address를 이용해서 page table을 찾아갈 수 있음. 이를 바탕으로 page table에서 정보를 가지고오게 되어있음. (valid/invalid || dirty bit || reference)

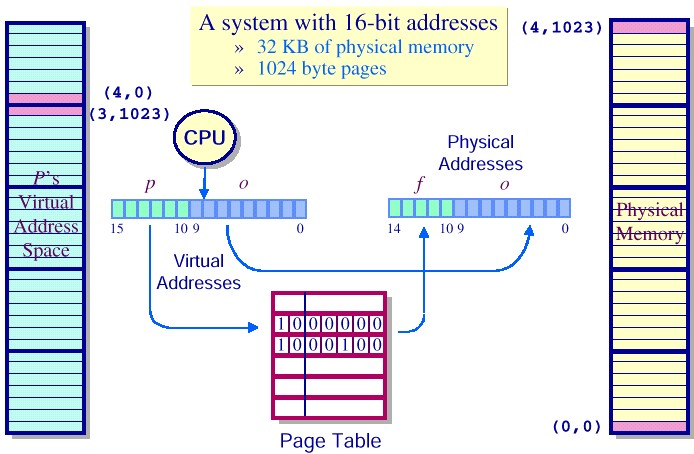

페이지리딩 예시

Demand paging

페이지를 필요할 때 쓰겠다 라는 뜻.

프로그램을 실행한다고 한번에 모든 정보를 메모리에 다 올리지 않는다. 이에 프로그램 사이즈가 더 이상 물리적 메모리 사이즈에 구속당하지 않는다. 메모리가 적게 필요하고 더 많은 프로세스 사용 가능해진다.

적은 I/O가 필요하고 빠른 반응 가능해진다. 이런 페이징을 함으로써 많은 장점이 발생한다.

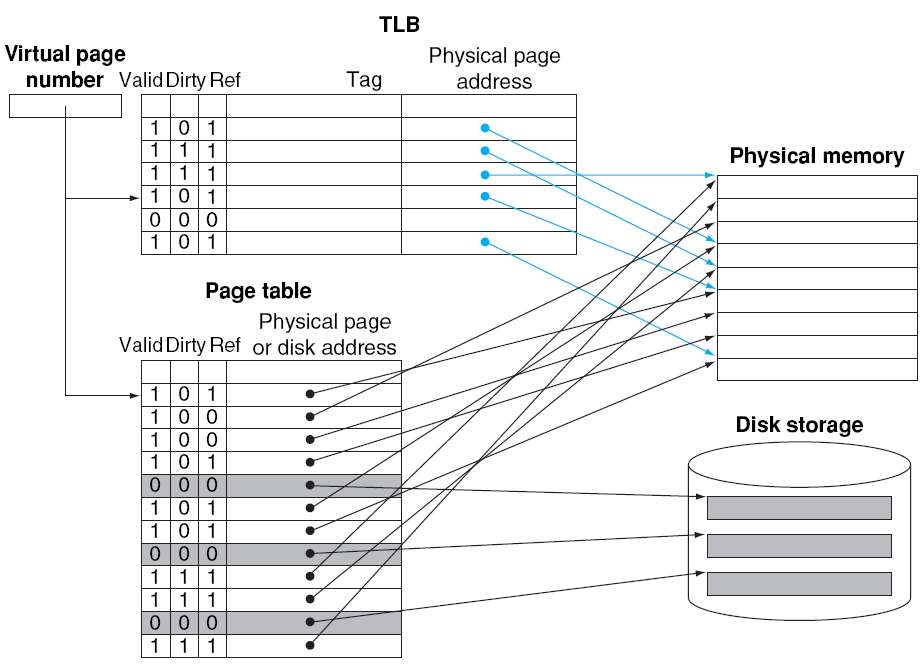

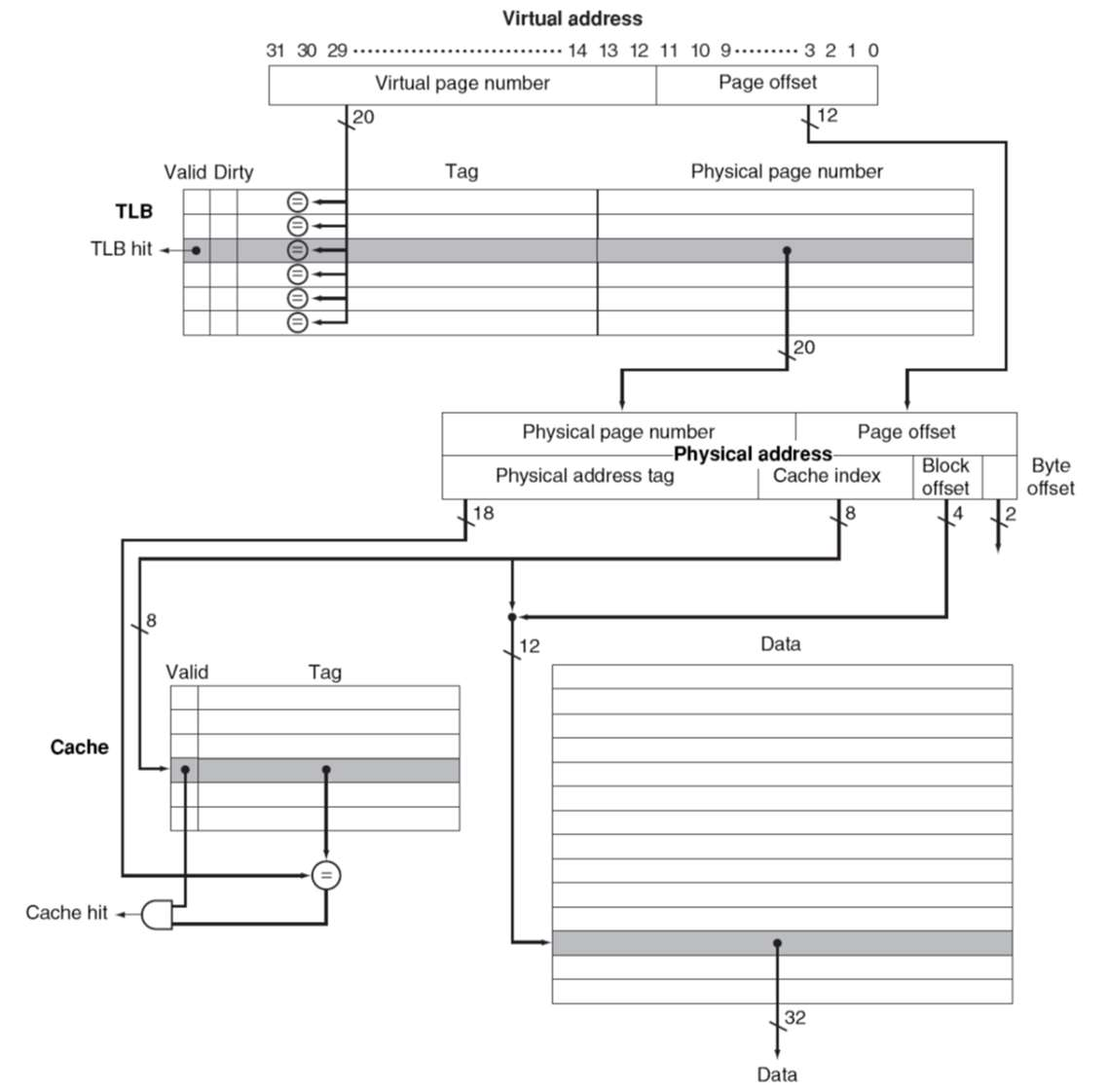

translation look aside buffer TLB

페이징 기법에 의거해서 보면 어떤 CPU가 특정 주소의 메모리에 접근하기 위해서는 CPU는 Virtual address를 가지고 있어도, 실제로는 Physical이 필요함

CPU가 일단 Virtual address 를 가지고 페이지 테이블에 접근해야함

하지만 이 접근과정이 overhead가 되고 시간낭비가 될 수 있음.

TLB에 Key Value 가 있고 hit가 발생하면 table 에 안가고 바로 physical로 가버린다. 이러면 Table에 가서 생기는 불필요한 Overhead를 줄일 수 있다.

miss가 난다면 어쩔 수 없이 메모리에 page table에 가야한다.

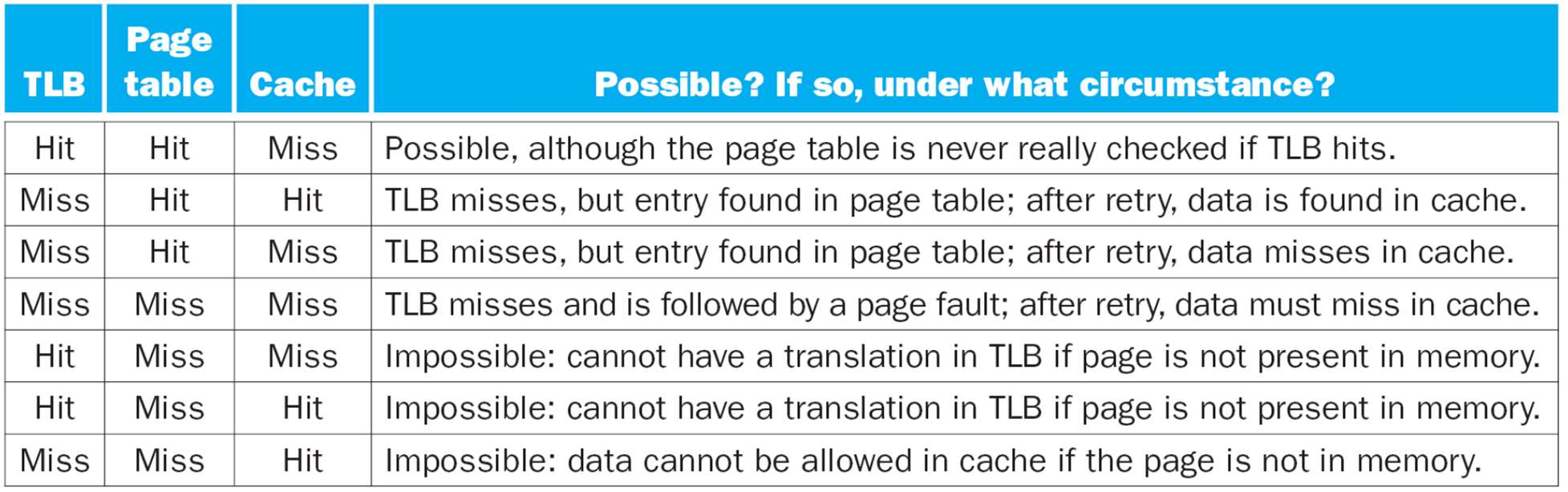

On TLB Misses

if page is in memory:

- load the pte from memory and retry

- could be handled in hw

- or in sw

if page is not in memory(page fault)

페이지 테이블에도 없는경우

- 페이지가 물리메모리에 할당이 안되어있는경우

해당 페이지를 스토리지로부터 찾아서 물리프레임에 할당해야함(운영체제)

Page Fault Handler

- TLB Miss indicates

- locate page on disk

- choose page to replace

- if dirty, write to disk first

- read page into mem and update page table

- make process runnable again

- restart from faulting instruction

(cpu에서는 stall로 멈춤)

- restart from faulting instruction

Paging protection and sharing

Protection - 보호는 각 페이지 기반으로 구체적이다.

Sharing - 같은 프레임에 매핑된 다른 프로세스의 페이지들에 의해 일어난다.

Virtual Memory Perfomance

virtual memory를 쓰면 장점이 있긴 하지만 프로그램이 다 올라오는게 아니라 실행하다보면 페이지가 없는 page fault가 발생할 수있음

--> Storage I/O가 필요한 연산이라 더 심각한 성능적 문제를 야기할 수 있음

--> 페이지폴트 발생자체를 줄이는게 가장 성능향상에 도움이 된다

페이지폴트를 줄이기 위해서는 Hit를 많이 내야한다

hit를 많이 내려면 pte를 잘 관리해야한다

Second Chance Algorithm

1 과 0으로 참조가 얼마다 되었는지 구분하는 알고리즘

LRU근사치가 나옴

1비트만 가지고 LRU와 비슷한 성능을 낼 수 있음

Referecen비트를 가지고 유사한 구현을 하는 것

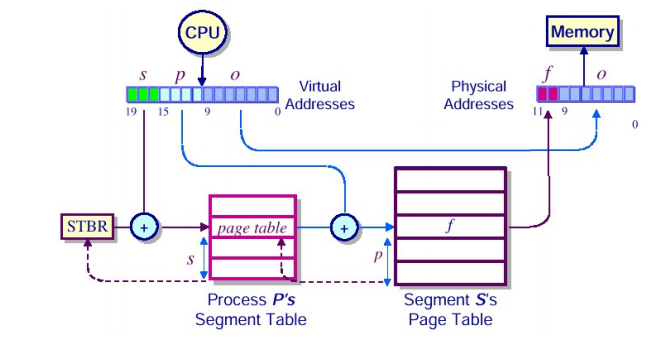

Segmentataion with paging

세그먼트를 배정하고, 세그먼트 넘버를 준다. 그리고 각 세그먼트별로 페이지 테이블을 관리한다. (세그먼트에는 각 페이지 테이블의 base address가 있음)

SPO로 구성

S 세그먼트 3비트면 세그먼트 테이블은 2^3 8개

P 1개의 세그먼트당 2^6승 개의 테이블

O 1024 byte의 페이지 크기

base는 세그먼트를 가르키는 주소만 가지고 있음

여기에 세그먼트 넘버를 더해서 세그먼트 위치를 찾음

세그먼트 안에는 페이지 테이블의 베이스 주소

그리고 뒤에 P 주소로 페이지 넘버로 페이지 테이블을 찾는다

그리고 그 페이지에서 O를 이용해 실제 피지컬 메모리의 주소를 찾아낸다

동일한 세그먼트 영역에서는 동일한 세그먼트 테이블을 사용하게 만들면 페이지테이블에 대한중복낭비를 감소시킬 수 있다.

Memory의 전체적 작동 구조

TLB --> 페이지 테이블에 대한

1) HIT의 경우 바로 메모리에 접근

2) MISS의 경우 페이지 테이블을 찾아감

(페이지 테이블 베이스 어드레스는 특정 레지스터에 적혀있음)

이 레지스터로부터 페이지테이블에 대한 정보를 얻음

페이지 테이블이 있으면 거기서 디스크를 감

실제 데이터에 접근할떄는 cache를 먼저 간다

Cache는 Direct Mapped, n-way set, fully set 3가지 사용. 캐시에 있으면 있는거고 없으면 기존의 접근 방식 사용한다.