Phase Locked Loop : 위상 고정 루프

Clock이 사용되는 거의 모든 회로(XTAL의 주파수 이외)에서 사용된다. XTAL의 출력은 정밀하고 노이즈가 적지만, 보통 높은 주파수를 만들지는 못한다.

PLL은 XTAL을 Reference freqeuncy로 사용하여 1배의 주파수부터 다양한 주파수의 clock을 만들어낸다. 물론 XTAL 외에 다른 PLL의 출력을 Reference로 하는 경우도 있다.

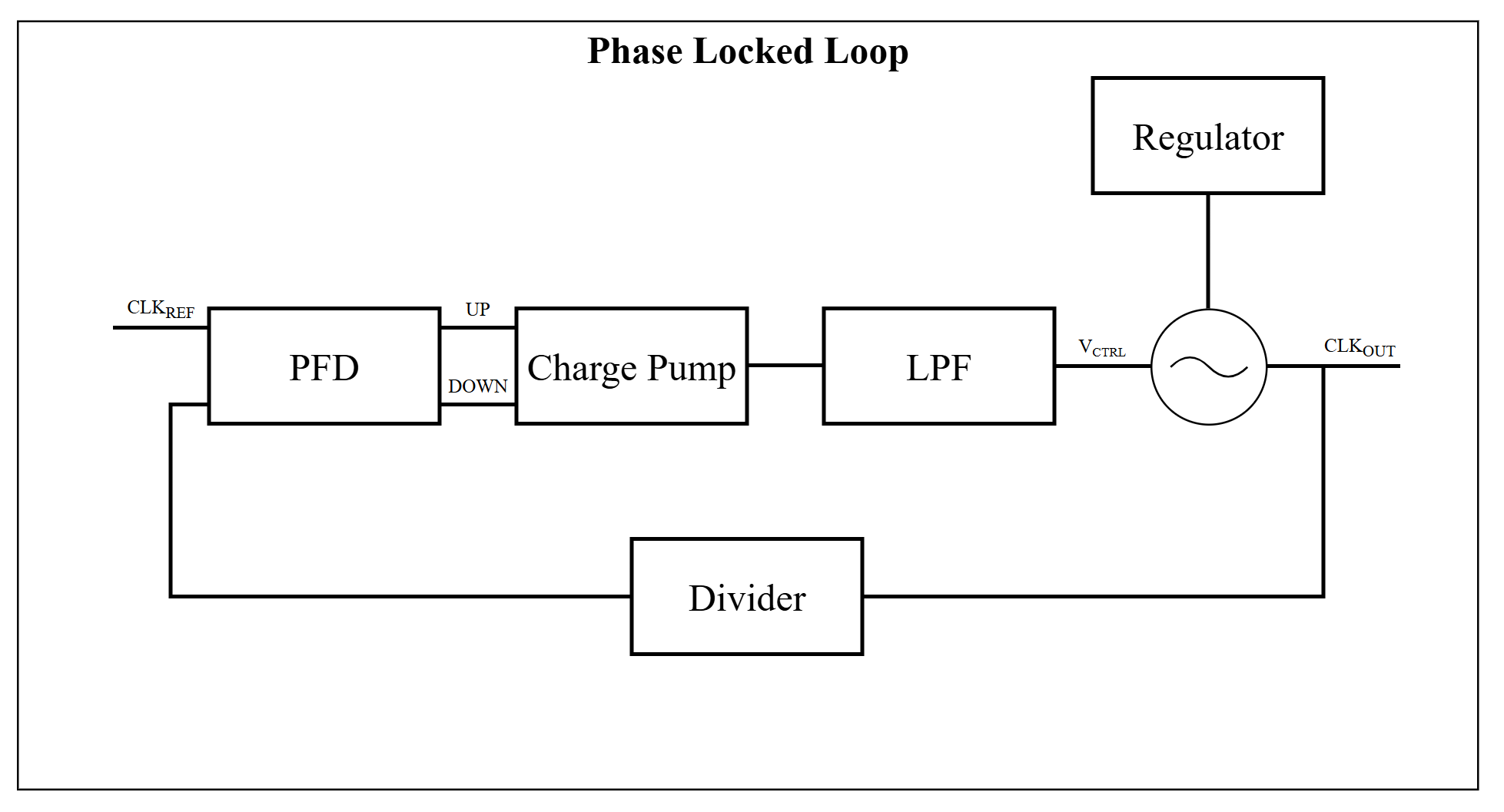

PLL 중 대부분을 차지하는 가장 대표적인 구조의 Charge Pump PLL의 구성은 다음과 같다.

Reference clock과 VCO의 출력 clock(Divider를 거친)의 위상을 비교하는 PFD(Phase Frequency Detector), PFD로부터 출력되는 위상 정보를 통해 전류를 Sourcing/Sinking 하는 Charge Pump, 이 전류를 전압으로 변환하는 Low-Pass Filter, 이 전압을 입력받아 Clock을 생성하는 VCO, VCO의 High-Frequency Clock을 Reference Clock으로 나눠주는 Divider로 구성된다. 이 때 VCO에 안정적인 전원을 공급하는 Regulator가 추가될 수 있다.