PLL / DLL / CDR / SerDes

1.Phase Locked Loop

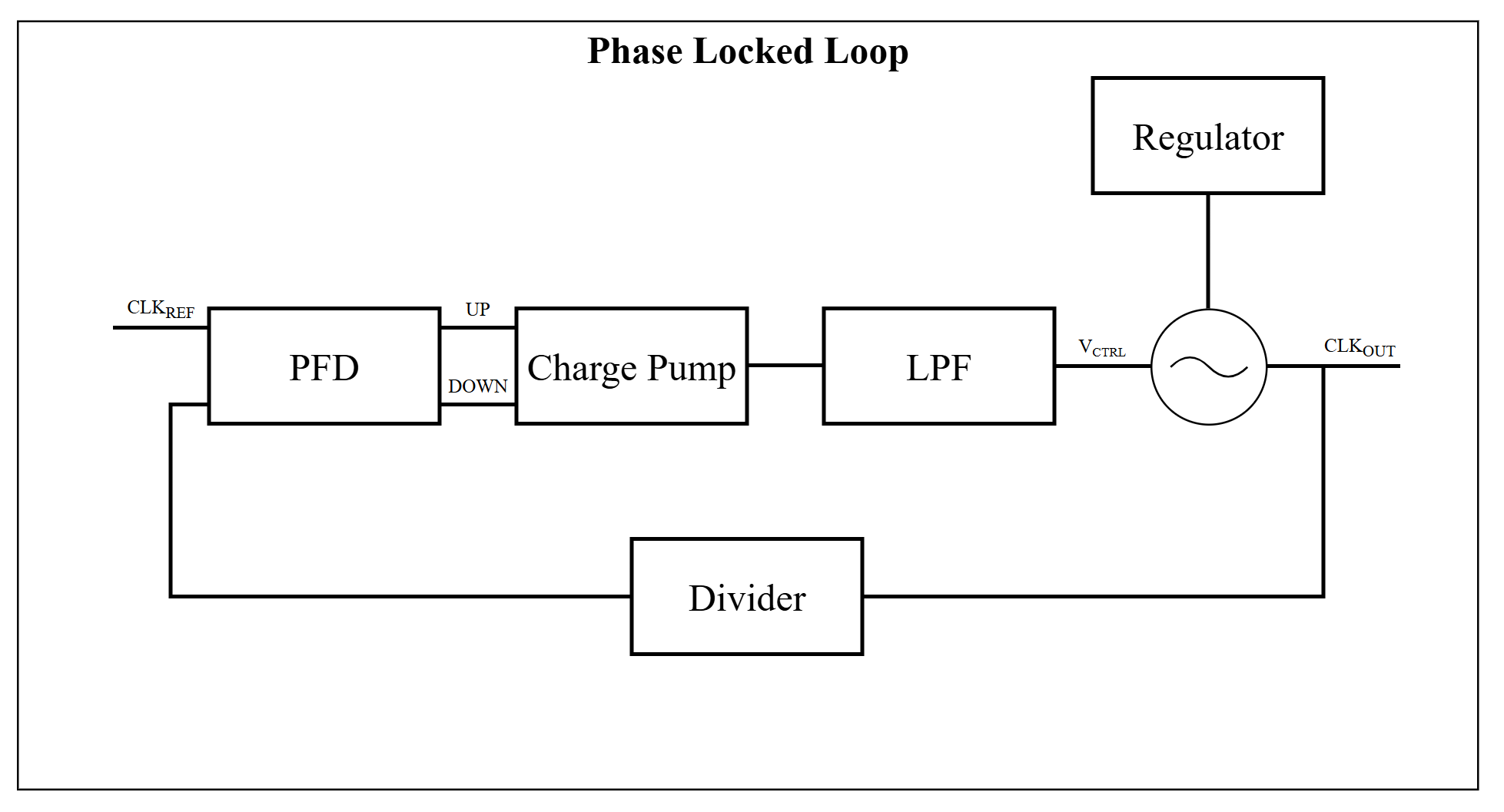

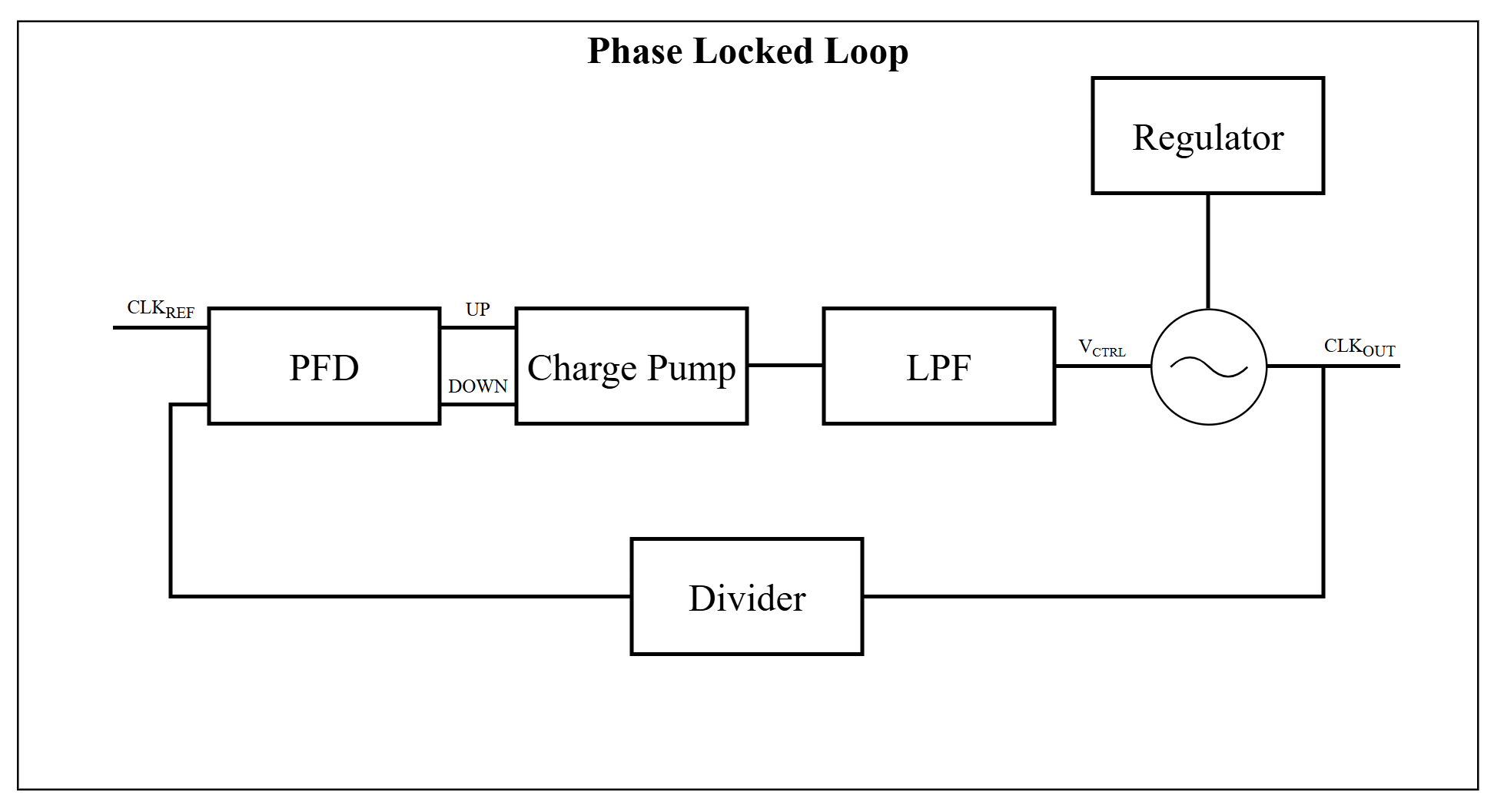

Clock이 사용되는 거의 모든 회로(XTAL의 주파수 이외)에서 사용된다. XTAL의 출력은 정밀하고 노이즈가 적지만, 보통 높은 주파수를 만들지는 못한다. PLL은 XTAL을 Reference freqeuncy로 사용하여 1배의 주파수부터 다양한 주파수의 clock

2025년 8월 23일

2.PLL Design - 1. Specification

우선, PLL을 실제로 설계하기 전, 스펙을 결정하였다. 기본적인 회로 설계 경험과 더불어 Clocking 회로와 CDR 등의 Interface에 대해 학습하는 것을 목표로 선정하였다. 전에 해본 회로 설계 경험으로는 간단한 2-Stage OP Amp, Folded C

2025년 8월 23일

3.PLL Design - 2. PFD 설계

PLL 성능에 큰 영향을 미치지 않고 간단한 PFD, Divider를 먼저 설계하였다. 내가 이번에 사용한 PFD의 구조는 기본적인 구조의 PFD로, 다음과 같다. 내가 사용할 Charge Pump는 UP, DOWN 신호 외에도 UPB, DOWNB이 필요하기 때문에 Inverter를 사용하고, Charge Pump에서 신호 간 Delay로 인한 특성 ...

2025년 8월 24일

4.PLL Design 3. Divider 설계

PFD 설계에 이어 간단한 Divider를 설계하였다. 앞서 정한 것처럼 이번에 만들 PLL은 25MHz reference clock을 통해 1.25GHz의 VCO clock을 생성한다.이 때 VCO의 clock과 reference clock의 phase를 비교해야 하

2025년 8월 27일