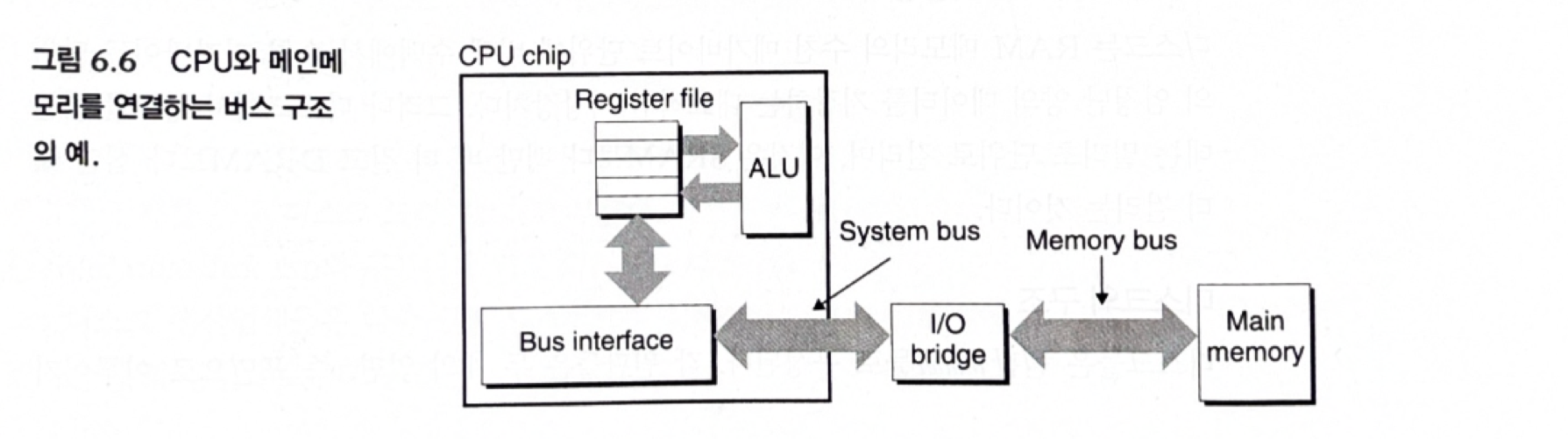

이번에는 CPU가 메모리를 다루는 실제 과정을 확인해보자

CPU와 메인 메모리(DRAM)은 직접 연결 X

→ 데이터를 주고 받기 위해서는 반드시 버스(BUS)라는 전기적 통신 회로를 통해야 함 !

🚐 BUS : CPU, 메모리, I/O 장치들이 데이터를 주고 받는 공용 통로

주소 버스(Address Bus) : 어디에 접근할 지 주소 전달

데이터 버스(Data Bus) : 실제 데이터 주고 받음

제어 버스(Control Bus) : 읽기/쓰기 등 동작 지시

CPU ↔️ BUS ↔️ I/O Bridge ↔️ Memory BUS ↔️ DRAM

→ 메모리에 접근하려면 최소 세 단계를 거쳐야 함

📌 이 과정이 중요한 이유 🔥

CPU 입장에서 메모리는 "무한한 저장 공간" 처럼 보이지만 실제로는 I/O 브릿지, 버스, 트랜잭션 회로, DRAM을 거치는 복잡한 전기 신호 흐름이 존재함

이게 느리기 때문에 !! → 캐시 메모리(SRAM)이 필요한거고

이 흐름을 이해해야 → 메모리 병목이나 속도 저하원인을 파악할 수 있다 !