There are major hurdles of Pipelining. In this post, I will cover this major problems and solutions.

Hazard

This hazard situation is occured when the next instruction cannot be executed in the following clock cycle.

Structural Hazard

- Hardware cannot support combination of instruction.

- The instruction and data should be separated. Because we cannot fetched from the memory at the same time

Solution about Structure Hazard

- Separate Instruction Memory and Data Memory by using Cache

- Time-multiplexed or Multi-port register file for register file access conflict

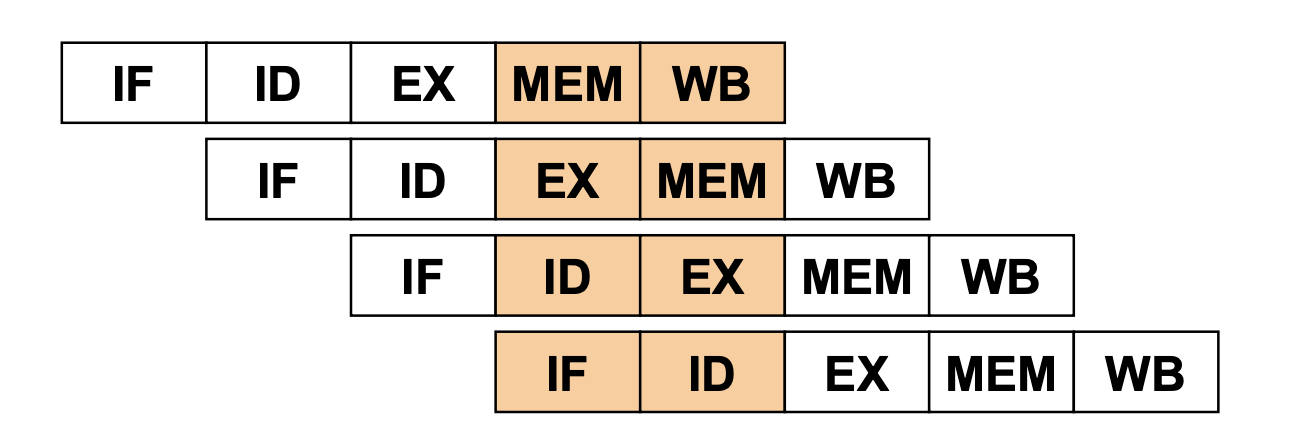

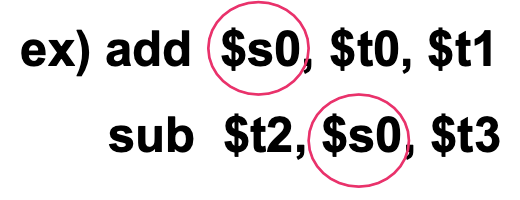

Data Hazard

-

An instruction depends on the results of a previous instruction still in pipeline.

-

For example, if we have these instructions, $s0 register cannot be used in sub instruction.

-

Problem with starting next instruction before first is finished.

Solution about Data Hazard

We can solve the data hazard by using these methods.

Freezing

- We can stall other instructions until previous instruction executed.

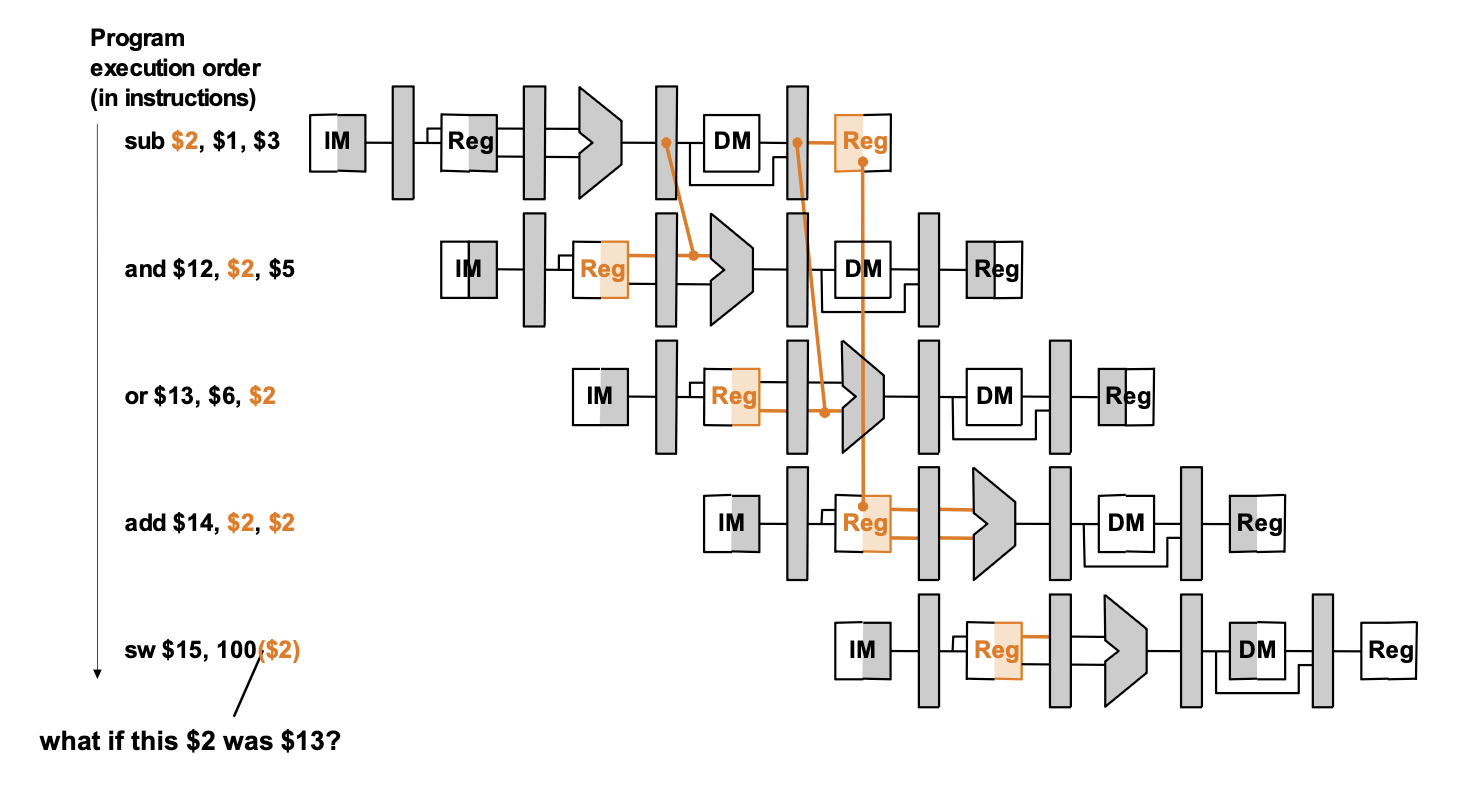

Forwarding

- We can create the path to send the result of instruction or calculation.

Compiler

- If our compiler can detect and predict some hazard, then it can prevent some hazard.

Control Hazard

- Control may be transferred to another instruction based on the results of an instruction.

- It is related with Branch, Jump instruction.

- This control hazard can be resolved by waiting. (stall)

- To detect hazard, we have to use pipeline control unit.

We have to decide what actions we take. In this section, we will suppose that branch is not occured. So, we should make some architecture to flush when actually branch is ouccred.

Solution about Control Hazard

These are the solutions about control hazard. If we stall, we can solve the control hazard problems.

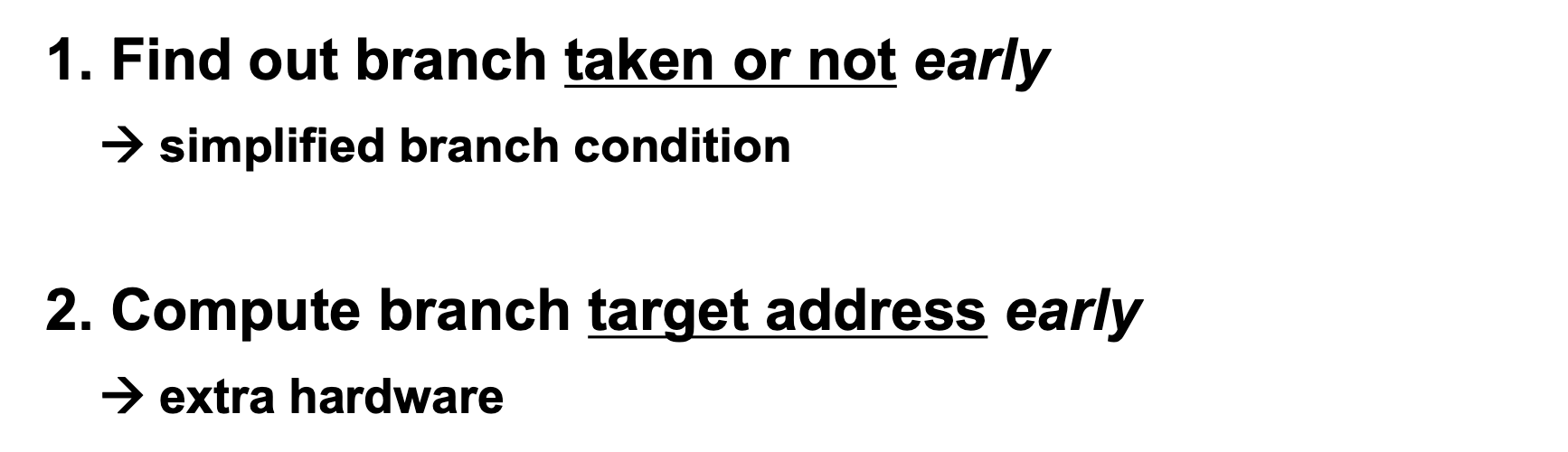

We can optimized branch processing. However, there are two conditions.

- Find out branch taken or not early.

-> If we use them, we can simplified branch condition. - Compute branch target address early

-> We have to create extra hardware.

We can reducing delay by moving branch execution to the ID stage. By using it, we can reduce the delay percent.

Branch Prediction

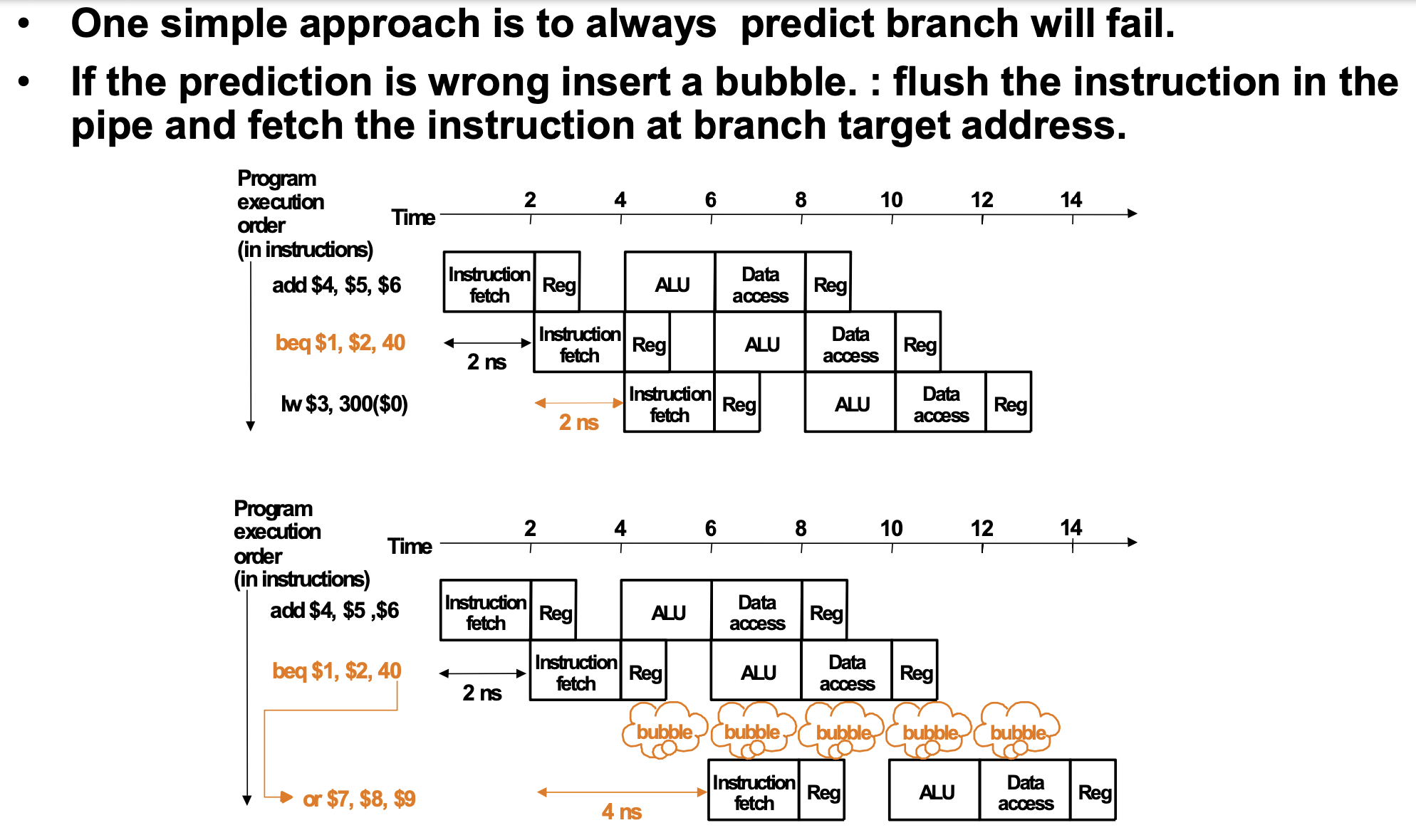

We can suppose that prediction always will be failed. If the prediction is wrong, then we must insert a bubble.

Static Branch Prediction

In the static branch prediction, we can choose three cases.

1. Never Branch

Assume that the branch never take place.

2. Always Branch

Assume that the branch always take place.

3. Predict by op-code

Decision is made based on the opcode.

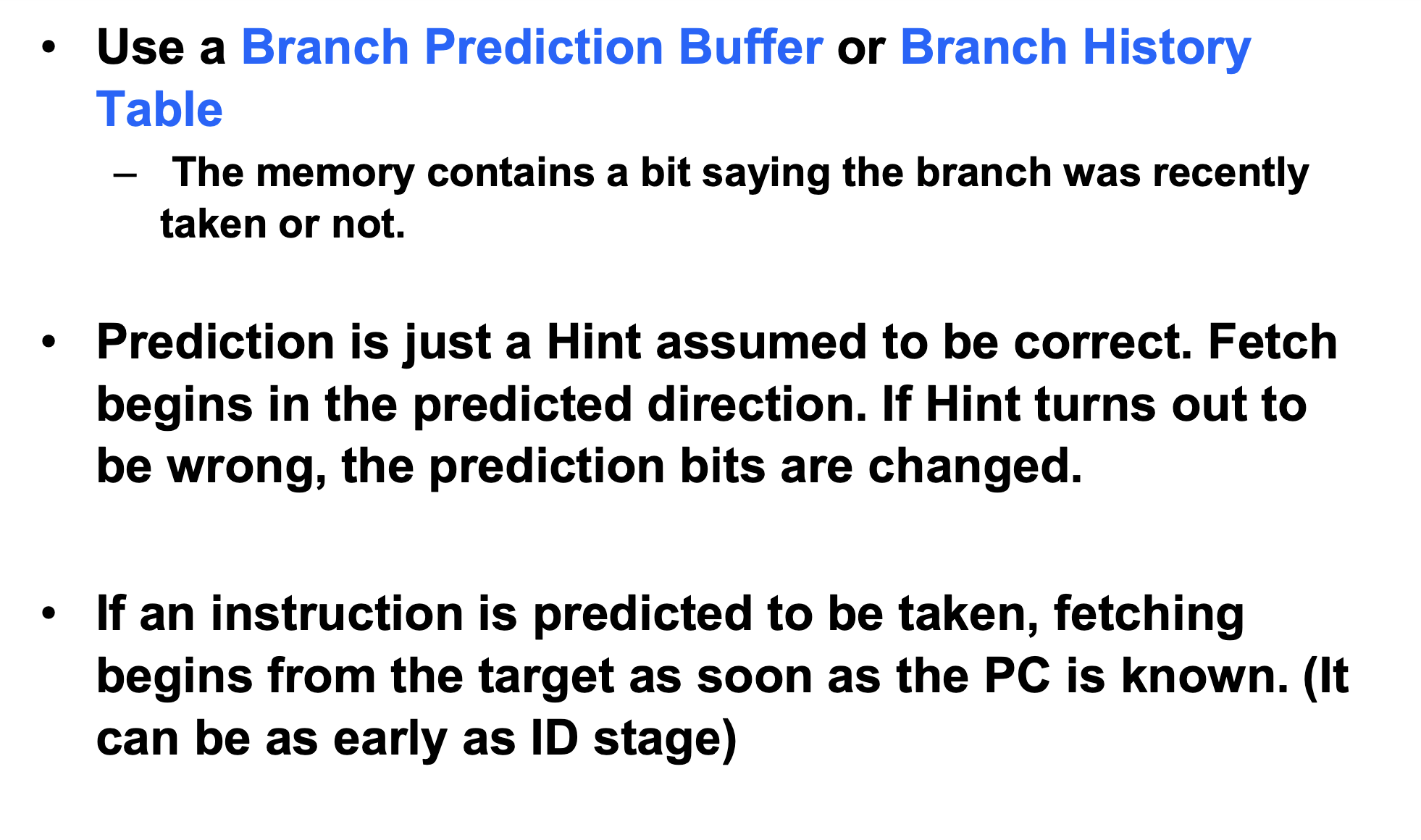

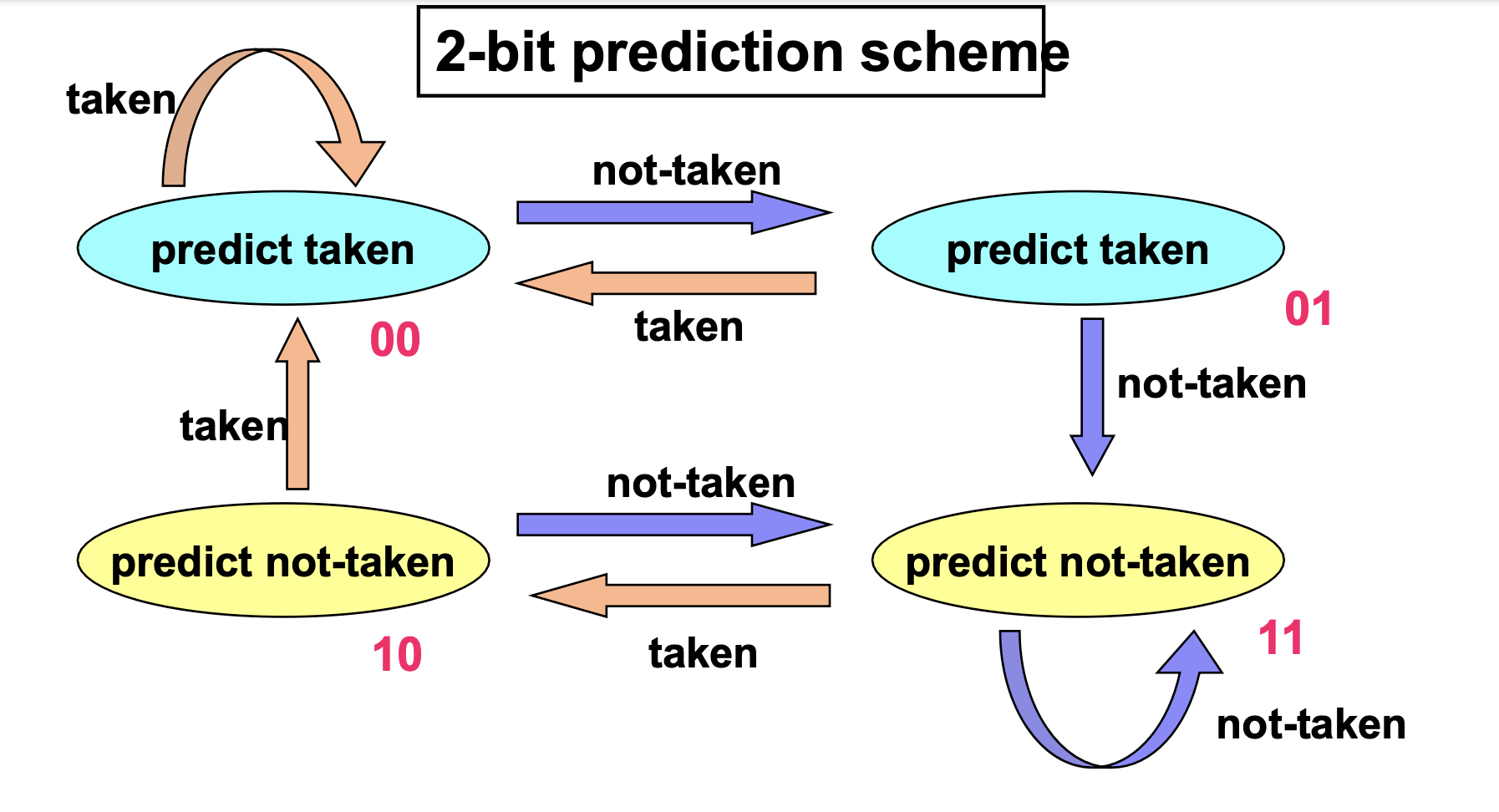

Dynamic Branch Prediction

We can use the space to remember the state of branch prediction. By using this other memory, we can make decision more easily.

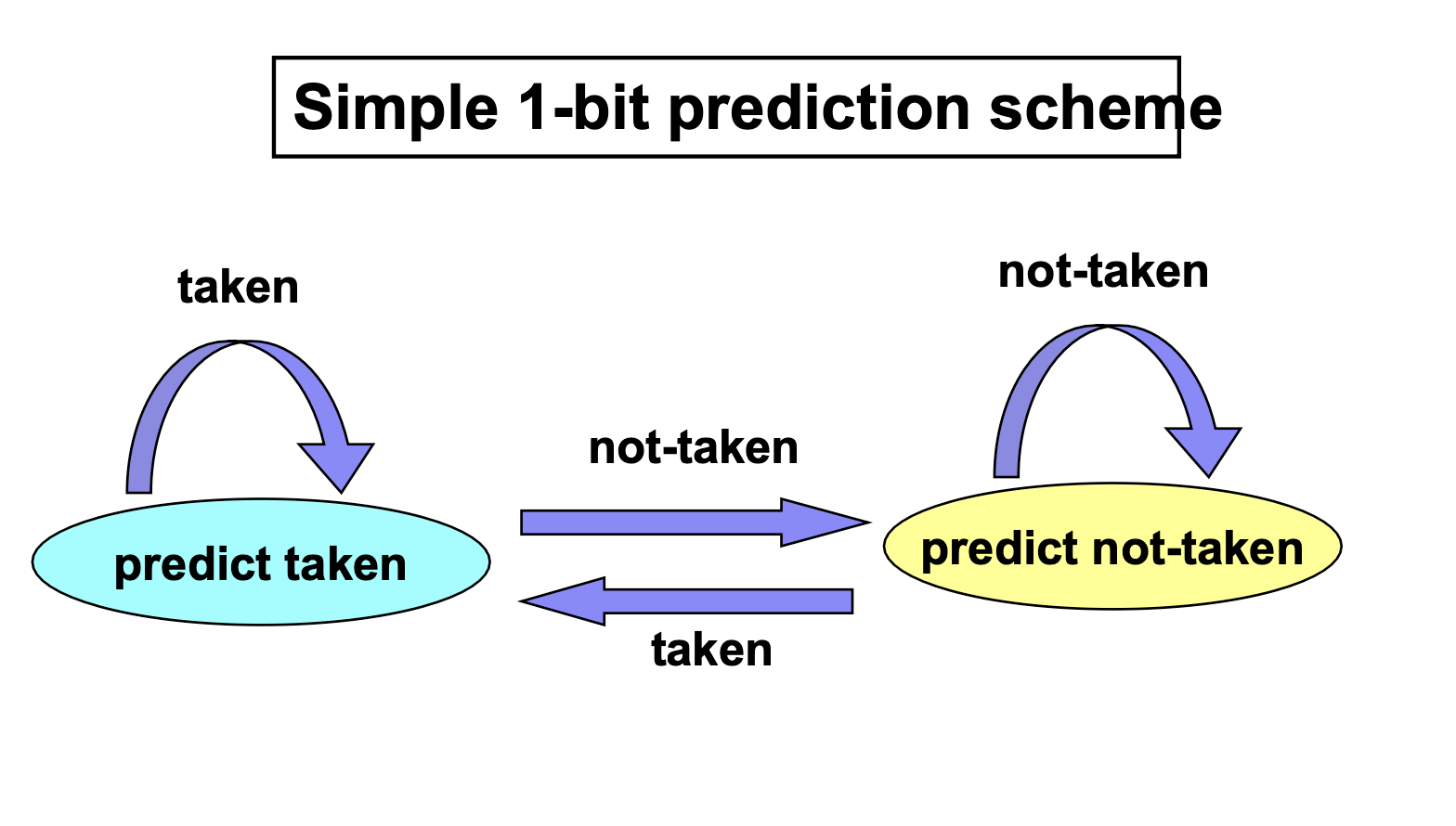

This is a example about the dynamic branch prediction. We can keep the state of prediction.

If we use more memory slot, then we can use 2 bits to keep the state.