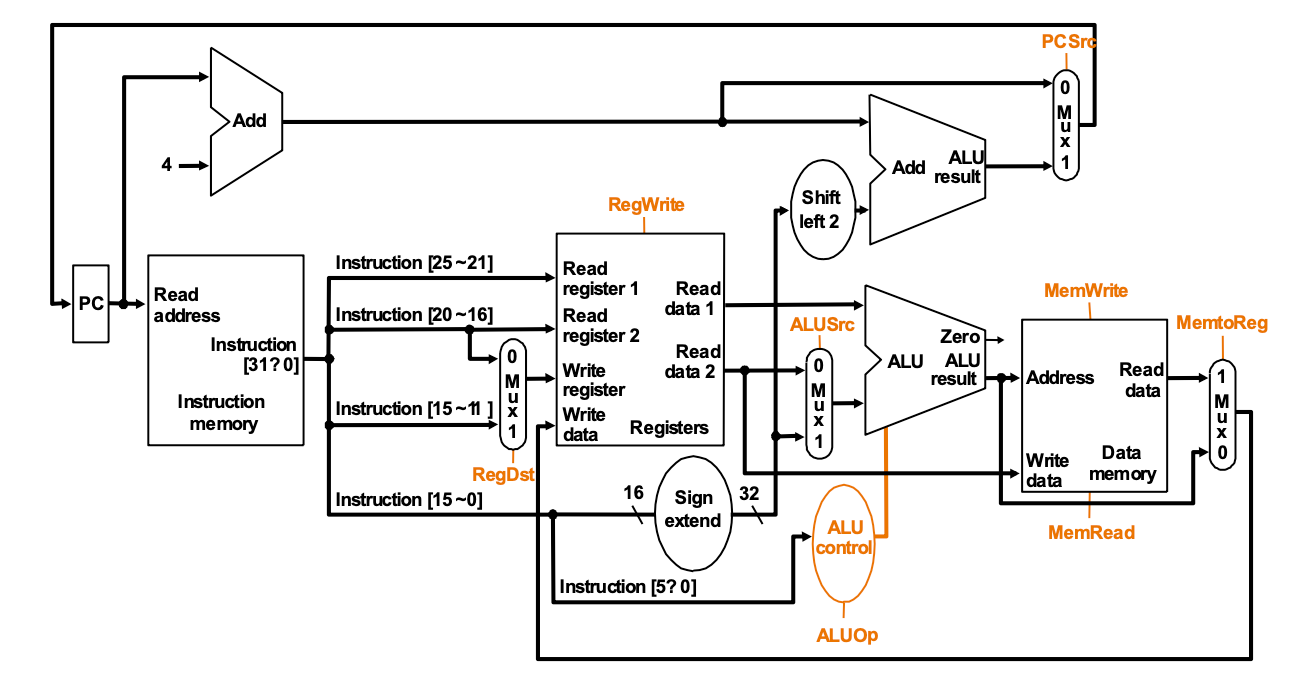

In this post, I will upload the Implementation of Single Clock Cycle.

In the MIPS Architecture, there are 3 types of instructions.

- R-type Instruction

- I-type Instruction

- J-type Instruction

R-type instruction has three register sections and each of them has 5 bits. However, I-type and J-type(In this post, I suppose that is branch instruction) has only two register sections and each of them has 5 bits.

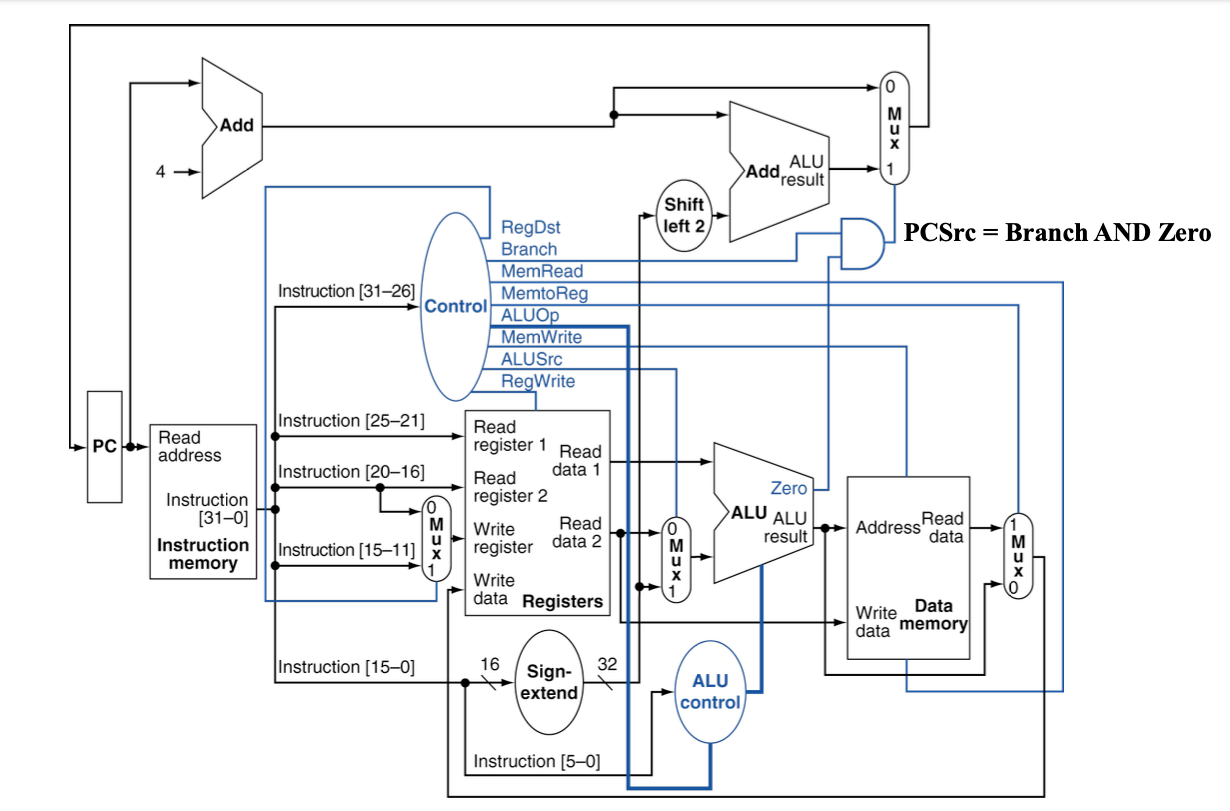

So, We have to deal all of the instructions. For that reason, MIPS create their architecture like that.

If some instruction is petched, then we should check up the type of instruction. If the instructio's type is R, then this architecture uses three read registers. On the other hand, the MUX that in front of the register box selected 1 that means it doesn't use more register. So, MIPS automatically use sign extention and use constant.

In addition, the second MUX recieved different value. If the instruction is R-type, then it recieved the read data, however it is not, then it recieved the constant with sign extention.

In the next, ALU unit calculated the result of the instruction and finally, last MUX recieved the value that can be evaluated result or other data.

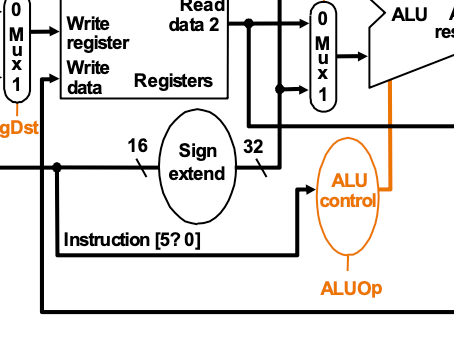

However, there is an essential point that decide what action to take.

In this picture, there is a part of ALU control. By using the function code in the instruction, it can decide what action to take.

More generally, it has to deal about opcode section. Because the instruction of I-type and J-type doesn't have function code section. So, it must be supplied opcode and function code sections.

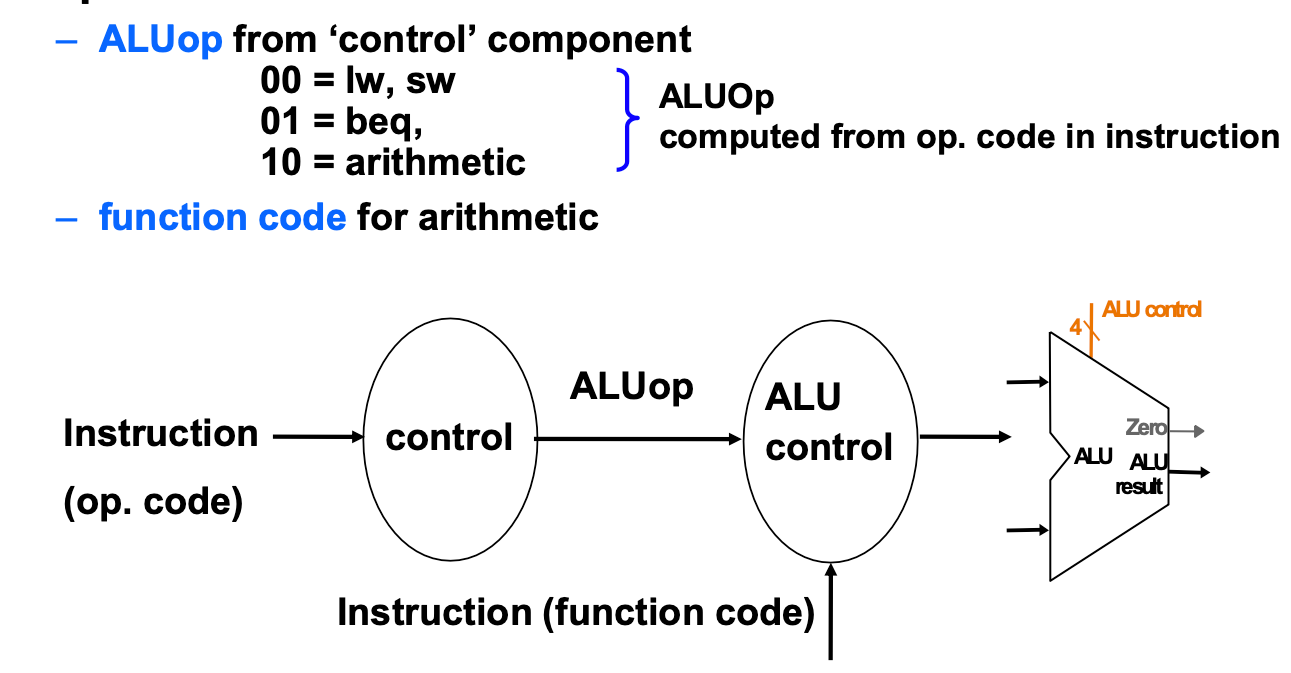

This picture can explain about that.

In addition, there are many control signals that decide what value is used.

This is the full structure of Single Clock Cycle architecture. In this picture, the value of ALU Opcode supplied to ALU control unit.

Structure of Single Cycle Control

All of the logic is combinational(excepted PC and general purpose registers).

If we use this structure, there might be a delay. Because ALU might not produce right answer right away. In addition, we use write signals along with clock to determine when to write.

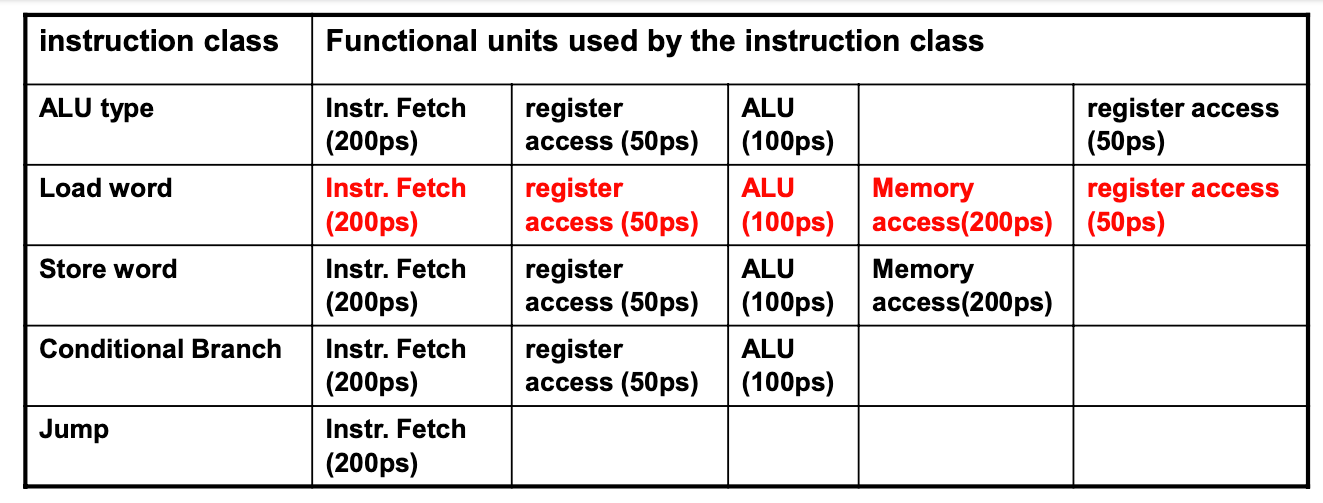

For that reasons, this structure must accpete the length of the longest path(Critical Path).

This is the general executed time about instruction. Load word instruction is the longest instruction among them.

Problems

There are some instructions about floating point. Floating point instructions are more difficult rather than other instructions. It means that instruction's executed time is more longer.

In addition, this architecture uses duplicated units like adder. It is result in the waste of chip area.

Solution

There is a solution about this problems.

- Make cycle time smaller

- different instructions take different numbers of cycles

-> Using a multicycle datapath