LinkedIn Yuzo Fukuzaki 페이지: #3D_V #Ryzen #AMD

AMD의 3D V 캐시의 구현 방법에 대한 설명 - 컴퓨터 / 하드웨어 - 기글하드웨어 (gigglehd.com)

요약

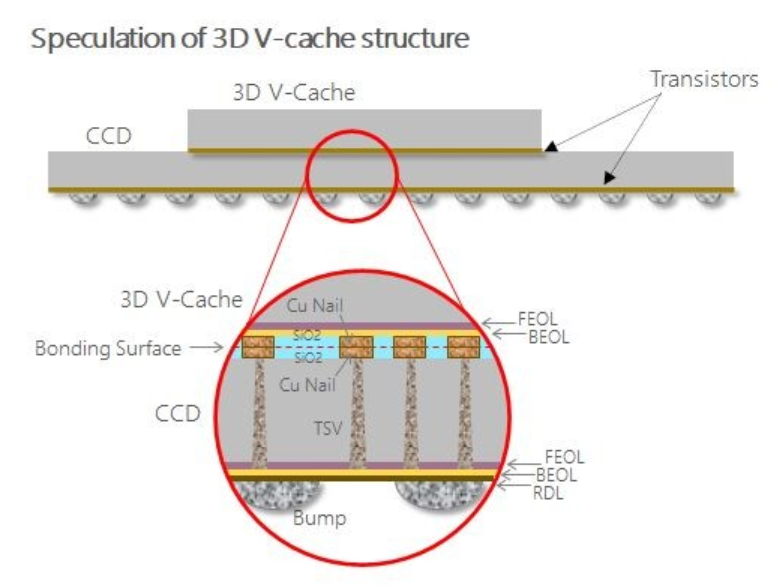

- 테크인사이트의 수석 테크놀러지 펠로우인 유조 후쿠자키가 AMD의 3D VCache 적층에 대해 설명함.

- CCD(CPU Core Complex Die) 위에 LLC를 적층하는 방법을 3D VCache라고 부름.

- AMD는 Zen3 CCD 위에 3D VCache를 올려 총 192MB의 L3 cache를 만듦.

- 이때, 3D VCache가 L4 cache 역할을 하는 게 아니라, 연속된 L3 cache로서 동작함.

- 3D VCache는 CCD와 동일한 공정으로 만들며 CCD 영역 위에 위치해 TSV로 연결됨.

의견

Memory의 성능을 올리기 위해 이제는 물리적인 거리를 극단적으로 최소화하는 패키지 기술이 등장하고 있습니다. AMD의 3D VCache는 CPU 위에 SRAM을 올리고 TSV로 연결해 RC delay와 병목현상을 최소화합니다.

CPU의 성능을 올리기 위해서는 cache와 brance prediction/speculation의 성능을 올려야합니다. 문제는 두 방법 모두 면적(area)이 많이 필요합니다. Area가 증가하면 양산 수율은 큰 폭으로 떨어지기 때문에 어떻게든 수율을 유지한 체로 성능을 올려야했고 가장 좋은 방법으로 CPU 위에 cache를 적층하는 방법을 사용합니다.

결과적으로 수율 확보와 성능 상승을 위한 방법입니다. 이로써 모든 memory(SRAM, DRAM, NAND)는 3D 적층구조를 선택하게 됩니다.