- 본 문서에서는 반도체 8대 공정에 대해 본격적으로 들어가기 전에 각 공정에 대한 이해를 돕고 전체 그림을 그릴 수 있도록 CMOS 반도체를 만드는 전체 공정을 구조와 함께 설명합니다.

- 올바르지 않은 내용은 언제든지 메일/댓글로 알려주시면 피드백 반영하겠습니다.

1. CMOS란?

- 예상 독자 여러분께서는

MOSFET,PMOS,NMOS,**CMOS**를 많이 들어봤지만 정확히 알고 계시지는 않으리라 생각합니다. 저 또한 그랬으니까요

-

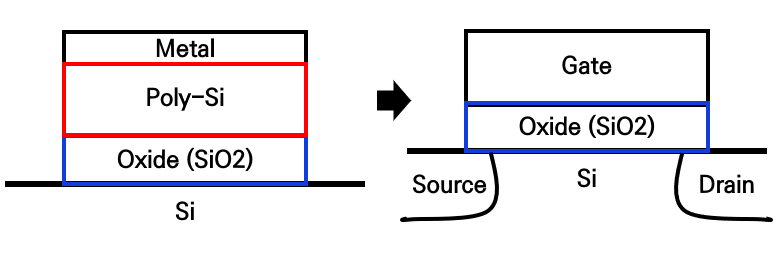

먼저 MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor)이란, 이름에서부터 유추할 수 있다시피 금속과 산화물 절연체 그리고 반도체가 층을 이루며 결합된 트랜지스터를 말합니다.

-

산화물 절연체? 트랜지스터? 정의에서 두 가지 새로운 단어가 등장하게 됩니다.

-

산화물 절연체 (Oxide)

- 물질의 구성요소중에 산소가 포함된 모든 물질을 산화물이라고 부릅니다. 우리 인체도 산화물의 일종이죠.

- 산화물 중에서 전기전도도가 매우 낮아 전기가 잘 통하지 않으면 우리는 그 물질을 산화물 절연체라고 부릅니다.

- MOSFET에 사용되는 oxide로는 실리콘 다이옥사이드 가 있습니다.

-

트랜지스터 (Transistor)

-

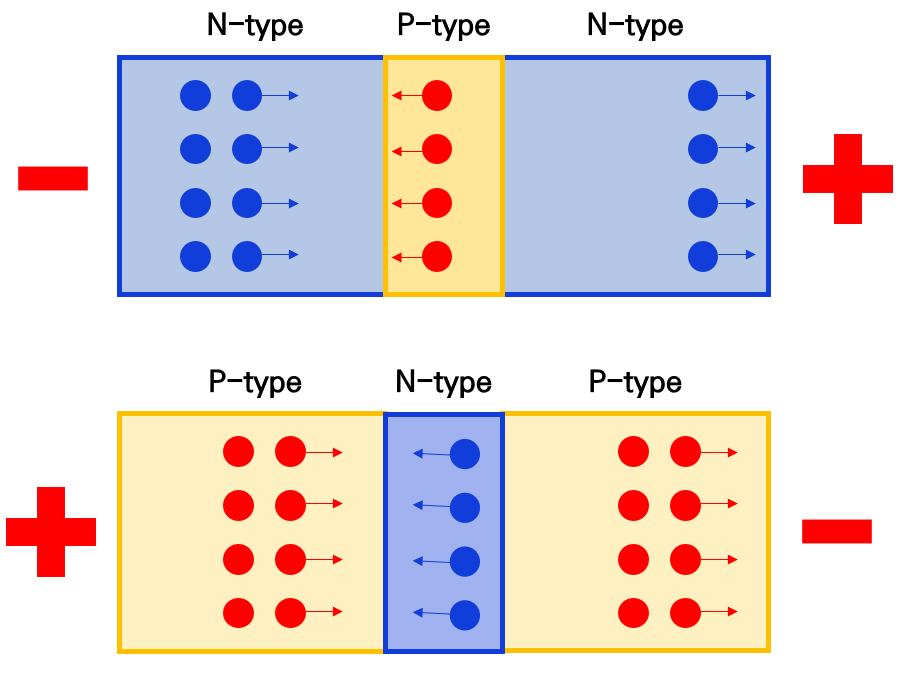

트랜지스터는 상대적으로 전자가 많이 들어있는 n-type 반도체와 적게 들어있는 p-type 반도체가 교차하는 구조로 되어있습니다. 위에 사진을 npn형 트랜지스터, 아래 사진을 pnp형 트랜지스터라고 부릅니다.

-

좌측 반도체부터 순서대로 emitter-base-collector 라고 부릅니다.

-

npn형 트랜지스터 동작원리

- N-type에 (-)극, p-type에 (+)극 순방향 전압을 인가해줍니다. P-type의 hole들은 n-type emitter 쪽으로 넘어가려고 할 것이고 반대로 n-type의 전자들은 base쪽으로 넘어오려고 할 것입니다. 그러면서 전자와 hole이 결합하면서 공핍 (depletion)영역이 줄어들면서 시계 반대 방향으로 전류가 흐릅니다.

- 하지만 base p-type 반도체가 굉장히 얇기 때문에 hole과 결합하지 못하고 남아도는 전자들은 emitter에서 collector 쪽으로 넘어갑니다. 이렇게 되면 base쪽의 전류보다 collector쪽의 전류가 훨씬 커지는 현상이 발생합니다.

- 반대로 collector 쪽 n-type에 (+)극, base p-type에 (-)극 역방향 전압을 인가해줍니다. 이럴 경우, p-type의 hole들과 n-type의 전자들은 서로 다른 방향으로 이동하려고 하면서 공핍 영역은 더 넓어져 전류가 흐르기 어려운 상태가 됩니다.

- pnp형 트랜지스터의 동작원리는 부호만 반대일 뿐 똑같이 진행됩니다.

-

동작원리를 통해 알 수 있는 트랜지스터의 용도는 다음과 같습니다.

- 스위칭 기능 (Switching)

- 전원 On/Off 하듯이 스위치를 닫아 base에 전류가 흐르게 하거나 또는 흐르지 못하게 하면 전체 전류 흐름을 제어할 수 있습니다.

- 이런 기능을 트랜지스터의 스위칭 기능이라고 합니다.

- 증폭 기능 (Amplification)

- 타입에 상관없이 base에 흐르는 전류보다 collector에 흐르는 전류가 더 큽니다.

- Base 전류의 작은 변화가 collector에서는 큰 변화로 나타나는 성질을 이용하는 것을 증폭이라고 합니다.

- 스위칭 기능 (Switching)

-

-

-

MOSFET은 위에서 살펴본 Emitter-Base-Collector로 구성된 BJT 트랜지스터와 유사하게 Source-Gate-Drain으로 구성된 일종의 트랜지스터 입니다.

-

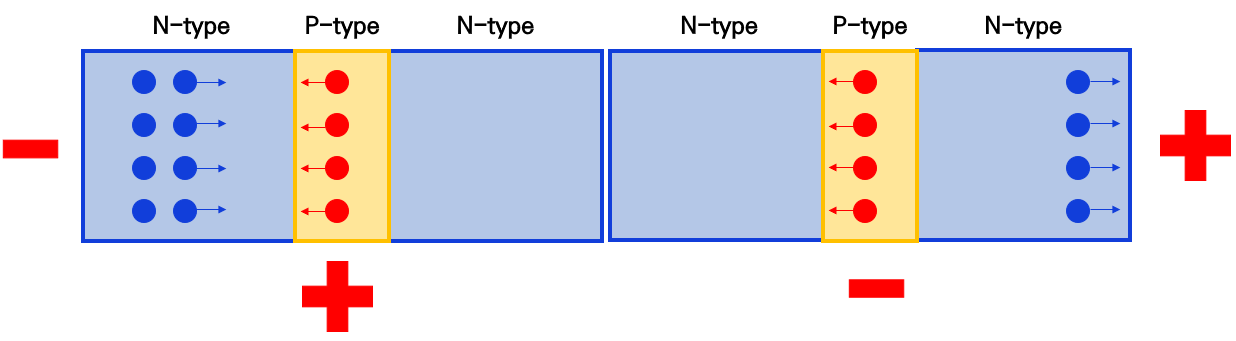

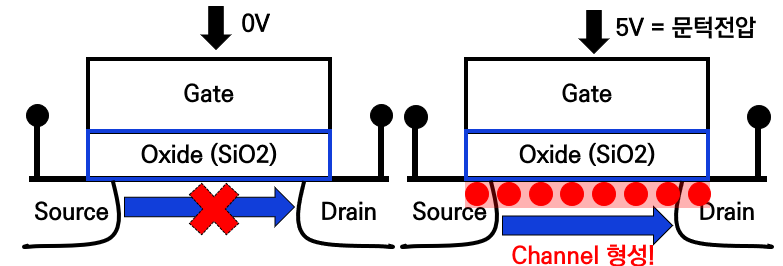

MOSFET은 어떻게 트랜지스터 역할을 수행할 수 있을까요? 바로 gate에 인가되는 전압이 비밀의 열쇠입니다.

- Gate에 아무런 전압도 인가되지 않았을 때,

source에서drain으로 전류가 흐를 수 없습니다.Source와drain의 타입과 웨이퍼 기판의 타입이 서로 달라서 전류가 통할 수 없기 때문입니다. - 설령 전압을 인가하더라도 라는 산화물 절연체가 있기 때문에 전류가 버티고 있기 때문에 역시 전류가 통할 수 없습니다.

- 하지만 문턱전압 (Threshold Voltage)이라는 일정 기준치 이상으로 전압이 인가되면 전압의 부호에 따라

source와drain사이에 carrier (전자 또는 hole)가 쌓이면서 channel이 형성되어 이를 통해 전류가 흐르게 됩니다.

- Gate에 아무런 전압도 인가되지 않았을 때,

-

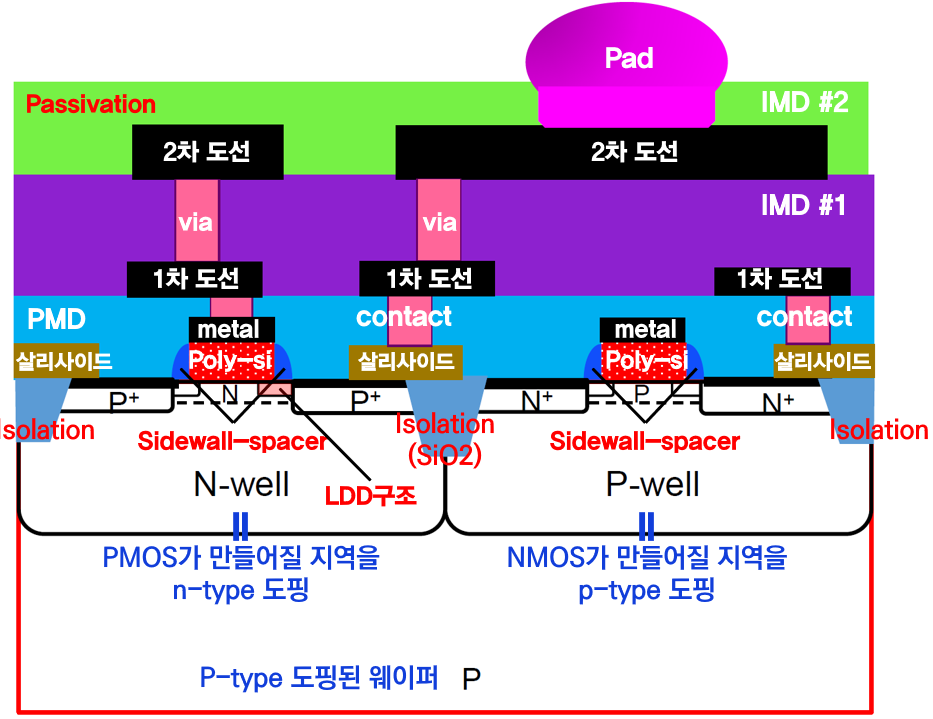

빙 돌아서 설명하느라 정신없으셨을 것 같습니다. CMOS는 이러한 MOSFET 기판이 n-type인 nMOSFET (

NMOS)과 p-type인 pMOSFET (PMOS)이 상보적으로 연결된 MOSFET을 의미합니다.

2. 왜 CMOS여야 하는가?

- 지금까지 트랜지스터와 MOSFET을 넘어 CMOS의 정의와 작동 원리에 대해서 알아봤습니다.

- 그런데 왜 현대 반도체 산업에서는 트랜지스터를 사용하지 않고 CMOS를 사용할까요? 분명 CMOS가 트랜지스터와 비교해서 우월한 점을 몇 가지 가지고 있기 때문이겠죠?

- 높은 집적도 구현이 가능합니다.

- BJT 트랜지스터보다 CMOS의 집적도가 약 50~100배 높습니다.

- NOT, NOR과 같은 기본적인 gate도 2 또는 4개의 BJT 트랜지스터가 필요하고 복잡합니다.

- 면적이 점점 작아지는 반도체의 흐름에 맞게 CMOS가 자연스럽게 BJT를 대신해서 채택될 수 밖에 없었습니다.

- 소비 전력이 매우 적습니다.

- Low level 전달 효율이 거의 100%인 nMOSFET과 high level 전달 효율이 거의 100%인 pMOSFET을 상보적으로 결합한 것이 CMOS이므로 gate 전압의 손실이 거의 없습니다.

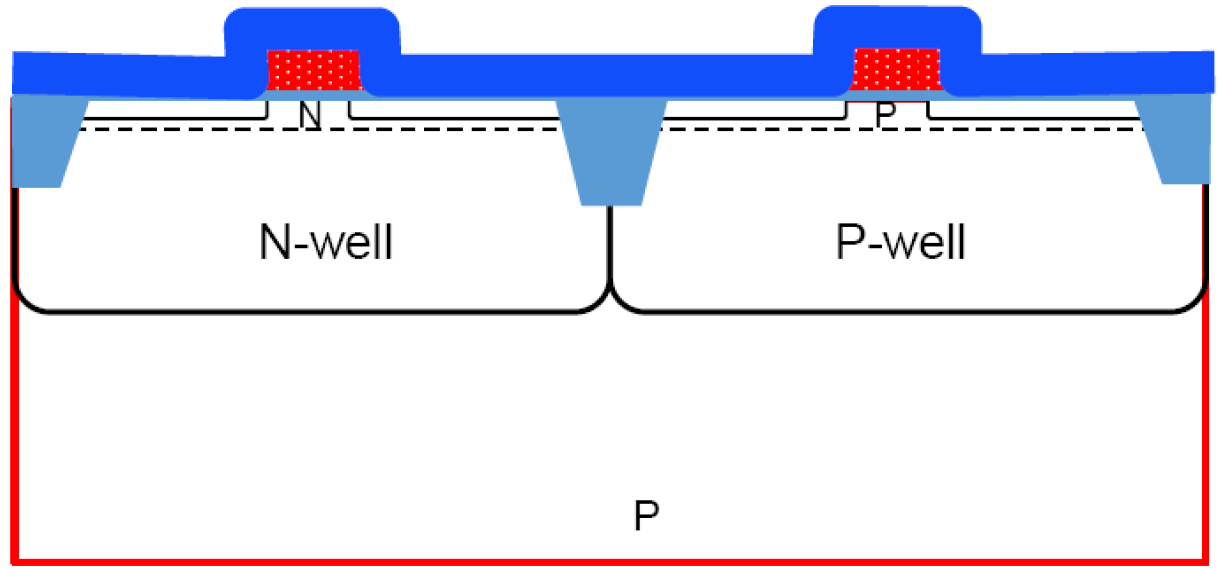

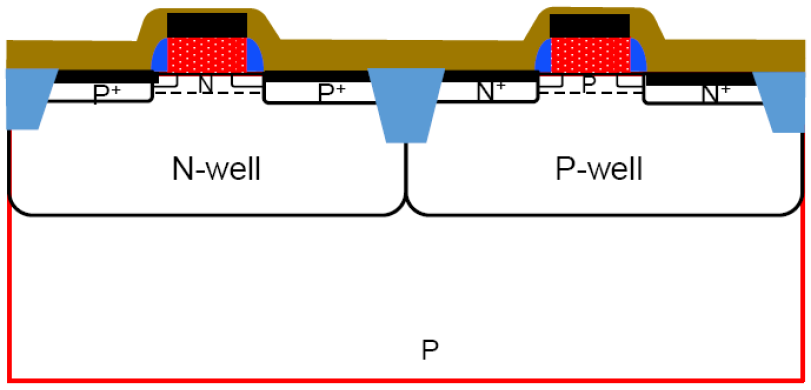

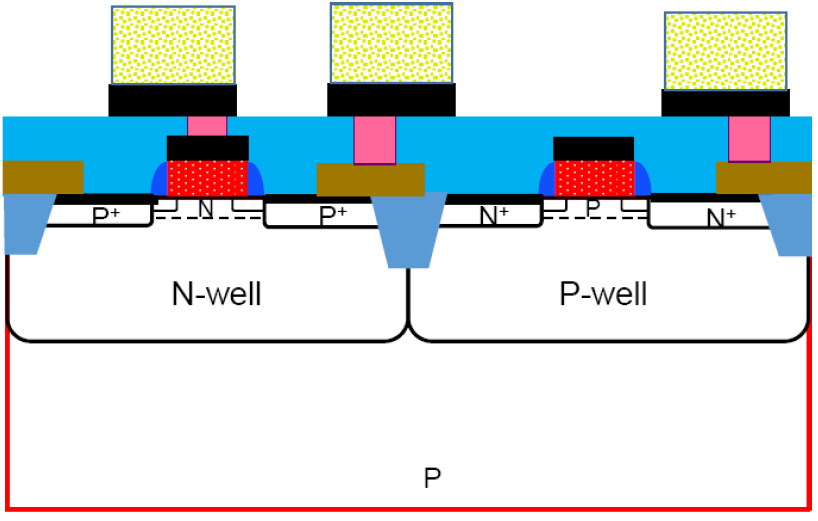

3. CMOS의 구조

- 갑작스럽게 많은 새로운 단어를 만나게 되서 당황스러우시리라는 점 충분히 이해합니다. 하지만 이 포스트를 보신 뒤에는 전부 이해하시게 될 것이니 차근차근 따라와주시기 바랍니다.

- CMOS의 구조는 위 그림과 같습니다. 설명의 편의를 위해 도선 층 (metal layer)이 두 개이고 well도 두 개인 간단한 구조를 가져왔습니다. 실제 반도체 공정에선 20층이 넘는 layer가 있고 well도 셀 수 없이 많습니다만 위 구조만 이해한다면 나머지는 반복되는 형태입니다.

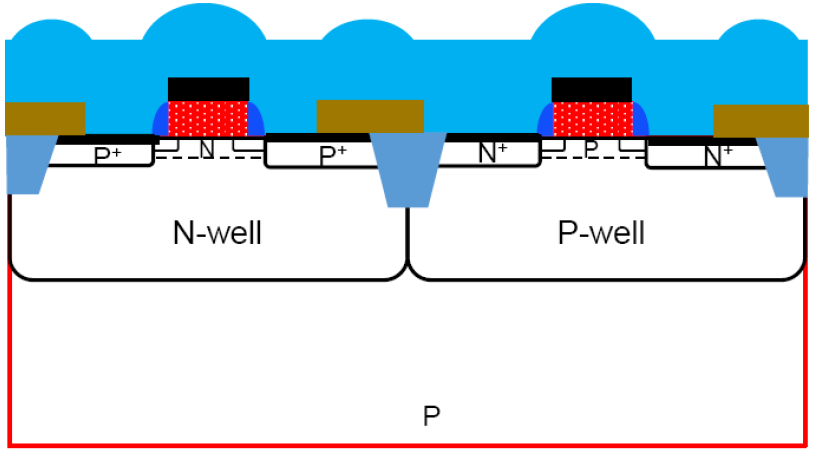

4. CMOS 제작 공정

CMOS 제작 공정을 18가지 절차로 설명합니다. 각 과정에 포함된 소과정에는 여러 생소한 단어가 포함됩니다. 처음에 배우실 때는 이게 얼마나 힘들고 난해한 단어와 절차인지 압니다. 여러분은 모르는 단어에 사로잡히지 마시고 전체 그림과 과정을 보시려고 노력하시면 되겠습니다.

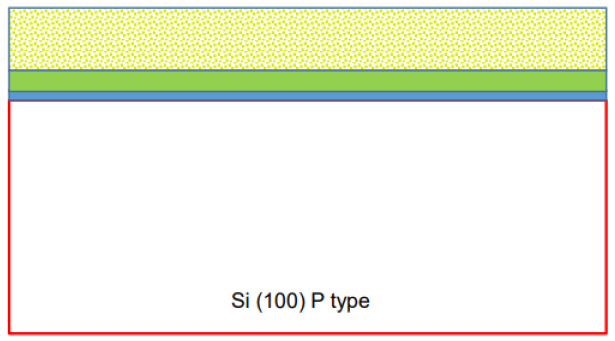

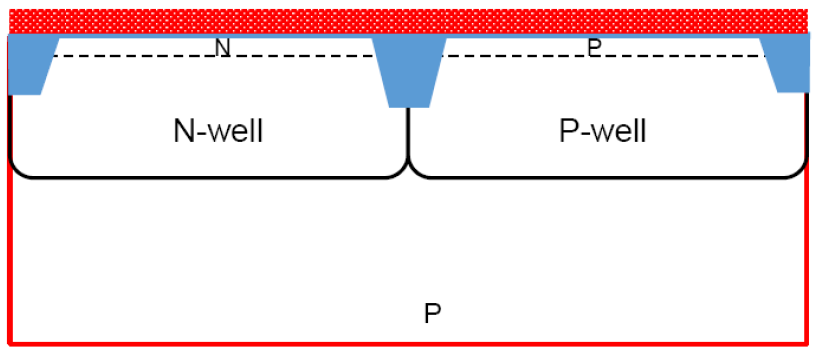

Step 1. Pad oxide 증착

- P-type으로 도핑된 wafer위를 cleaning 합니다.

(Cleaning은 추후에 하나의 큰 주제로 다룰 토픽입니다. 추후에 업로드 될 글에서 더 자세히 배우실 수 있습니다.) - Pad oxide (, 파란색 층)를 얇게 증착하고 열산화 (Thermal oxidation)처리 해서 경화합니다. ( )

- Pad Silicon Nitride (, 초록색 층,

실리콘 나이트라이드)를 LPCVD (Low Pressure Chemical Vapor Deposision, 진공상태에서 박막을 입히고 고온처리해서 증착하는 방법)로 증착합니다. - Photoresist (PR,

포토레지스트)를 spin 코팅으로 두껍게 증착하고 약 100도 정도의 열로 경화 (Baking)시킵니다. PR은 자외선 처럼 파장이 짧은 빛을 받으면 성질이 변하면서 녹아내리는 코팅 막을 가리킵니다.

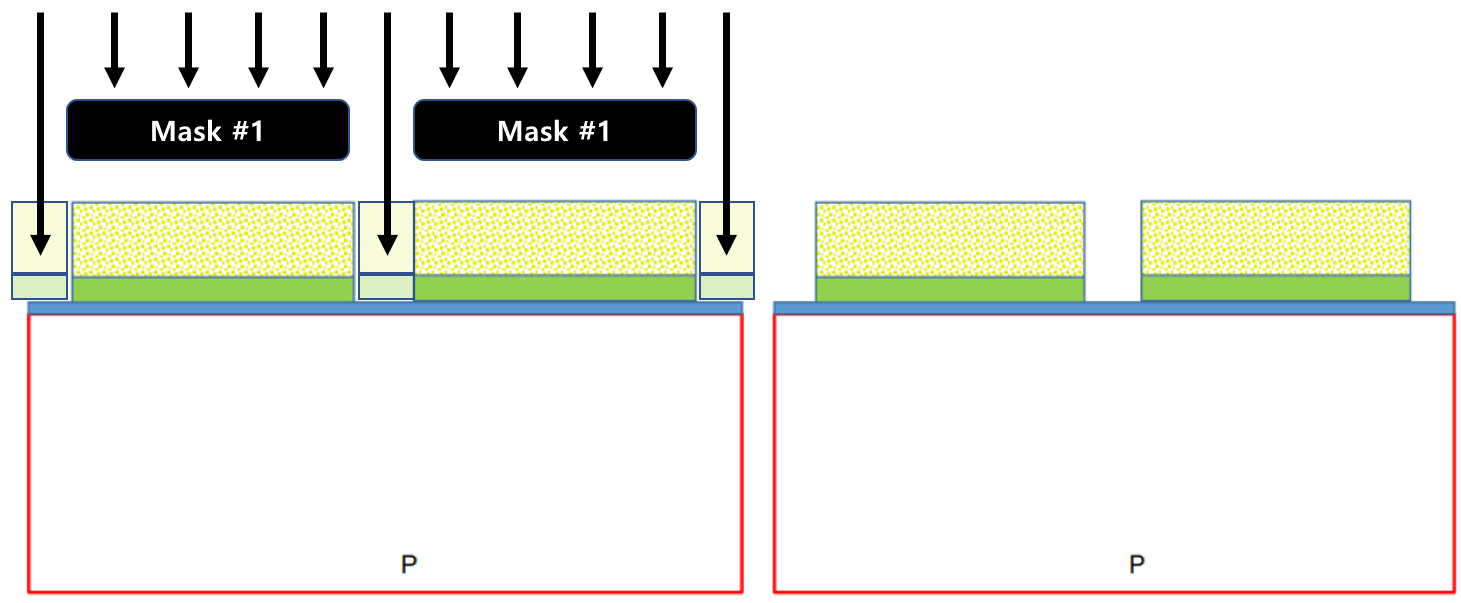

Step 2. Mask #1 사용

- PR을 제거할 영역과 제거하지 않을 영역을 구분하기 위해 1번 mask를 사용해서 빛을 가립니다. 빛을 받은 영역의 PR은 제거되고 이외의 영역은 남게 됩니다.

- PR이 제거된 영역의 nitride를 dry etching (식각)합니다.

- 표면의 PR을 모두 제거합니다.

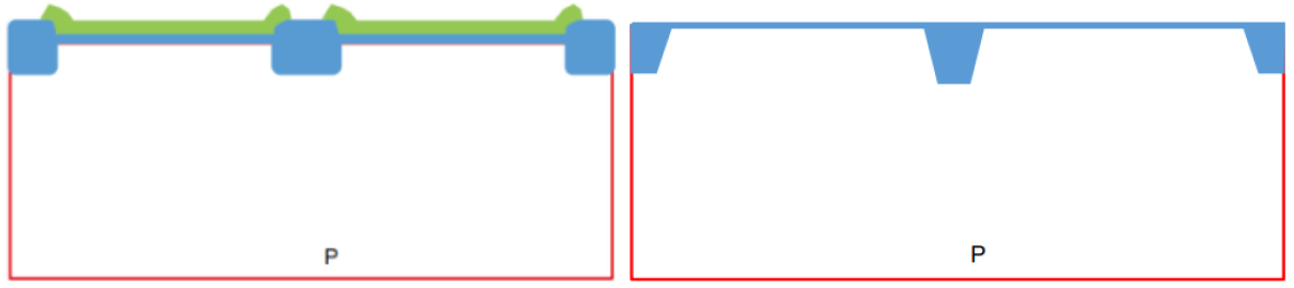

Step 3. Isolation 만들기 (LOCOS vs STI)

- 서로 다른 타입의 MOSFET이 들어갈

well을 만들기 위해서는 각 영역을 구분해 줄 필요가 있습니다. 이 구분은Isolation이라 불리는 oxide로 만들어집니다. - Isolation을 만드는 방법은

LOCOS(LOCal Oxidation of Silicon)라는 고전적인 방법과STI (Shallow Trench Isolation)이라는 신식 방법이 있습니다. - LOCOS는 step 2에서 드러난 pad oxide (파란색)부위에 boron (붕소)이온을 주입해서 oxide를 성장시키고 확산시켜서 좌측의 그림처럼 isolation을 만드는 방법입니다.

- LOCOS는 Bird's Beak Effect라는 현상이 발생하므로 이제 현업에서 사용하지 않습니다.

- 이온 주입으로 성장한 pad oxide가 MOSFET이 생성될

active region까지 침투해서 영역을 좁게 만듭니다. 집적도가 높아지는 현대 반도체 공정에서는 아주 약간의 영역 침투도 굉장히 예민한 문제이므로 가장 치명적인 단점입니다. - 실리콘 결정결함을 만들어서 생겨 제품의 신뢰도를 낮춥니다. 신뢰도가 낮은 제품은 오래 사용할 수 없고 금방 고장나게 됩니다.

- 이온 주입으로 성장한 pad oxide가 MOSFET이 생성될

- LOCOS는 Bird's Beak Effect라는 현상이 발생하므로 이제 현업에서 사용하지 않습니다.

- STI는 step 2에서 드러난 pad oxide (파란색)부위를 trench etching으로 도랑을 파내듯 식각한 뒤 HDPCVD (High-Density Plasma CVD)로 oxide를 채웁니다. 그리고 CMP (Chemical-Mechanical Polishing)라는 과정으로 nitride와 잉여 pad oxide를 갈아버려 제거해서 우측의 그림처럼 isolation을 만드는 방법입니다.

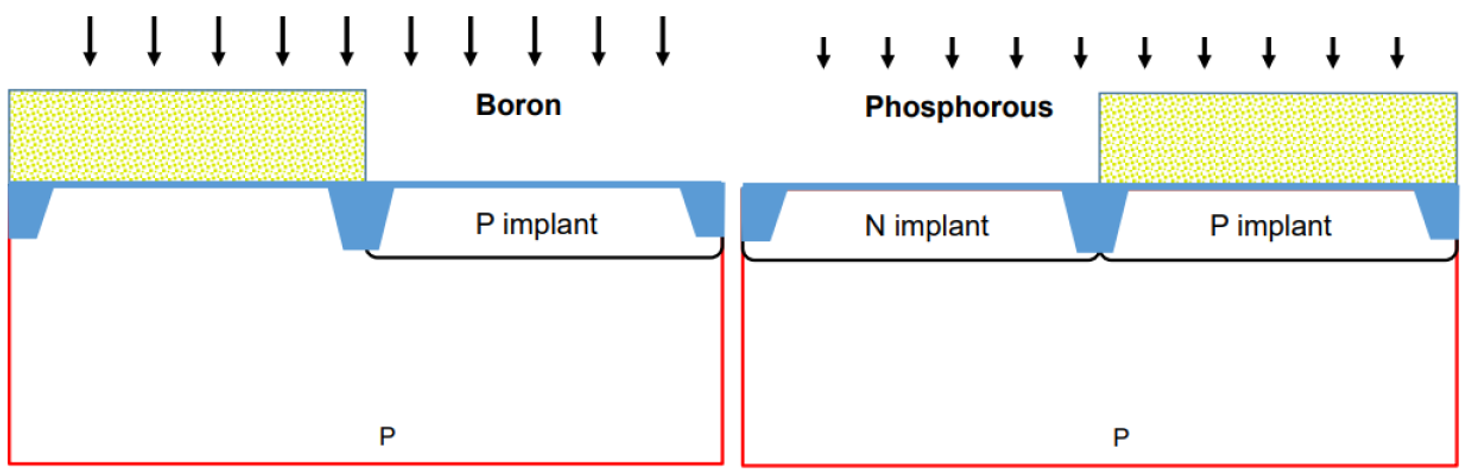

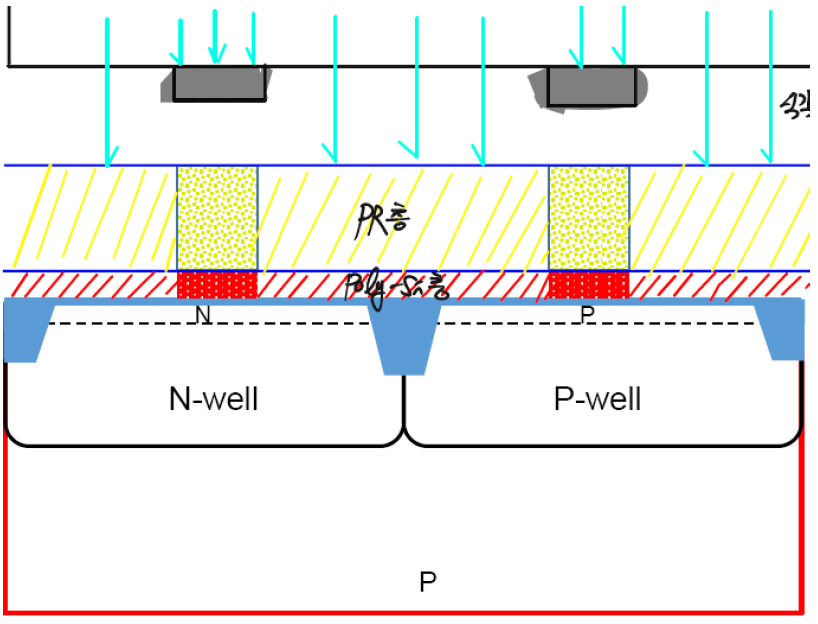

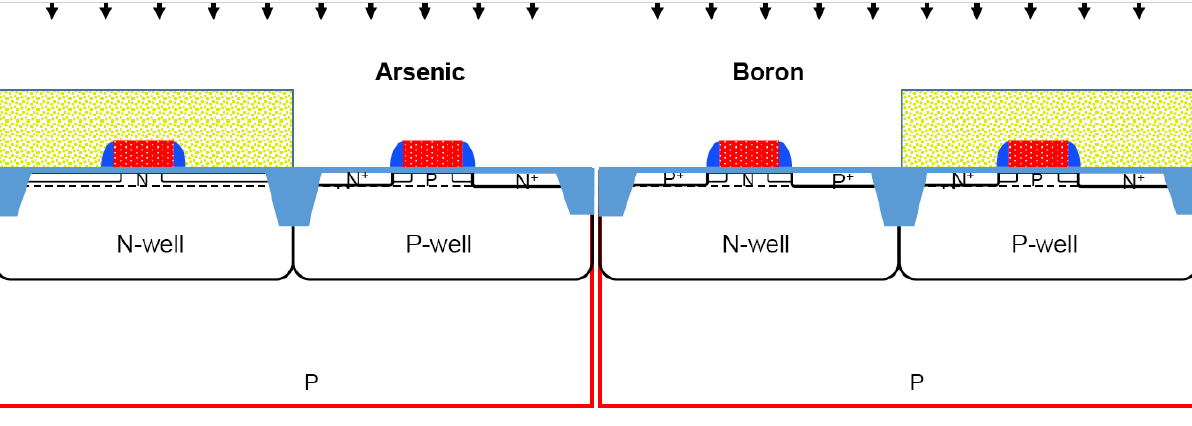

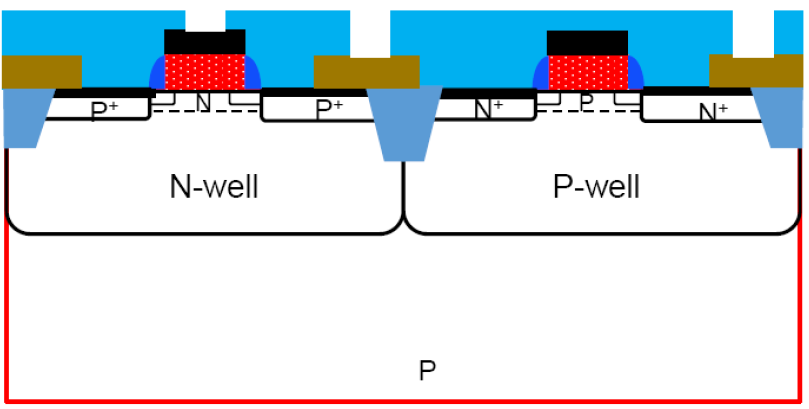

Step 4. Mask #2, 3 사용, 이온 주입

- 먼저 표면에 PR을 증착한 뒤 baking 합니다.

- 2번 mask를 이용해서 p-type 이온 주입 (implant)을 진행할 NMOS 지역만 PR을 제거합니다.

- 해당 영역에 boron 이온을 주입하면 p-type으로 도핑됩니다.

- PR을 cleaning 합니다.

- 다시 표면에 PR을 증착한 뒤 baking 합니다.

- 3번 mask를 이용해서 n-type 이온 주입을 진행할 PMOS 지역만 PR을 제거합니다.

- 해당 영역에 phosphorous (인) 이온을 주입하면 n-type으로 도핑됩니다.

- PR을 cleaning 합니다.

-

Recovery thermal annealing을 수행합니다. 정말 중요한 과정입니다.

- Recovery annealing이란 이온 주입 후 고열처리를 하는 과정을 의미합니다. 다음과 같은 3가지 이유 때문에 반드시 수행해야 하는 과정입니다.

- 주입된 이온이 실리콘 원소 자리를 안정적으로 차지해서 active dophant가 될 수 있기 때문입니다.

- 이온주입으로 실리콘이 원소 단위로 damage를 입게 되는데, 이를 회복시켜 주기 때문입니다.

- 각 implant 영역이 우리가 원하는 만큼 아래로 확산 (drive-in)되어 well 구조를 만들 수 있기 때문입니다.

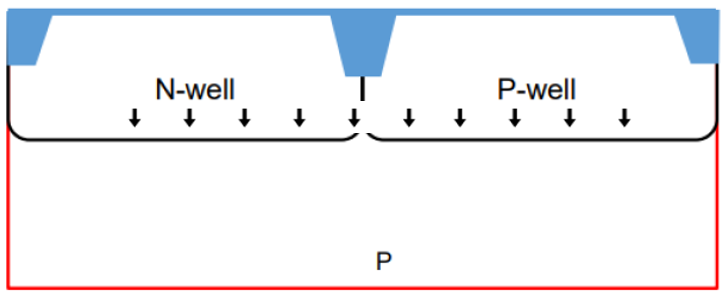

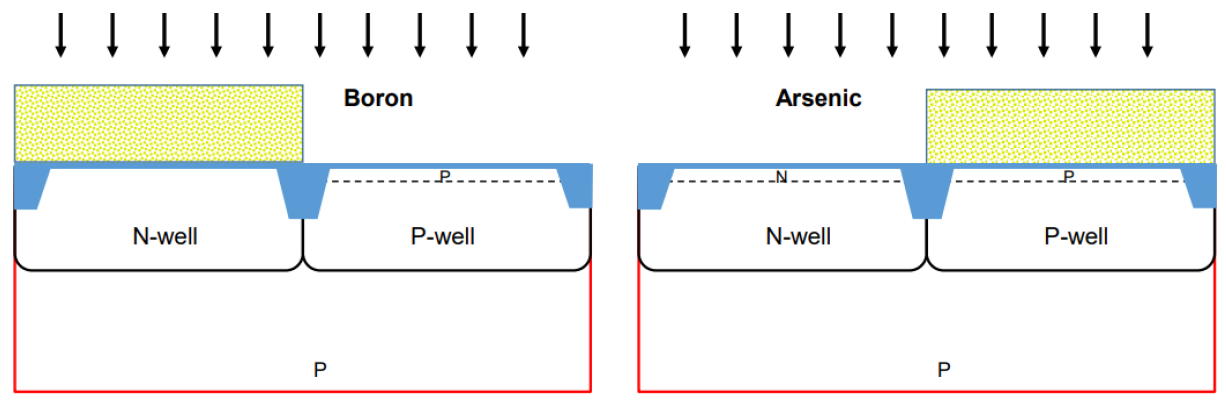

Step 5. Mask #4, 5 사용

- 먼저 표면에 PR을 증착한 뒤 baking 합니다.

- 4번 mask를 이용해서 p-type 이온 주입 (implant)을 진행할 NMOS 지역 (P-well)만 PR을 제거합니다.

- 해당 영역에 boron 이온을 주입하면 p-type으로 도핑됩니다.

- PR을 cleaning 합니다.

- 다시 표면에 PR을 증착한 뒤 baking 합니다.

- 5번 mask를 이용해서 n-type 이온 주입을 진행할 PMOS 지역 (N-well)만 PR을 제거합니다.

- 해당 영역에 Arsenic (비소) 이온을 주입하면 n-type으로 도핑됩니다.

- PR을 cleaning 합니다.

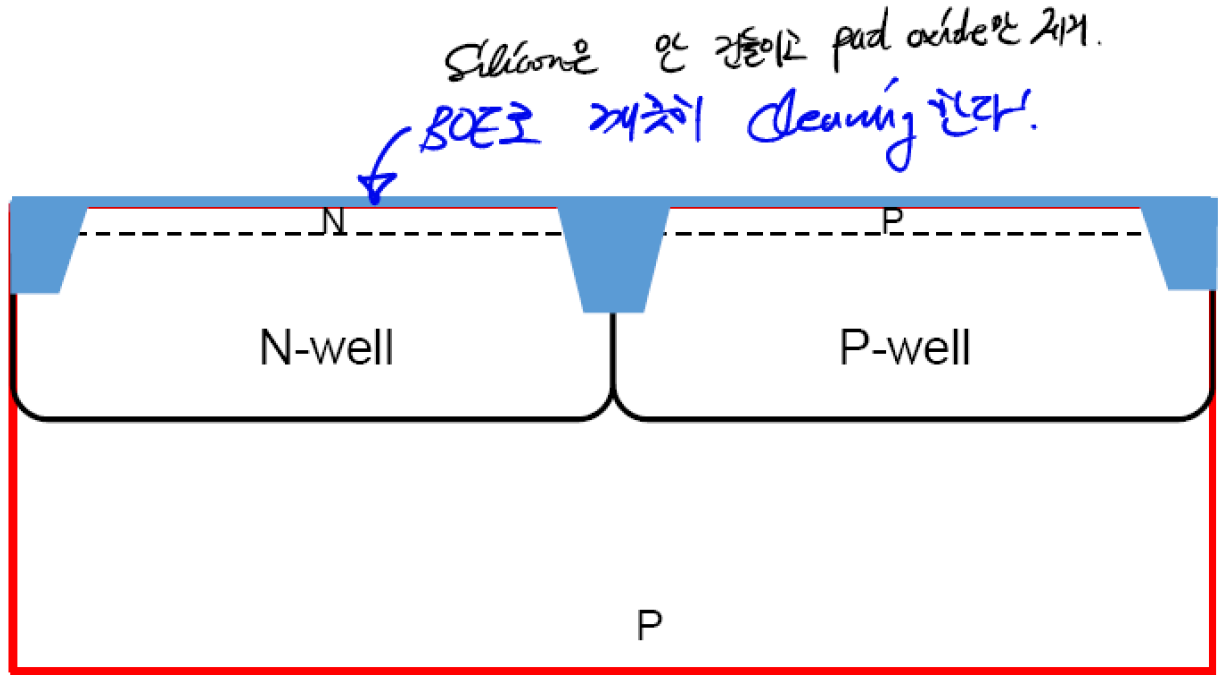

Step 6. BOE & Cleaning 과정

-

Active region 위에 남아있는 pad oxide를 BOE (

Buffered Oxide Etcher)라는 희석된 불산 ()으로 cleaning 합니다. -

다음 기회 (Cleaning part를 메인 토픽으로 다루는 글)에 더 자세히 설명하겠지만 cleaning에도 여러 과정이 있습니다. 그 과정 중에 BOE로 잉여 pad-oxide를 제거하는 과정이 가장 중요합니다.

-

Cleaning 이후 고열처리를 해서 gate oxide를 약간 성장시킵니다.

Q. Pad oxide와 gate oxide 두 용어가 너무 햇갈리네요!

A. Pad oxide와 gate oxide는 저도 정말 햇갈렸던 두 개념입니다. 아무리 구글링을 해도 명확한 차이를 알 수 없었습니다. 제가 지금까지 이해한 내용이 맞다면 두 oxide의 조성은 로 동일합니다. 다만 wafer 표면에 고루 펴져 증착된 oxide를 pad oxide라고 부르고, CMOS의 gate 밑에있는 oxide를 gate oxide라고 따로 명명한 듯 싶습니다. 즉 본 cleaning 과정은 더 이상 쓸데없는 pad oxide를 모두 제거하고 CMOS를 위한 oxide만 성장시켜서 이후 과정에 끌고 가기 위한 과정이라고 이해하시면 됩니다.

Step 7. Poly-Si 증착하기

-

LPCVD를 이용해서 Poly-Si ()를 증착합니다.

-

이때 Poly-Si는 금속에 비해 전도도가 낮기 때문에 high-dose doping (고농도 도핑)해줍니다.

Q. 근데 왜 금속 안 쓰고 Poly-Si를 먼저 사용하나요?

A. 좋은 질문입니다. 그 이유는 두 가지가 있습니다. 먼저 이형의 두 물질을 접합할 때 생기는 결정손상 같은 문제를 최소화하기 위해서, 그리고 문턱전압의 조정이 더 유리하기 때문입니다. 따라서 signal delay를 최소화하기 위해 전도성은 금속만큼 좋아야하고 문턱전압 조정이 유리해야하며 Si와 결합해도 문제가 생기지 않기 위해서 실리콘 계열의 물질을 게이트 물질로 사용해야 했고 가장 적합한 물질이 Poly-Si 였다고 이해하시면 됩니다. (더 자세한 내용은 - https://news.skhynix.co.kr/1680 에서 확인하실 수 있습니다.)

-

Step 8. Mask #6 사용

- PR을 두껍게 증착하고 baking 한 뒤 6번 mask를 이용해서 gate 부분만 PR을 남깁니다.

- Anisotropic etching (수직방향으로 잘 식각하는 dry etching의 일종)으로 poly-Si를 식각합니다.

- 이 과정으로 gate length가 결정되고 feature size에 굉장히 큰 영향을 미치기 때문에 가장 정밀하고 세밀한 patterning이 필요합니다.

- 따라서 사용하는 mask도 식각기술도 굉장히 정밀해야 합니다.

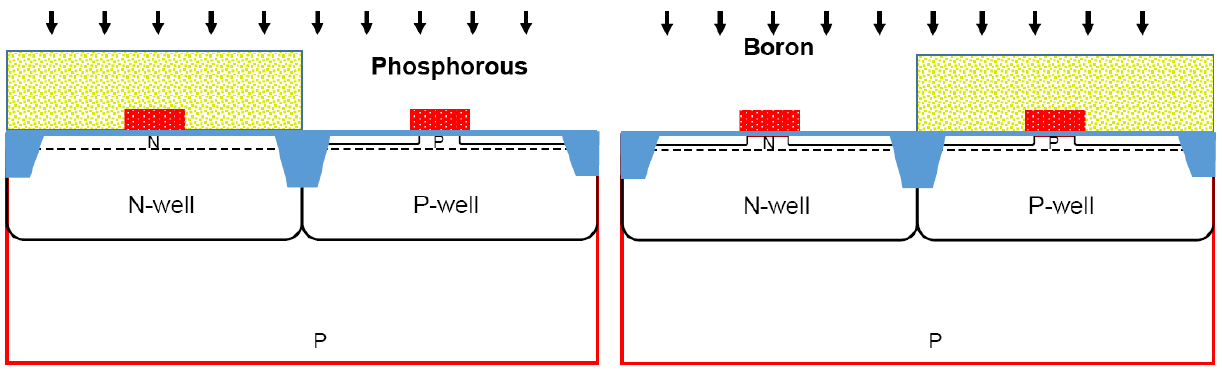

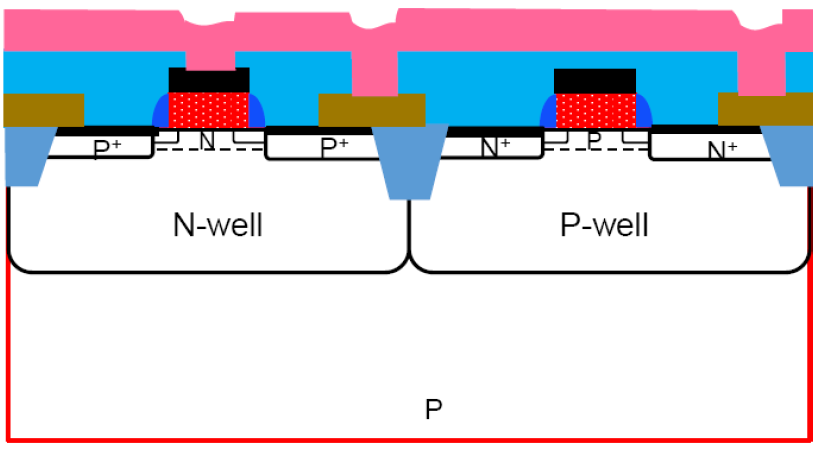

Step 9. Mask #7, 8 사용, 이온 주입

- (CMOS의 각 well 이온 주입 과정은 step 4와 5에서 충분히 설명했으므로 간략하게 넘어가겠습니다.) 각 필요한 부분에 증착시킨 PR을 7번, 8번 mask를 이용해서 제거합니다.

- NMOS 지역에는 p-type, PMOS 지역에는 n-type으로 low dose로 이온을 주입합니다.

- 이 과정은 LDD 구조를 만들기 위한 사전 작업이라고 이해하시면 됩니다.

- LDD (Light Doped Drain) 구조란?

- 옛날에는 인가해주는 전압이 현재보다 높았고 feature size가 커서 각 MOS 사이의 거리가 길었습니다. 하지만 이제는 인가되는 전압이 굉장히 낮아졌고 feature size도 굉장히 짧아졌습니다.

- 전기장 이고, 가 점점 짧아지다보니 전기장 가 폭발적으로 증가하게 됐습니다. 이기 때문에 힘도 증가하면서 전자들의 이동속도 (drift velocity)도 따라서 증가했습니다. 이를

Hot Carrier Effect라고 부릅니다. - 이 Hot carrier effect 때문에 전자가 굉장히 빠른 속도로 drain 지역과 부딪히면서 gate oxide를 취약하게 만들고 음전하가 쌓이게 됩니다. 따라서 제품의 신뢰도를 낮추는 문제와 문턱전압도 바꿔버리는 문제를 일으킵니다.

- LDD 구조는 gate 하단에 source, drain 사이 영역에 매우 low dose로 도핑된 영역을 만들어서 공핍층 (depletion layer)을 의도적으로 확대해 전자의 속도를 낮추는 구조이며 hot carrier effect를 방지하는 역할을 합니다.

- LDD (Light Doped Drain) 구조란?

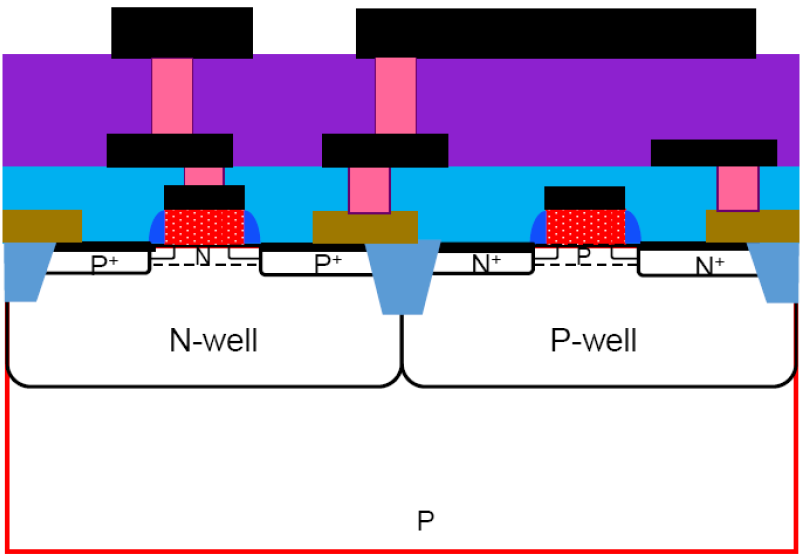

Step 10. Oxide 증착, Side-wall spacer 만들기

- 이번에는 를 LPCVD를 이용해서 두껍게 증착시킵니다.

- Step 8에서 사용했던 anisotropic etching을 이용해서 식각합니다.

- Anisotropic etching은 수직방향으로 식각을 하는 기술이므로 측면 식각은 상대적으로 잘 안되서 poly-Si 양 옆으로 약간의 가 남게 됩니다.

- 이렇게 남는 를 Side-wall spacer라고 부르며 LDD 구조를 만들기 위한 두 번째 사전 준비물 입니다.

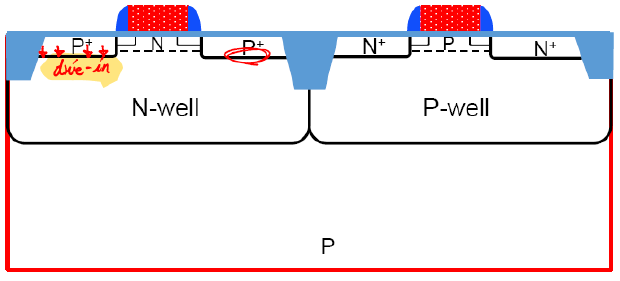

Step 11. Mask #9, 10 사용, LDD 구조 완성

- 각 지역을 low-dose로 도핑하면서 LDD구조를 완성합니다.

Step 12. RTA (Rapid Thermal Annealing)

- Recovery annealing과 유사한 이유로 진행하며 비슷한 효과를 얻을 수 있습니다. 30초 ~ 1분 정도로 매우 짧게 고열처리 합니다.

- N+, P+ 도핑 영역이 조금 더 아래로 drive-in 됩니다.

- 이후 BOE로 active region 표면의 pad oxide를 cleaning 합니다.

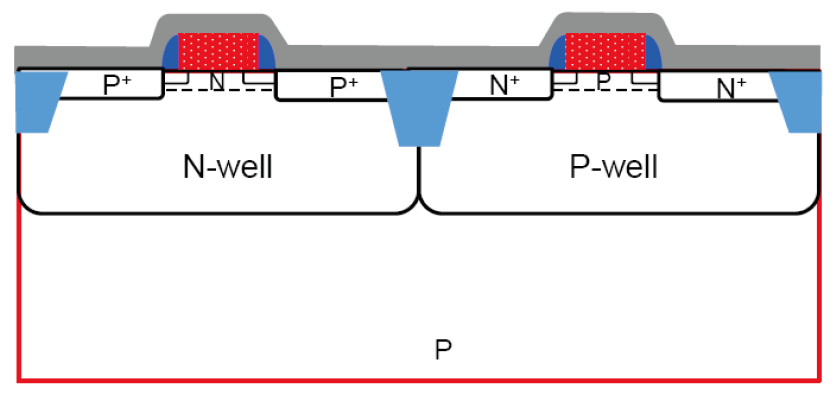

Step 13. SALICAIDE (살리사이드), Mask #11 사용

- 살리사이드는

Self-Aliged Silicide의 약자로 , 같은 실리콘 계열의 준금속 금속화합물 (Silicide, 실리사이드)을 정렬하면서 증착하는 과정을 의미합니다. Lithography 과정에서 가장 중요하다고 말할 수 있는 과정입니다. - 살리사이드 과정은 Sputtering (스퍼터링) 방법으로 증착시킵니다. Sputtering이란, 이온화된 Ar 따위의 가스 원자를 증착시킬 물질에 플라즈마를 이용해 강하게 충돌시켜서 원자와 전자를 튀어나오게 만들어 타겟 표면에 박막형태로 증착시키는 방법을 의미합니다.

- Sputtering 방법으로 (또는 )를 증착시키면 표면의 와 반응해서 실리사이드 (검정색 부분)로 바뀝니다. ()

- 이때 step 10에서 만들었던 sidewall spacer가 poly-Si의 양쪽 옆면은 와 반응하지 않도록 보호해주는 역할을 합니다.

- 반응하지 못한 잔여물은 으로 남으며 내부 도선 (Local Interconnect)로 사용할 부분만 남기고 11번 mask를 이용해서 식각합니다. 이 내부 도선은 이후 유용하게 사용할 수 있습니다.

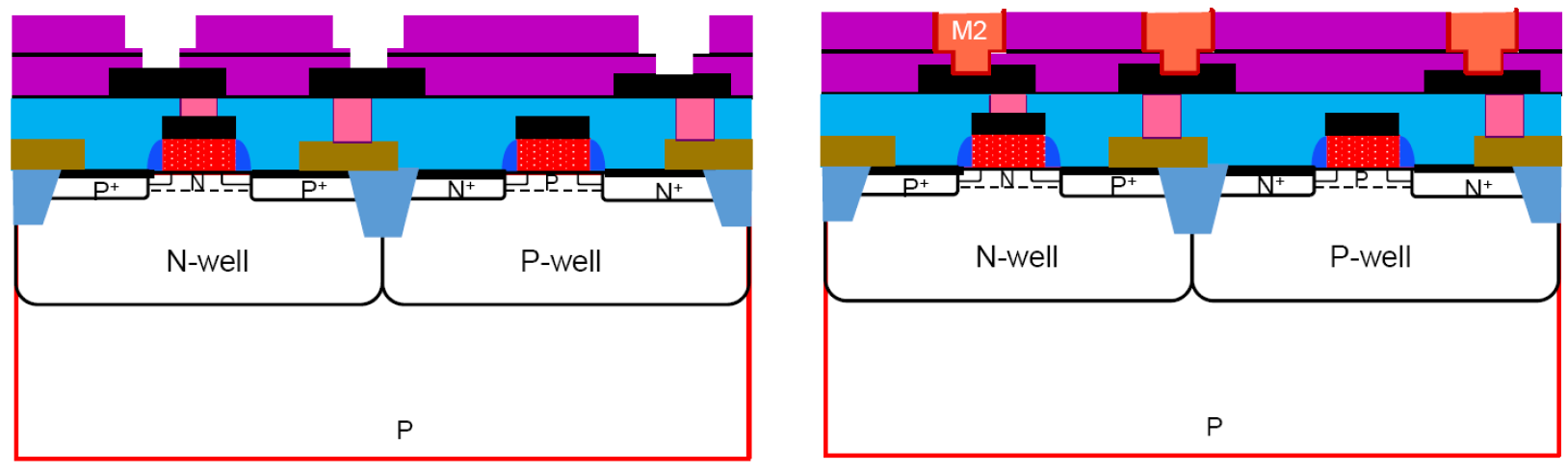

Step 14. PMD 증착 후 CMP, Mask #12 사용

- PMD (

Pre-metal Dielectric SiO2)층을 LPCVD 또는 APCVD로 두껍게 증착합니다.- 이때 전 단계들에서 증착된 여러 소자 때문에 필연적으로 표면에 굴곡이 생기게 되는데 이 굴곡이 해상도와 DoF (Depth of Field)에 악영향을 주므로 반드시 평면화 (Planarization)를 통해 최대한 높게 만들어줘야 합니다.

- CMP로 평면화를 수행합니다.

- Contact가 뚫릴 위치를 잘 조절 (alignment)해준 뒤 12번 mask를 이용해서 hole을 뚫어줍니다.

Step 15. 텅스텐 (W)증착

- CVD를 이용해서 표면에 와 을 증착시킵니다.

- 와 을 증착시키는 과정이 필요한 이유는 두 가지가 있습니다.

- 텅스텐 ()이 PMD와 잘 달라붙지 않기 때문입니다. 를 미리 증착시키면 가 더 잘 붙도록 접착력을 높힐 수 있습니다.

- 텅스텐 ()을 증착시키기 위해 CVD를 거치는데 이때 사용하는 가스로부터 를 보호하기 위해 을 미리 증착합니다.

- CVD를 이용해서 표면에 를 증착시킵니다. 는 채움성이 좋은 물질이라 feature size가 점점 작아져서 굉장히 미세하고 얇아진 hole도 잘 채워줍니다.

- CMP로 표면을 평탄화하면서 잉여 를 제거합니다.

Step 16. 알루미늄 도선 깔기, Mask #13 사용

- CVD를 이용해서 표면에 와 을 증착시킵니다.

- 도선으로 사용할 1번 금속 알루미늄()과 PR을 표면에 증착시킵니다.

- 현재 공정에서는 더 이상 도선으로 알루미늄을 사용하지 않고 구리를 사용합니다.

- 전자가 고속으로 이동하면서 알루미늄 원소를 치고 지나가는 EM (Electro Migration) 현상 때문에 시간이 지날수록 도선의 신뢰도가 떨어지기 때문입니다.

- 알루미늄의 전기전도도가 구리보다 낮기 때문입니다.

- 구리는 플라즈마 etching이 통하지 않는다는 단점이 있지만 다른 방법 (Damascene, 상감법)을 이용해 식각이 가능해졌기 때문입니다.

- 현재 공정에서는 더 이상 도선으로 알루미늄을 사용하지 않고 구리를 사용합니다.

- 13번 mask를 이용해서 patterning을 하고 플라즈마 etching으로 필요없는 알루미늄을 제거하고 PR도 제거합니다.

(+) Damascene (상감법)이란?

- 구리 도선은 플라즈마 etching이 불가능하므로 상감법을 사용합니다.

- IMD#n 층을 기존보다 훨씬 두껍게 증착합니다.

- Via hole과 trench를 함께 파냅니다.

- 표면에 와 을 증착시키고 를 증착합니다.

- CMP로 표면의 를 제거해주면 가 가득 찬 via hole이 만들어집니다.

Step 17. IMD 증착

- IMD를 증착하고 via를 뚫고 2번 금속을 증착하는 과정은 step14, 15, 16을 반복하면 됩니다.

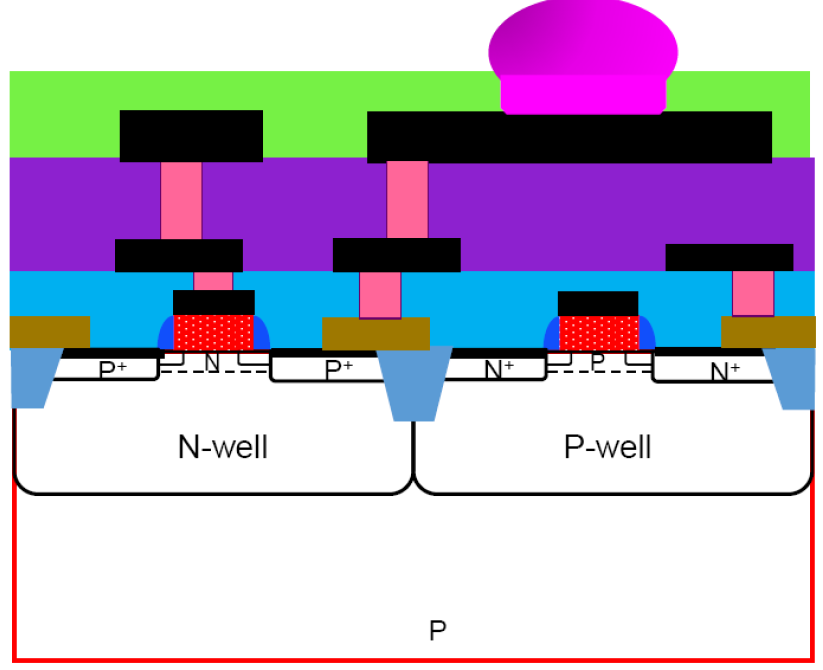

Step 18. Passivation, Mask #16, 17 사용

- IMD#n을 보호하기 위해 마지막 단계로 PECVD (

Plasma Enhanced CVD)를 이용해서 silicon nitride () passivation layer를 증착합니다. (초록색 부분) - 16번 mask를 이용해서 pad contact를 뚤어주고 17번 mask를 이용해서 pad etching을 해주는 것으로 공정이 마무리 됩니다.

이번 포스트에서는 CMOS에 대한 개요를 다뤄봤습니다.

방대한 내용이라 받아들이시기 쉽지 않으리라 생각합니다.

뭐든 첫 술에 배부른 것은 없습니다. 한 번에 하나씩 받아들이되 전체 그림과 과정을 잃어버리지 않으려고 애쓰시길 바랍니다!

다음 포스트에서는 8대 공정 중 첫 번째 과정인 웨이퍼 제조 공정에 대해서 다뤄보겠습니다. 읽어주셔서 감사합니다. 🙂

3개의 댓글

안녕하세요. 포스팅 정말 잘 읽었습니다. 읽다가 궁금한 점이 생겨 댓글 남겨요!

step 4에서 NMOS에는 P-well을, PMOS에는 N-well을 이온주입과 어닐링으로 만들어주었는데 step 5에서 다시 NMOS에는 p 타입인 붕소를 PMOS에는 n 타입인 비소를 implantation을 해준 이유가 무엇인가요? step 4에서 각각 well을 만들어주었기에 따로 할 필요가 없지 않나 해서요,,,

추후에 step 9에서 source와 drain을 위한 implantion을 하는데 step 5 과정이 필요한 이유가 있을까요?

아 그리고 step 9에서 설명하실때, " NMOS 지역에는 p-type, PMOS 지역에는 n-type으로 low dose로 이온을 주입합니다. " 라고 하셨는데 source와 drain 쪽 영역을 만들기 위함이므로 NMOS에는 n PMOS에는 p인것 같은데 착각하신건가요? 아니면 제가 잘못알고 있는건가요 ㅠㅠ

긴 글 읽어주셔서 감사합니다! 포스팅 진짜 잘봤어요

대단히 고맙습니다. 비전공자여서 기존의 8대공정 내용으로는 반도체 제조공정을 제대로 이해하기가 어려웠는데, 조금 더 알게 되었습니다. (다 이해했다는 의미는 아니고요 ^^)