- 모든 내용의 출처는' 고꾸라진고구마'님의 글 'https://blog.naver.com/minky0118/221860772321'을 기반으로 합니다.

DRAM의 구조와 동작원리

- DRAM은 위와 같이 트렌지스터의 source 또는 drain 단자 중 하나에 capacitor가 달려있는 구조를 가지고 있습니다. 이를 1T1C구조라고 부릅니다.

- DRAM의 source(또는 drain)와 gate는 각각 외부와 연결된 도선과 연결되어있는데요, 이 도선들에 적절한 전압 ()이 인가되어 source와 drain 사이에 channel이 형성되어 capacitor로 전류가 흐르게 되어 전자가 축적되어 전기적으로

0또는1신호를 가지게 되는 방식으로 data를 저장합니다. - Gate 쪽이 WL(

word line)에 붙어있으며 양 옆으로 BLC(Bit Line Contact)와 SNC(Storage Node Contact)가 있고 SNC 쪽에는 capacitor가 달려있습니다. - 2개의 transistor는 1개의 BLC를 공유합니다.

- 2개의 BL (

Bit Line, BL/BL')은 1개의 SA (Sense Amplifier)를 공유합니다. - DRAM은 subthreshold current와 같은 leakage current (누설전류)로 인해 주기적으로 capacitor의 방전되어가는 전하를 보상해주는 과정인 refresh가 필요합니다. DRAM의 data 보존 능력을 retention이라고 부르며 DRAM 전체 cell의 99% 이상이 retention time이 1초가 넘지만 몇 몇 cell들은 최소 시간인 64ms도 유지하지 못합니다.

Write 하는 방법

- WL을 ON해서 해당 row의 모든 트랜지스터의 gate에 전압을 인가합니다.

- 특정 BL에 전압을 인가합니다. 이때

1을 쓰고싶다면 전압을 인가하고0을 쓰고싶다면 를 인가합니다. - Channel을 통해 전류가 통하며 SNC는 BLC와 전압이 같아지고 capacitor에 전하가 저장되면서 정보가 기록됩니다.

Read 하는 방법

- WL을 OFF하고 precharge합니다.

- Read의 경우 원하는 셀의 capacitor을 의도적으로 방전시켜서 읽은 전하값으로 데이터를 읽기 떄문에 감쇄된 전하를 보상해주기 위해 재충전하는 과정인

precharge가 필요합니다. - Precharge는 DRAM controller의 CS, RAS, WE가

0이고 CAS가1이면 수행되며 WL과 SA를 off한 뒤 의 절반만큼 선택된 BL에 인가해 전하를 보상해서 다음 연산에 대한 ACT 신호를 대비합니다.

- Read의 경우 원하는 셀의 capacitor을 의도적으로 방전시켜서 읽은 전하값으로 데이터를 읽기 떄문에 감쇄된 전하를 보상해주기 위해 재충전하는 과정인

- WL을 ON하고 SNC로부터 BLC로 흐르는 전류를 통해 BL의 전압 변화량을 확인합니다.

- BL의 전압 변화량을 통해 LVDS (

Low Voltage Differential Swing)로 SA가 증폭한 뒤 read합니다. SA가 제대로 감지하기 위해 BL의 전압변화량이 커야하고 그러기 위해서는 SA와 연결된 두 BL과 연결된 CMOS transistor의 oxide의 capacitance를 잘 조절해야합니다. 또한 RC delay를 최대한 줄이기 위해 BL에 사용하는 금속을 최대한 전도성이 높은 물질로 채택하는 것이 유리합니다.

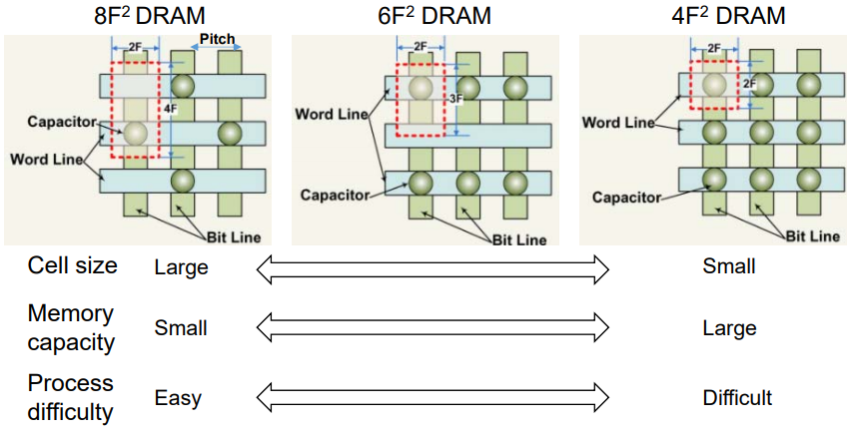

DRAM Cell 크기

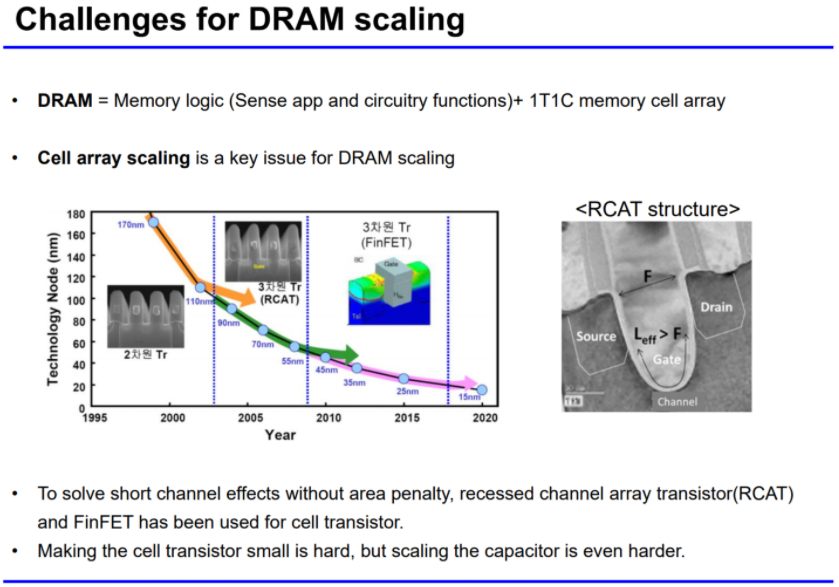

DRAM Cell - Transistor의 발전

Short channel effects를 해결하기 위해 capacitance를 늘려야했고 두께를 줄이니 tunneling이 발생했습니다. 이를 해결하기 위해 cell 구조에 대한 여러 의견이 제시되었고 결과적으로 현재는 3D-super DRAM으로 향하는 방향으로 귀결된 것 같습니다.

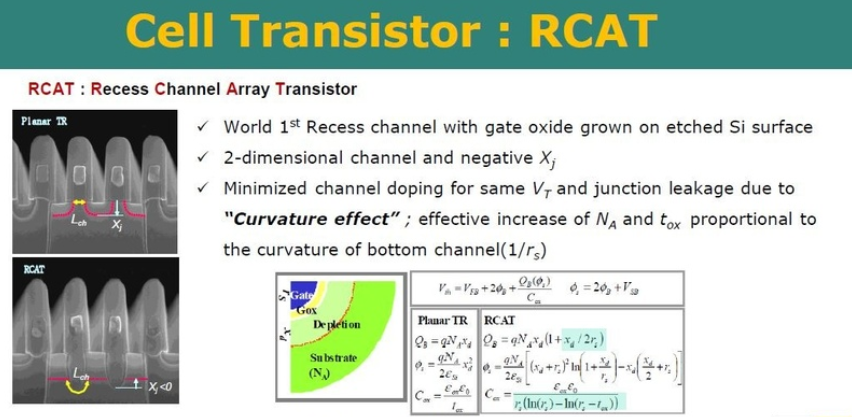

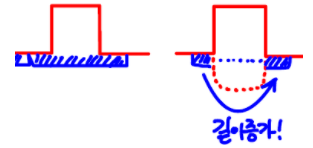

① RCAT (Recess Channel Array Transistor)

- 물리적으로 gate의 길이는 짧게 만들 수 있지만 channel의 길이는 물리전자적인 이유로 인해 짧게 만드는 것이 어렵습니다.

- Leakage current의 원인은 short channel에 있기 때문에 물리적인 gate의 길이를 줄여 transistor의 크기를 줄이면서 effective channel length는 늘려서 short channel effects를 줄이는 것이 좋습니다.

- 따라서 gate 밑부분의 substrate를 파내서 (recess: 우묵 들어간 부분) channel을 물리적으로 막아버린다면 channel의 길이 자체는 그대로지만 전자가 우회해서 이동해야 하기 때문에 effective channel length는 증가하는 꼴이 됩니다.

- Effective channel length가 증가하므로 해당 영역의 doping 농도는 기존보다 증가할 것이고 pn접합에 의해 생기는 depletion 영역이 상대적으로 생기기 어려워집니다. 따라서 roll-off 가 해결되어 누설전류가 감소하는 효과를 얻을 수 있습니다.

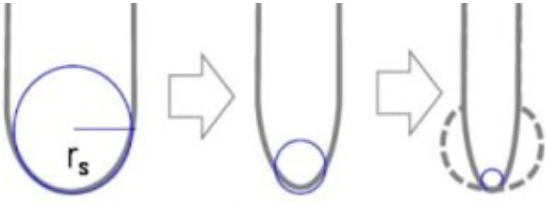

② S-RCAT (Sphere-RCAT)

- Channel의 길이가 점점 짧아지면서 RCAT 때 파낸 gate도 점점 좁아지면서 의미가 없어지는 수준에 이르렀습니다.

- 따라서 gate controllability를 충분히 확보하기 위해 이번에는 둥글게 다시 파내주는데 이 방법을 S-RCAT라고 합니다.

③ S-Fin (FinFET + S-RCAT, Saddle-Fin)

- FinFET 구조에 S-RCAT를 융합해서 두 구조의 장점을 모두 살린 구조입니다.

- FinFET은 gate가 oxide와 닿는 면적을 3면으로 늘려서 gate controllability를 늘릴 수 있었고 RCAT로 effective channel length늘 늘리고 Vth roll-off를 해결해서 누설전류를 감소시켰습니다.

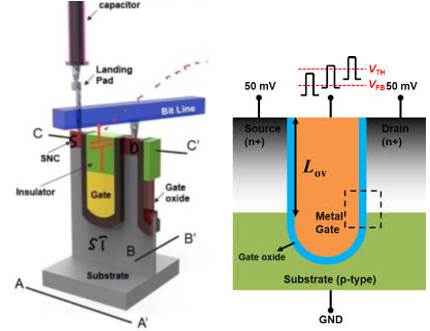

④ BCAT (Buried Channel Array Transistor)

- 현대 DRAM에서도 사용하고 있는 BCAT는 S-Fin 구조에서 gate를 아예 substrate에 묻어버리고 위를 insulator로 덮어버리는 형태로 발전한 구조입니다.

- 이렇게 substrate가 in

- Gate가 아래로 묻혀버리므로 drain과 곂치는 구간이 감소하게되어 자연스래 GIDL(Gate Induced Drain Leakage)이 해소됩니다. 또한 BL과 gate의 물리적 거리가 멀어지므로 BL의 기생 capacitance가 줄어듭니다.

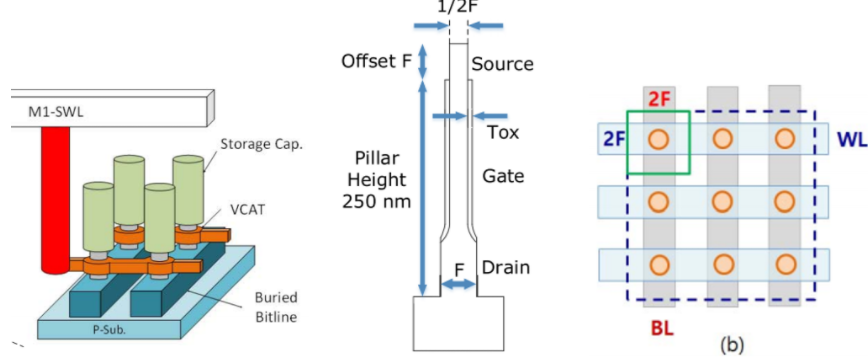

⑤ VCAT (Vertical Channel cell Array Transistor)

[1]. Y. Cho et al., "Suppression of the Floating-Body Effect of Vertical-Cell DRAM With the Buried Body Engineering Method," in IEEE Transactions on Electron Devices, vol. 65, no. 8, pp. 3237-3242, Aug. 2018, doi: 10.1109/TED.2018.2849106.

[2]. J. B. Park, W. R. Davis and P. D. Franzon, "3-D-DATE: A Circuit-Level Three-Dimensional DRAM Area, Timing, and Energy Model," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 2, pp. 756-768, Feb. 2019, doi: 10.1109/TCSI.2018.2868901.

- VCAT는 기존에 가로 형태로 누워있던 transistor를 세우는 방식으로 scale을 감소시키고 수직으로 쌓아올리는 방식의 구조입니다.

- Size는 널리 알려진 8F2에서 BCAT부터는 6F2로 감소했고 VCAT를 사용하면 4F2로 감소시킬 수 있습니다.

- Floating Body Effect라는 심각한 문제 때문에 VCAT 구조는 아직 상용화가 되지 않았습니다.

- Floating Body Effect는 이런 수직구조의 transistor에서 보이는 고질적인 문제로 과거에 SOI (Silicon on Insulator) 구조를 채택함으로써 해결한 문제입니다. 수직구조는 전류가 수직으로 흐르게 되는데 전자는 source에서 drain으로 잘 이동하지만 hole은 source와 gate 사이의 중립지역에 축적됩니다. 이 축적된 hole이 마치 substrate에 양전압을 가한것과 같은 효과, 즉 body effect를 유발해서 를 변화시키는 악영향을 끼칩니다. (더 쉽게 자세히 설명해드리고 싶은데 아무리 찾아도 자료가 너무 없네요...)

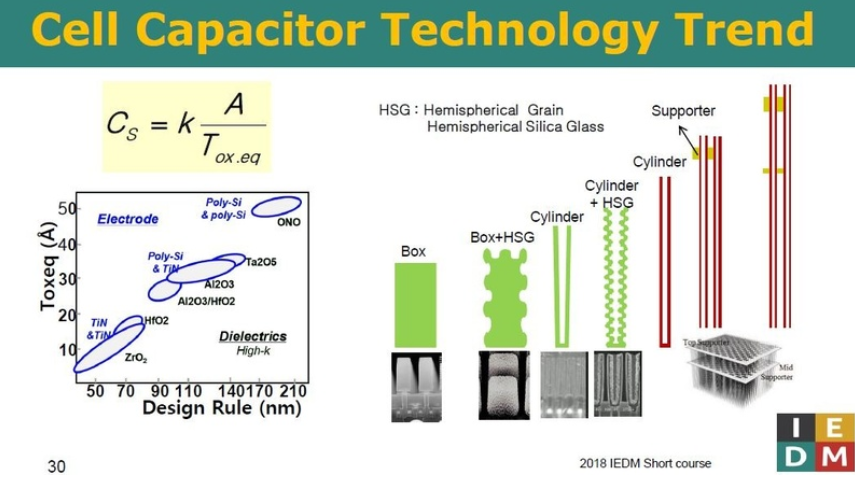

DRAM Cell - Capacitor의 발전

-

Cell capacitance를 최대한 늘리고 leakage current를 최대한 줄이기 위해 capacitor도 많은 발전을 거듭했습니다.

-

모든 글을 차근히 읽고 따라오신 분이라면 자다가 깨워서 물어봐도 답하실 수 있어야 합니다. Capacitance를 늘리기 위해 capacitor의 면적을 늘리고 oxide의 두께를 줄여야 했습니다. 그러나 scale의 감소로 면적도 비례해서 감소할 수 밖에 없었고 oxide의 두께를 지나치게 줄이면 tunneling이 일어났기 때문에 다른 방법이 필요했습니다.

-

High-k 물질을 사용해서 최소한의 oxide 두께를 확보하는 방법

-

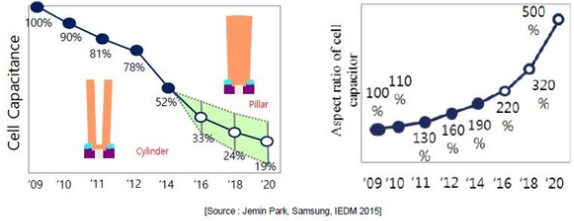

면적을 넓히기 위해 오돌토돌한 곡선 표면을 가진 실린더 형태로 바꿔 aspect ratio를 극대화하는 방법

-

-

하지만 이러한 노력에도 불구하고 capacitance는 지속해서 급속하게 떨어지고있고 앞으로도 떨어질 전망입니다.

-

왜냐하면 10F → 8F → 6F → 4F로 점점 cell은 작아지는데 아무리 유전율이 높은 재료를 사용한다고 해도 cap 감소량을 극복하기엔 부족하기 때문입니다. 또한 HKMG는 높은 온도를 거치면 막질이 열화될 수도 있고 비용이 크다는 문제도 있습니다.

-

Capacitance가 줄어듦은 곧 DRAM의 retention time이 줄어들어서 refresh cycle이 빨라진다는 의미입니다. 즉, 대기 전력이 점점 증가할 수 있다는 것을 의미합니다. 심각한 문제네요.

-

이것이 시사하는 바는 더 이상 charge-based memory는 저장 용량 확대 폭이 이전과 같이 눈부시게 이뤄지기는 힘들다는 것입니다. 앞으로는 저장용량의 확대보다는 성능 향상을 꾀할수도 있겠네요.

DRAM Reliability Issues

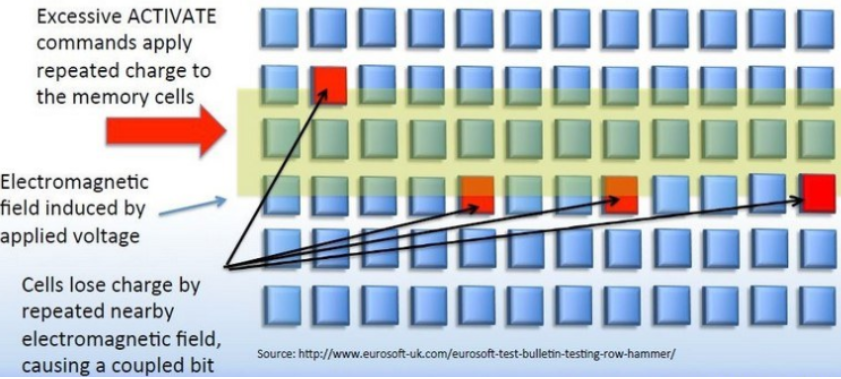

① Row Hammer

- Row hammer란, 특정 row 주소를 연속해서 계속 사용하면 인접한 row 주소의 cell capacitor 내 data가 누설되어 전기적인 간섭에 의해 바뀌거나 cell 자체가 망가져 data를 판독하지 못하는 문제를 의미합니다

- Cell 밀도가 높아질수록 cell 사이의 물리적인 거리가 짧아지면서 더욱 간섭을 받기가 쉬워지며 생긴 문제입니다.

- WL과 인접한 WL 사이의 capacitance coupling 때문에 발생합니다.

- 선택된 WL 때문에 인접한 row의 cell들에 의도치않게 channel이 생성되어 leakage가 발생합니다.

- Hot carrier가 trap을 만들어 전자들이 victim cell에 들어가거나 나옴으로써 failure가 발생합니다.

- Row hammer를 해결하는 방법으로 제시되고 있는 3가지 방법은 다음과 같습니다.

- Annealing을 통해 interface trap을 최소화합니다.

- BLC (Bit Line Contact)를 n-type doping합니다.

- 그냥 자주 refresh 해줘서 data 손실을 최소화합니다.

- 재밌는 점은 row hammer를 악용한 애플리케이션 공격방법이 존재한다는 점입니다.

- Double Sided Hammering이라 불리는 공격방법은 공격자가 n번째 row를 공격하면서 그 양 옆 (n-1, n+1) row에 순차적으로 접근하는 방법으로 이뤄집니다.

- Row hammer를 악용해서 주소 데이터를 의도적으로 바꾸면 접근 권한을 휙득해서 금지된 명령을 수행하거나 ECC 회로를 망가트려서 후속 공격을 시스템이 감지하지 못하게 만들수도 있습니다.

② Pass-Gate Effect

- 특정 cell의 gate가 ON이 되면 인접한 cell의 energy barrier가 낮아지면서 유사 roll-off 현상이 발생합니다.

- 이 현상은 cell의 scale이 점점 작아지면서 상대적으로 문제가 커지고있습니다.

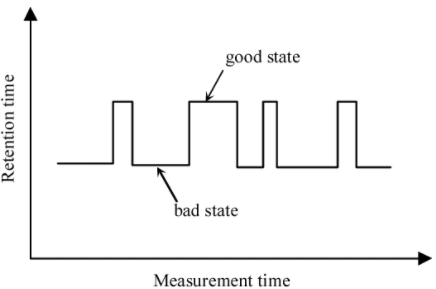

③ Variable Retention Time

- 하나의 DRAM cell의 retention time이 측정할 때마다 달라지는 현상을 말합니다.

- 즉, retention time이 경우에 따라서는 good state 일수도 bad state 일수도 있습니다.

- 실험을 최대한 다양하게 지속적으로 해서 통계적인 평균값을 내는 것이 해법이겠네요.

- 인텔 (PRAM, Phace change RAM), 삼성 (STT-MRAM, Spin-Touque-Transfer Magnetoresistive RAM), RRAM (Resistive RAM)이 휘발성이라는 최대 단점을 가지고 있는 DRAM을 대체할 차세대 메모리 반도체로 알려져있습니다.

- Charge-based memory에서 Register-based memory로 바뀌고 있으며 비휘발성 메모리로 바꾸려는 방향을 알 수 있습니다. 즉, capacitor를 대체하려고 하는거죠.

- 작동과정: https://www.youtube.com/watch?v=-rNpiBM0Ymg

3개의 댓글

안녕하세요! 덕분에 DRAM에 대해 공부 수월하게 할 수 있었습니다. 질문 드릴게 있어서 댓글 남깁니다!

"Floating Body Effect는 이런 수직구조의 transistor에서 보이는 고질적인 문제로 과거에 SOI (Silicon on Insulator) 구조를 채택함으로써 해결한 문제입니다. " 이 부분에서 SOI구조를 채택함으로써 floating body effect가 발생한 것인가요? VCAT은 심각한 floating Body Effect 문제로 상용화되고 있지 않다고 알고 있는데, 이 문장에서는 body 효과를 해결했다고 되어 있어서 이해가 안 가는데 설명 해주실 수 있을까요?!

안녕하세요! 도움 많이 받았습니다ㅎㅎ 혹시 질문 하나 해도 될까요?

"Effective channel length가 증가하므로 해당 영역의 doping 농도는 기존보다 증가할 것이고" 이 부분 이해가 안 되는데 설명 가능 할까요ㅜㅜ