- 참고한 글과 출처

- 감마의 하드웨어정보: https://gamma0burst.tistory.com/593?category=356600

- SeMi뀨: https://m.blog.naver.com/jgw1030/221240159053

- https://blog.naver.com/minky0118/221875099263

좋은 자료를 제공해주셔서 정말 감사합니다.

- 본 문서는 NAND에 대한 학부 수준의 내용을 총정리한 문서입니다.

- 부족하거나 틀린 내용에 대한 지적은 언제나 반갑습니다.

1. NAND의 구조

1.1. NAND cell 구조와 구성의 이해

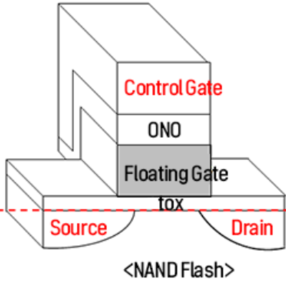

- NAND memory cell은 MOS capacitor의 일종으로 1개의 transistor에 2개의 gate를 가지고 있는 구조가 특징입니다.

- Substrate 위로 순서대로 4개의 층으로 구성되어있습니다.

- : Tunneling oxide라고 부르는 얇은 산화막 층으로 channel에 흐르는 전자가 energy band를 넘어서 뚫고 들어오는 현상인 tunneling 현상이 발생하는 곳입니다.

- Floating gate: Tunneling을 통해 왕래하는 전자들이 저장되는 곳입니다. Floating gate는 gate지만 위아래로 oxide로 둘러쌓여있기 때문에 전자들이 한 번 들어오면 쉽사리 빠져나가지 못하는 구조를 갖고 있습니다.

- ONO: Oxide-Nitride-Oxider의 약자로 흔히 blocking oxide라고 부르는 산화막 층입니다. Floating gate에 저장된 전자가 빠져나가지 못하게 그리고 tunneling 된 전자가 floating gate를 넘어가지 않도록 막아주는 (blocking) 역할을 합니다.

- Control gate: 외부 도선과 직접적으로 연결된 gate로 이 gate에 인가되는 전압의 level에 따라 memory cell이 활성화(ON) 되거나 쓰기모드 (Program)로 작동하거나 지우기모드 (Erase)로 작동합니다.

- Floating gate의 존재 덕분에 한 번 저장된 전자는 쉽게 밖으로 빠져나가지 않으므로 DRAM과 달리 NAND는 한 번 저장된 정보는 전원이 없어도 사라지지 않는 non-volatile memory입니다.

1.2. 심화 :: NAND Memory Array

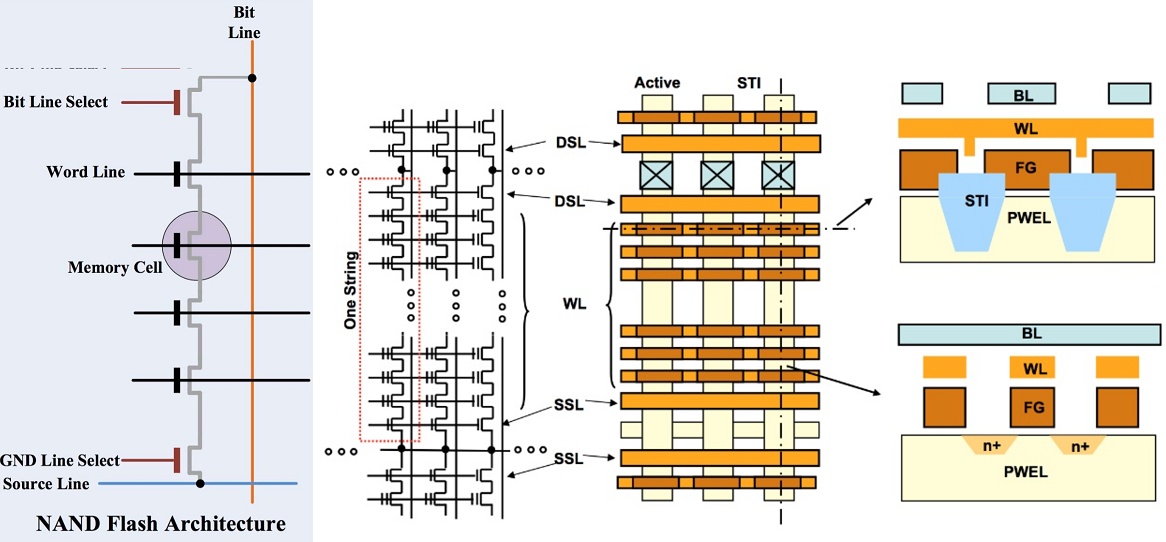

- 상단의 그림은 단일 memory cell이 직렬로 수십 개 연결된 형태의 memory array의 구조와 NAND flash 전체 구조에 대해서 설명하는 그림입니다..

- DRAM과 비슷하게 NAND에는 Bit Line (BL)과 Word Line (WL)을 통해 각 page 단위로 READ 하거나 WRITE 합니다. 용어를 잘 알아두세요.

- Cell이 여러 개가 직렬로 연결된 구조를 NAND string이라고 부릅니다. 그리고 여러 string이 차곡차곡 옆으로 정렬되어 있을 때 동일한 WL을 공유하는 집합을 1-page 라고 부릅니다. (제품마다 그 용량은 상이하지만 일반적으로 'Page'는 약 4KB입니다.)

- String의 양 끝에는 SSL (String Select Line)과 GSL (GND Select Line)이라는 이름의 WL이 있습니다.

- 결과적으로 NAND의 READ-WRITE-ERASE operation은 SSL(또는 DSL), GSL, BL 그리고 WL 이 4가지 라인에 어떠한 전압을 인가하느냐에 따라 약속된 기능을 수행합니다.

2. NAND의 작동 원리

NAND의 memory cell은 control gate에 인가해주는 전압의 특성에 따라 3가지 상태를 가집니다.

2.1. Activate mode

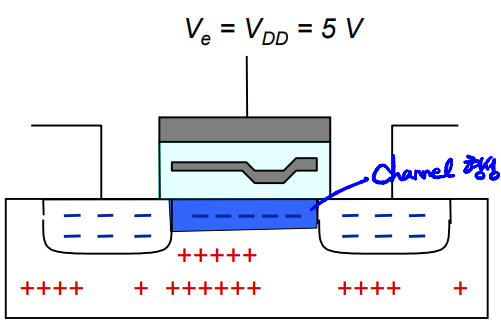

- Activation mode는 gate 전압 에 의 전압을 인가했을 때 source와 drain 사이에 channel이 형성되어 전류가 통하게 되는 때를 말합니다.

- 이 mode에서는 floating gate 내부에 있는 전하의 존재 여부에 따라 channel에 전류가 통할 수도, 통하지 않은 수도 있기 때문에 '읽기(read)연산'을 할 때 사용합니다.

- 만일 floating gate에 전자가 tunneling 되어 programmed 됐다면 channel이 정상적으로 형성되지 않아서 전류가 통하지 않습니다.

따라서 를 인가했는데 전류가 감지되지 않는다면 이 memory cell에는 정보가 저장되어있음을 알 수 있습니다.

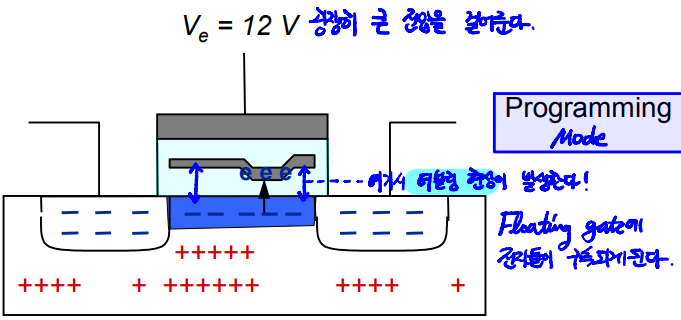

2.2. Programming mode

- 이번에는 gate에 굉장히 높은 전압 을 걸어봅시다.

- 형성된 channel 사이를 이동하는 전자는 tunneling 현상 덕분에floating gate로 이동할 수 있게되고 한 번 floating gate에 들어온 전자는 구속됩니다.

- 이렇게 floating gate에 구속된 전자는 gate 전압이 끊겨도 정보를 저장할 수 있는 volatile한 NAND의 특성을 가질 수 있도록 해줍니다.

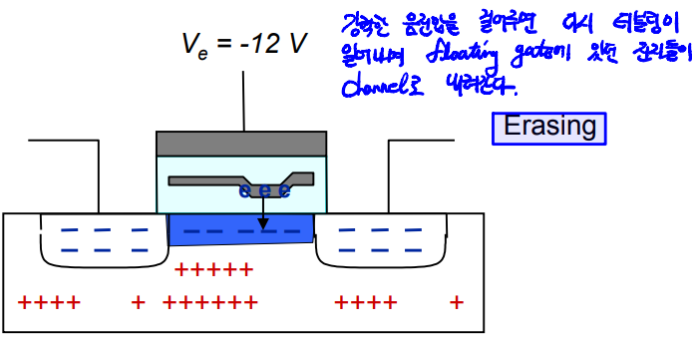

2.3. Erase mode

- 마지막으로 이번에는 gate에 굉장히 높은 음전압 를 걸어봅시다.

- Program mode와 반대 방향으로 channel이 형성되면, 이번에는 역방향 tunneling이 발생하고 floating gate에 있던 전자들이 substrate로 빠져나갑니다.

- 결국 memory cell에 내장된 정보는 사라지게 됩니다.

3. NAND의 종류

3.1. NAND의 종류

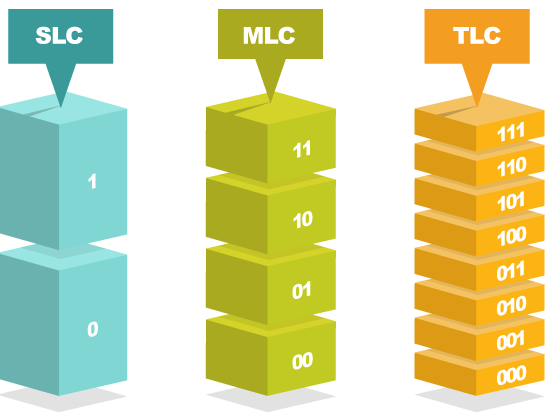

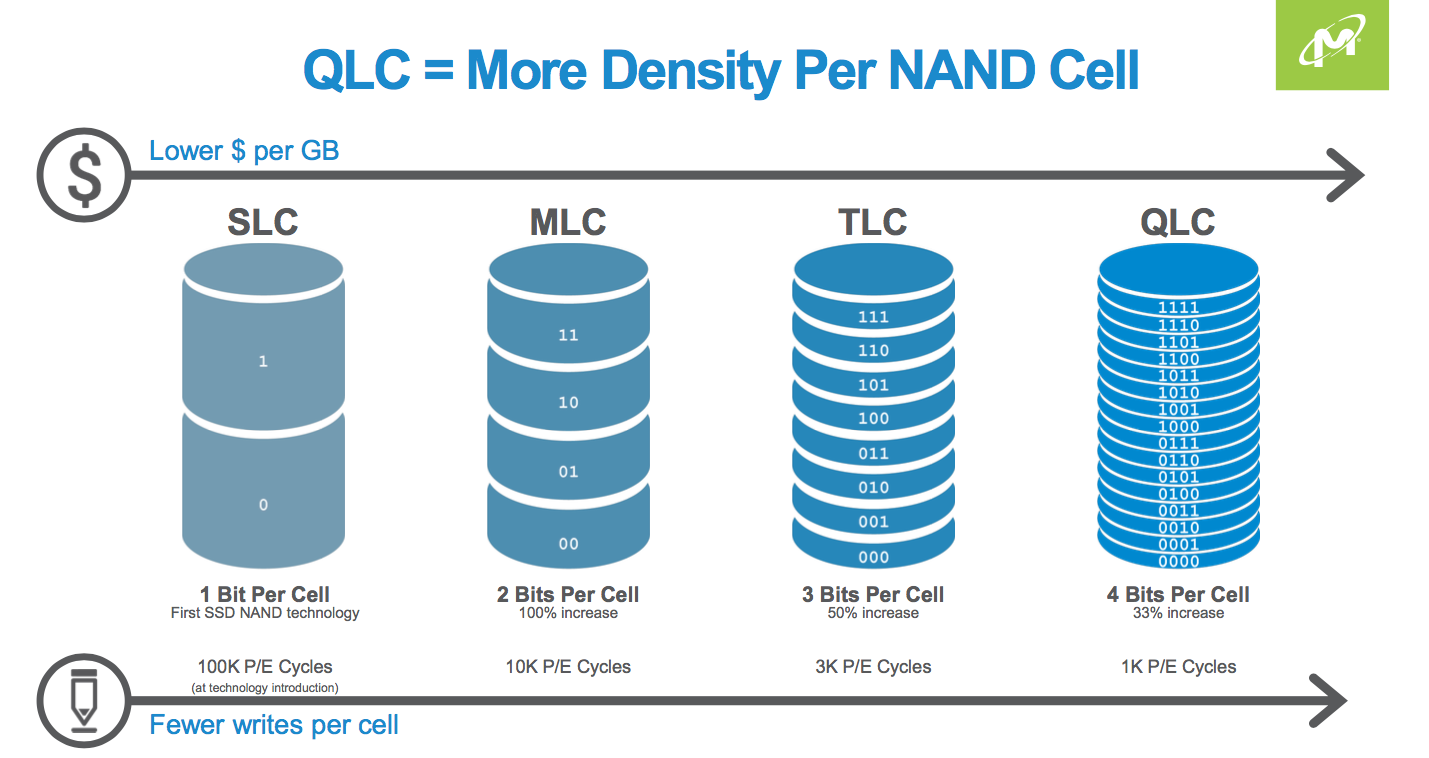

- NAND는 하나의 memory cell에 저장하는 data의 bit 수에 따라 네 가지 종류로 나뉩니다.

- SLC (Single Level Cell): 하나의 memory cell이 오직 1bit (개 상태)를 가지고 있는 구조입니다.

- MLC (Multi Level Cell): 하나의 memory cell이 2bit (개 상태)를 가지고 있습니다.

- TLC (Triple Level Cell): 하나의 memory cell이 3bit (개 상태)를 가지고 있습니다.

- QLC (Quad Level Cell): 하나의 memory cell이 4bit (개 상태)를 가지고 있습니다.

3.2. 각 종류의 특징

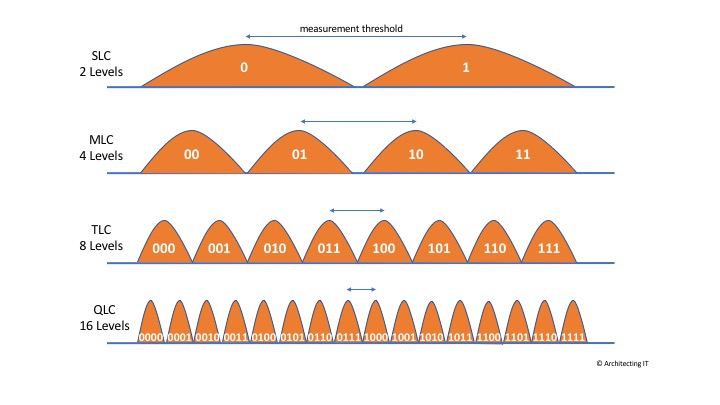

- 단일 cell에 저장된 상태가 적을수록 한 번의 동작으로 data를 명확하게 식별할 수 있습니다. 그러므로 속도 측면에서는 SLC가 가장 빠릅니다.

- 또한 단일 동작으로 data access가 가능함은 곧 cell의 capacitor에 저장되는 전자들의 이동횟수가 적어진다는 의미이므로 NAND의 수명도 SLC가 가장 높습니다.

- 하지만 단일 cell을 여러 상태로 구분할 수 있다는 것은 곧 대용량화가 가능하다는 의미입니다. SLC에 비해 상대적으로 속도도 느리고 수명도 짧더라도 대용량 스토리지가 기존 HDD에서 SSD로 바뀌고 있는 방향을 고려하면 TLC와 QLC도 충분히 시장성이 높습니다.

3.3. 심화

위 두 절을 읽으신 여러분은 두 가지 의문이 생기셨을 것입니다.

- 단일 cell에 capacitor는 하나인데 어떻게 여러 상태를 구분할 수 있을까?

- 왜 cell의 상태를 여러 개로 구분하면 수명이 떨어지게 될까?

3.3.1. 상태 구분 방법

- 위 사진은 SLC, MLC 그리고 TLC의 상태 구분도를 간략하게 보여주는 그림입니다.

- 일반적인 SLC라면 gate에 인가되는 총 전압 이 문턱전압 를 넘을 경우 2.1절의 mode에서 floating gate에 저장된 전자의 양에 따라 channel이 받는 영향을 통해 '1'과 '0'을 구분합니다.

- 즉, 다시 말하면 program mode에서 gate에 인가되는 총 전압 의 크기에 따라 floating gate에 저장되는 전자의 양이 달라지는 것을 응용해서 하나의 memory cell에 여러 정보를 저장합니다.

- MLC도 동일한 방법으로 정보를 구분하되 정보와 정보 사이의 폭을 2배로 촘촘하게 만들어서

00(전자 적음), 01(전자 조금 있음), 10(전자 꽤 있음), 11(전자 개많음)으로 구분하게 됩니다. TLC는 이것보다 2배 더 많은 8개의 정보를 저장합니다. - 하지만 floating gate에 저장되는 전자의 양을 통해 정보를 구분하는 NAND memory cell의 특성 상 단일 operation만으로는 정확하게 각 정보를 구분짓기 힘들었기 때문에 2~4단계의 작업을 거치면서 정보를 파악합니다.

- 결과적으로 단일 operation 만으로 data를 읽을 수 있는 SLC보다 수 차례 더 operation을 수행해야만 data를 읽을 수 있는 MLC, TLC, QLC가 필연적으로 더 느립니다.

3.3.2. NAND cell의 수명

- NAND의 memory cell은 P/E cycle이라 불리는 '수명' 개념을 가지고 있습니다.

- 일반적으로 memory cell은 더 이상 floating gate에 전자를 수용할 수 없는 상태가 될 때 해당 cell을 '고장이 났다', 또는 '수명이 다했다'고 표현합니다.

- Floating gate에 전자를 저장하는 원리 tunneling은 tunneling oxide를 전자가 물리적으로 뚫고 지나가는 방식으로 이뤄집니다.

- 이 과정에서 oxide는 필연적으로 손상을 입게되고 READ, WRITE 횟수가 늘어날수록oxide 손상도 심해집니다.

- 결론적으로 oxide가 손상되면 더 이상 channel로부터 tunneling이 일어나기 어려워지므로 해당 cell은 더 이상 유효한 정보를 저장할 수 없는 고장난 cell이 됩니다.

Q. MLC, TLC, QLC로 갈 수록 수명이 줄어드는 이유는 뭔가요?

A. 우리는 위에서 floating gate에 저장된 전자의 양으로 data를 구분한다고 배웠습니다. 따라서 하나의 cell이 담는 bit 수가 많아질수록 data와 data 사이의 전자양을 구분하는 폭이 좁아지게 됩니다. 만일 oxide가 손상돼 floating gate에 저장되는 전자의 양에 차이가 생긴다면 QLC로 갈수록 받는 영향이 커질 수 밖에 없습니다. 게다가 공정이 미세화 될수록 가뜩이나 커지는 영향력이 증폭됩니다. 따라서 QLC로 갈수록 cell의 수명은 짧아질 수 밖에 없지요.

3.3.3. NAND 수명 연장 방법

NAND memory cell의 수명을 연장하기 위해 많은 연구가 진행되고있는데 오늘 소개할 방법은 총 3가지가 있습니다.

- Wear leveling (웨어레벨링)

- WRITE/ERASE가 특정 memory cell에 집중해서 발생한다면, 해당 cell은 금방 수명을 다하고 고장난 cell이 될 것입니다.

- 따라서 NAND를 오랫동안 사용하기 위해서는 최대한 전체 cell을 골고루 사용해야 합니다.

- Wear Leveling은 외부 controller가 맡아서 수행하게 되며, WRITE/ERASE가 특정 NAND 부위에 집중되지 않고 여러 부위에 분산되게끔 만들어주는 방법입니다.

- ECC (Error Check and Correct, 에러 검출 및 수정)

- ECC는 높아지는 집적도로 지나친 feature size의 줄어듦과 cell-to-cell interference 때문에 발생한 NAND의 신뢰도 문제를 해결하고 retenction과 endurance를 확보하기 위해 사용되는 컨트롤러의 에러 수정 기능입니다.

- ECC에서 사용하는 신뢰성 척도는 시스템의 요구 신뢰성을 의미하는 UBER (uncorrectable bit-error rate)와 data 자체의 오류 수준을 의미하는 RBER(raw bit-error rate)이 있습니다.

- SSD가 대용량 스토리지 시장에서 HDD를 대체하게 되면서 TLC, QLC가 채택되는 경우가 많아지며 이전에는 4-bit 정도의 ECC면 충분했지만 이제는 24-bit 이상의 ECC가 필요할 정도로 ECC의 요구 정밀도도 높아지고 있습니다.

- Over Positioning (오버포지셔닝)

- Over positioning은 일부 NAND memory cell (SSD 전체 용량의 약 8~25%)을 의도적으로 사용하지 않는 부분으로 놔둔 뒤 cell이 죽을 때 이 포지셔닝 된 공간에서 가져다 사용해서 제품의 수명을 높히는 기술입니다.

- Over positioning은 garbage collection을 위한 예비 buffer 용도로도 사용되고는 합니다. 자세한 내용은 https://velog.io/@embeddedjune/Coding-for-SSD-정리-및-요약 에서 확인하실 수 있습니다.