7.1. Introduction

어떻게 CPU의 성능을 객관적으로 측정할 것인가?

- 주어진 복잡하고 많은 instruction을 얼마나 빠르게 컴파일하는가?

- 한 instruction을 수행하는 데 얼마나 많은 cycle이 필요한가? (CPI)

-

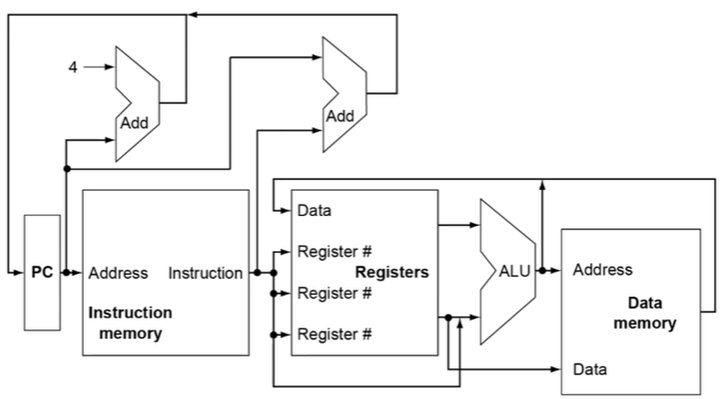

Instruction을 수행하기 위해 operands를 꺼내오는 과정을 도식화한 그림이다.

PC값이 가리키는 주소를Instruction Memory에 넣으면 다음에 수행할 instruction을 알 수 있다.- Instruction의 operand인

rs에 저장된 번호들을Registers에서 꺼내온다. Data memory에서 register에 저장된 value를 꺼내온다.

-

우리는 이번 시간에 위 도식화 된 그림에 대해서 배워볼 것이다.

7.2. Logic Design Convention (사전지식)

- Low voltage =

0, High voltage =1로 맵핑된다. - 하나의 wire는 당연히 하나의 bit를 담고, 여러 bit는 wire 다발 (array)로 표현된다.

- 모든 요소는 Combinational element와 Sequential element로 나뉜다.

- Combinational은 AND, OR, MUX, DEC … 등 주어진 input에 대해 정해진 logic에 따라 output을 단순 출력하는 소자를 말한다.

- Sequential은 retch, flip flop (F/F’), register같이 임의의 data를 저장하는 능력을 가지고 있고, 저장된 data를 다음 연산에 활용하는 소자를 말한다. Edge triggered 방식으로 작동하며, CLK이 high 또는 low로 바뀔 때 약간의 propagation delay (setup and hold time) 이후 결과값이 출력된다.

- Combinational elements의 속도 (clock period)는 critical path의 worst delay로 결정된다.

이 속도를 빠르게 만들어서 previous sequential에서 next sequential로 넘겨주도록 설계해야 한다.

7.3. Datapath와 과정

Data가 어디서 어떤 경로로 움직이는지를 나타낸 경로를 datapath라고 한다. Fetch 및 operation execution은 input 값들과 control signal의 조합으로 이뤄진다. 7.1절의 그림을 한 부분씩 차례대로 보도록 하자.

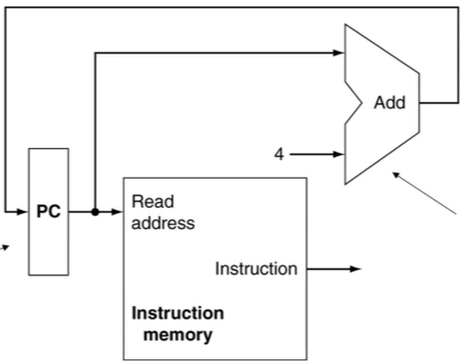

7.3.1. Instruction fetch

- 다음에 수행할 instruction을 fetch 하는 과정이다.

PC에 저장된 값이 instruction이 저장된 memory의read부분으로 들어가면, 해당하는 instruction이 반환된다.PC값을 늘려주기 위해ADD연산기에 상수4를 항상 넣어놓고PC를PC + 4로 만든다. 이 결과는 다음 rising edge때 반영될 것이다.

7.3.2. R-Format instruction

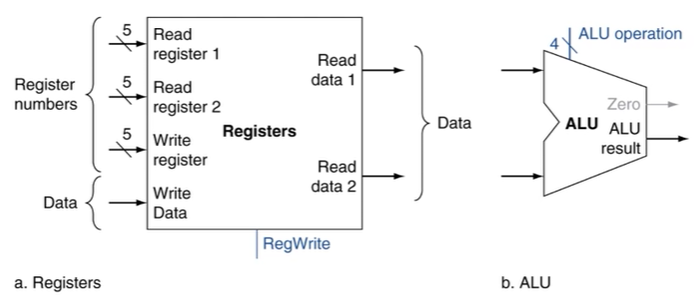

Registers (Operand와 data를 가지고 오기 위한 과정)

- Operand인

rs1과rs2를Read register 1, 2에서 읽는다. - Destination인

rd를Write register에서 읽는다. Write data는rd에 들어있는 data를 말한다. 이 data는Read data 1, 2로 나간다.- Read는 언제나 해도 되지만, Write는 요청이 들어올 때만 해야한다. 안그러면 원치않는 timing에 register에 이상한 값이 쓰여서 엉망이 되기 때문이다.

- 위 문제를 막기 위해 control signal인

RegWrite를 사용한다.

High일 때Write register앞에서 대기중인 register 번호가 들어간다.

ALU (가져온 data들로 연산을 하기 위한 과정)

-

ALU는

Read data 1, 2를 두 입력으로 받아 연산을 수행하고result를 반환한다. -

연산을 결정하는 것은 4-bit 짜리

ALU Operation코드이다. -

Zero는beq명령어를 위해 사용하는 signal인데, 일단 이 R-format 에서는 활용하지 않는다.

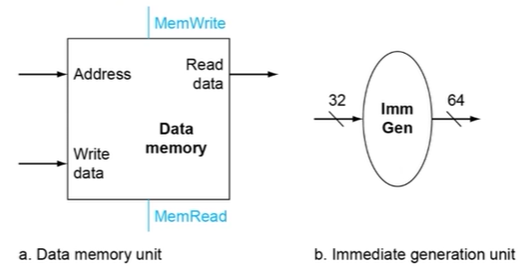

7.3.3. Load-store Instructions

- Load할 경우에는

Address로 들어온 memory의 주소 안에 들어있는 value를 register에 저장한다. - Store할 경우에는

Write data로 들어온 register value를Address로 들어온 memory 주소 안에 저장한다. - 이 과정을 control하는 게

MemWrite과MemReadsignal이다.

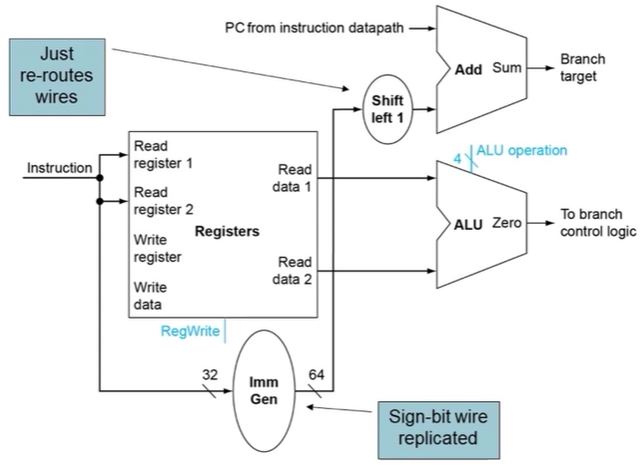

7.3.4. Branch Instruction

예를 들어 beq rs1, rs2, Label 이라는 명령을 수행한다고 가정하자.

Read register 1, 2가 지정한 registers 안의 data를Read data 1, 2로 반환한다.- 이 값들은 각각 ALU로 들어가 뺄셈 연산을 수행하게 되고

Zero핀으로0인지 아닌지 확인한다.- 만일

0이라면 branch를 빠져나와서 정상 flow로 프로그램이 실행된다.

- 만일

- 만일

0이 아니라면, Instruction의 하위 32-bit를 1칸 왼쪽으로 shift해서 64-bit로 만든 뒤 branch할 target 주소를 확보한다. 이 주소가Label의 주소다.

-

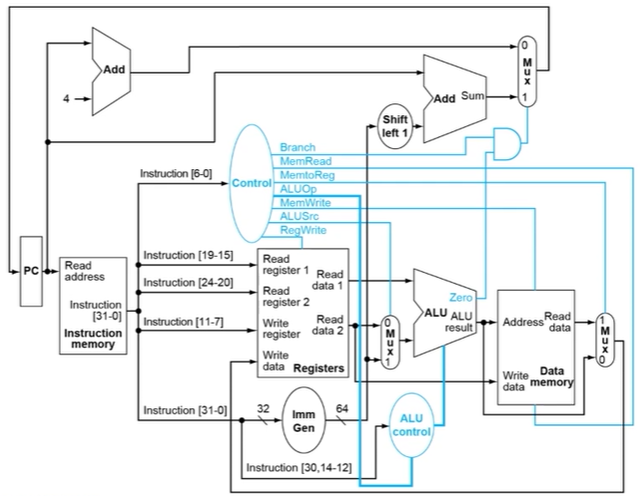

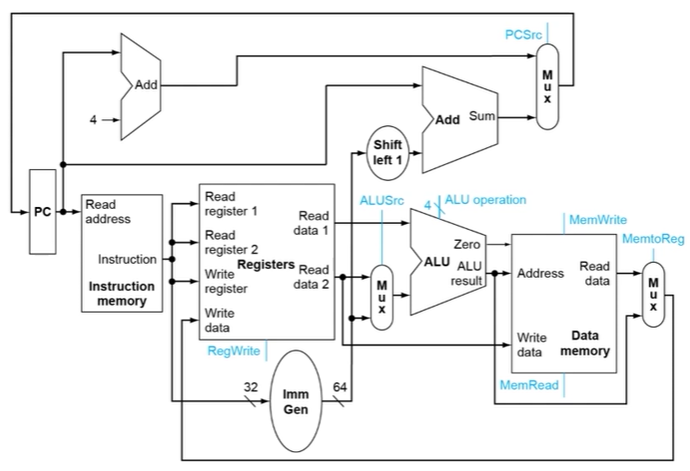

지금까지 배운 내용을 하나로 합치면 위와 같은 그림이다.

-

Datapath가 겹치는 부분이 필연적으로 생기는데, 2x1 multiplexer를 넣어서 두 input 중 하나만 선택한다.

- 예를 들어, 가운데 MUX는

Read data 2를 선택하거나immediate상수값을 선택하거나 한다. - 아무래도, R-format일 때는

Read data 2를 선택할 것이고 I-format일 때는 상수값을 선택할 것이다. - 이것을 결정하는 control signal이

ALUSrc이다.

- 예를 들어, 가운데 MUX는

-

우리는 이번 시간을 통해, 명령어를 수행하기 위해서는 어떤 하드웨어 모듈(logical block)이 사용되는지 배웠다. 그 과정에서 data path와 control path 그리고 control signal이 무엇 무엇이 사용되는지 이해할 수 있었다.

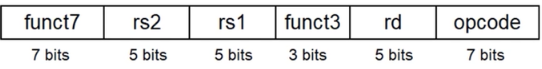

7.4. ALU Control bits

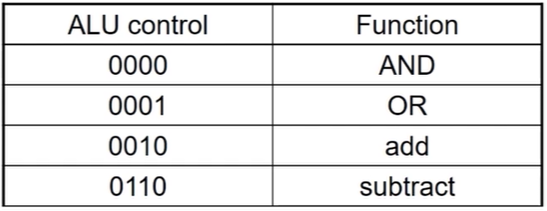

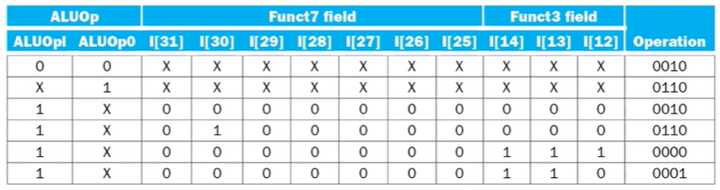

우리는 앞서 ALU에 control bit가 operation을 결정한다고 배웠다.

단순히 ALU 연산 뿐만 아니라, R-format, I-format, S-format 등 다양한 연산에서 ALU를 활용하게 되는 것 또한 배울 수 있었다. 이번에는 ALU의 control bit 4-bit가 어떻게 형성되는지 알아보자.

Instruction에 주어지는 opcode에서 우리는 2-bit 짜리 ALUOp 라는 정보를 얻을 수 있다.

- opcode가

ld또는sd명령어일 때,ALUOp == 00이며 ALU control bit는0010=add연산이다. - opcode가 R-type일 때,

ALUOp == 1x이며Funct3, 7의 값에 따라 control bit가 변한다.

최종적으로 ALU control bit까지 적용된 그림은 아래와 같다.