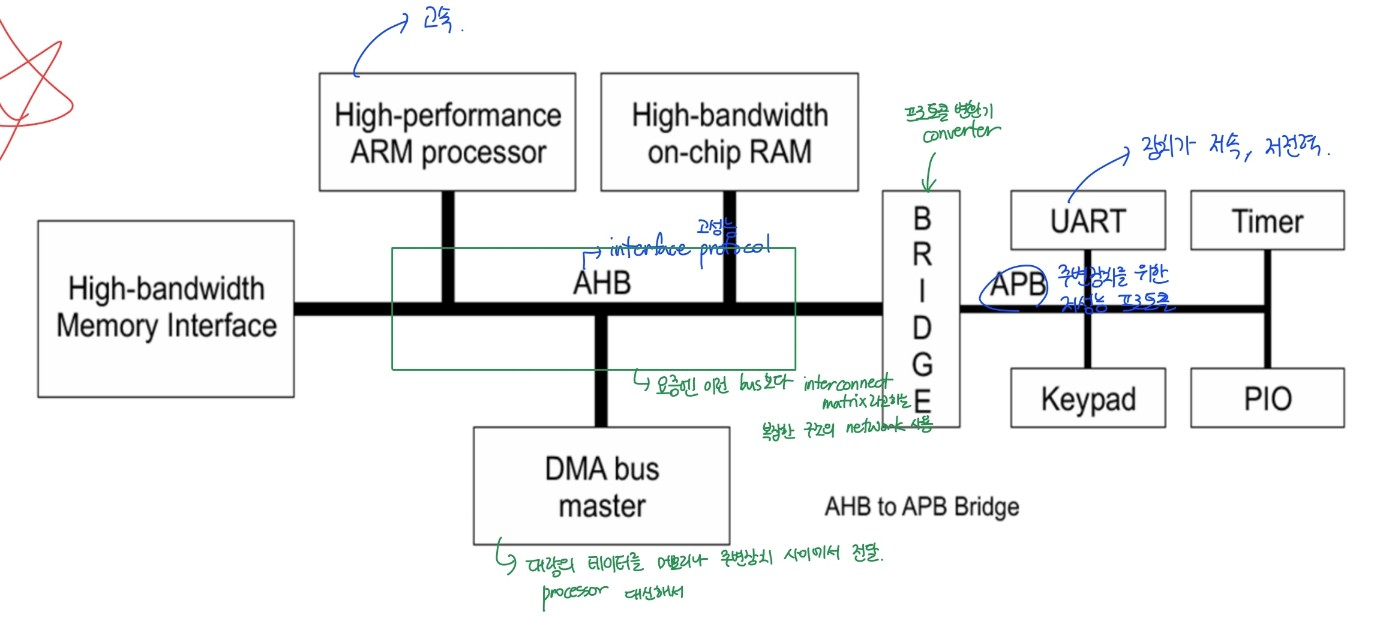

Overview of the AMBA specification

- 보편적인 AMBA 기반 마이크로컨트롤러

- 고속으로 동작하는 ARM processor와 연결된 bus는 AHB 사용(AHB : 고성능 interface protocol)

- DMA bus master : 프로세서를 대신하여 대량의 데이터를 메모리나 주변장치 사이에서 전달

- bridge : protocol 변환기

- 주변장치는 저속, 저전력으로 동작하므로 APB interface protocol 사용

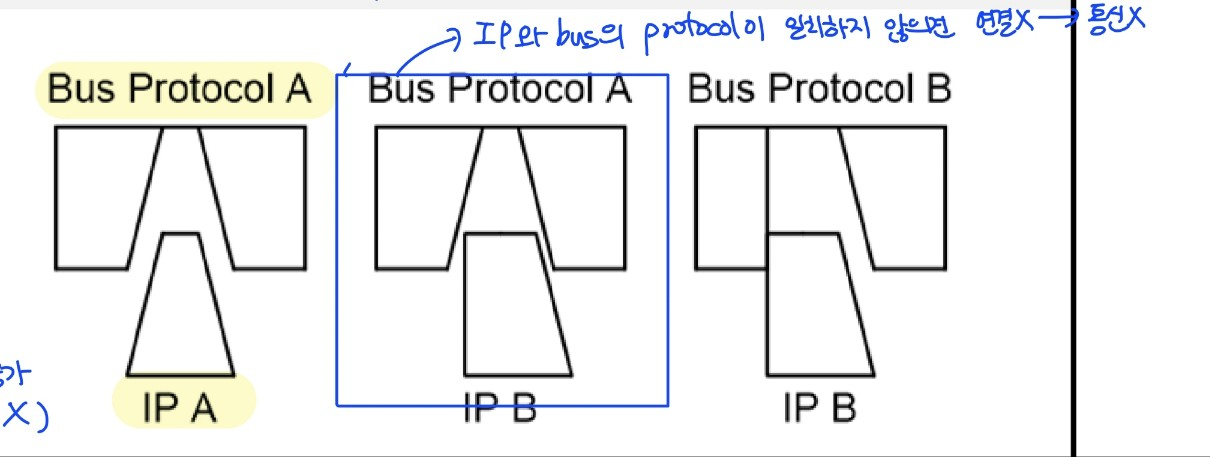

Why do we need Bus?

- chip에는 많은 IP block들이 있음 (IP : 프로세서와 메모리같은 장치 하나하나를 의미)

- IP block들은 On-chip 통신을 함

- IP와 bus의 protocol이 일치하지 않으면 연결이 안 되어 통신이 되지 않음

- 모든 IP들이 사용하는 protocol과 network이 사용하는 protocol이 같아야 원할한 통신 가능

-

Dedicated interconnection lines

- 32bit architecture, 4 IPs : 32bit 6 2 = 384bit

- IP들의 수가 많아지면 더욱더 많은 bit가 필요

-

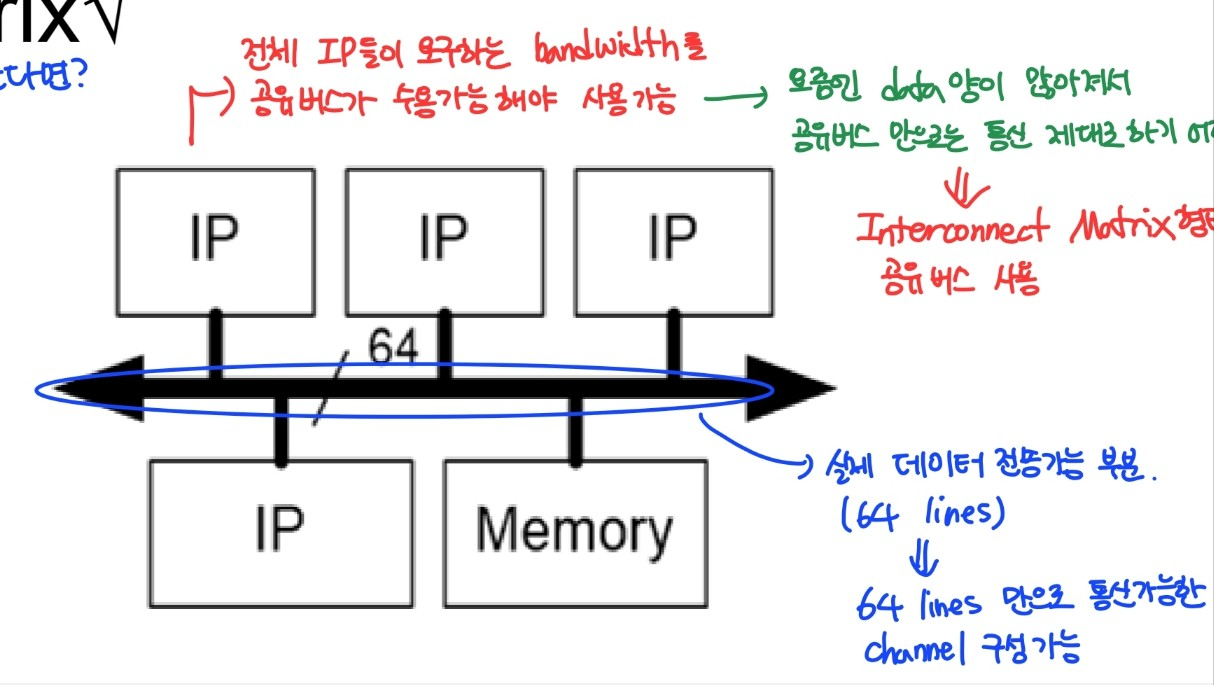

Shared bus

- 공유 버스를 사용하면 연결선이 크게 감소함

- 64 bit

- 부작용

1. 한번에 하나의 통신만 가능

- 하나의 IP가 데이터를 내보내면 다른 IP가 데이터를 받는 방식

2. IP의 I/O가 system bus를 따라가야해

3. 전체 IP들이 요구하는 bandwidth를 공유버스가 수용 가능해야 사용 가능

-

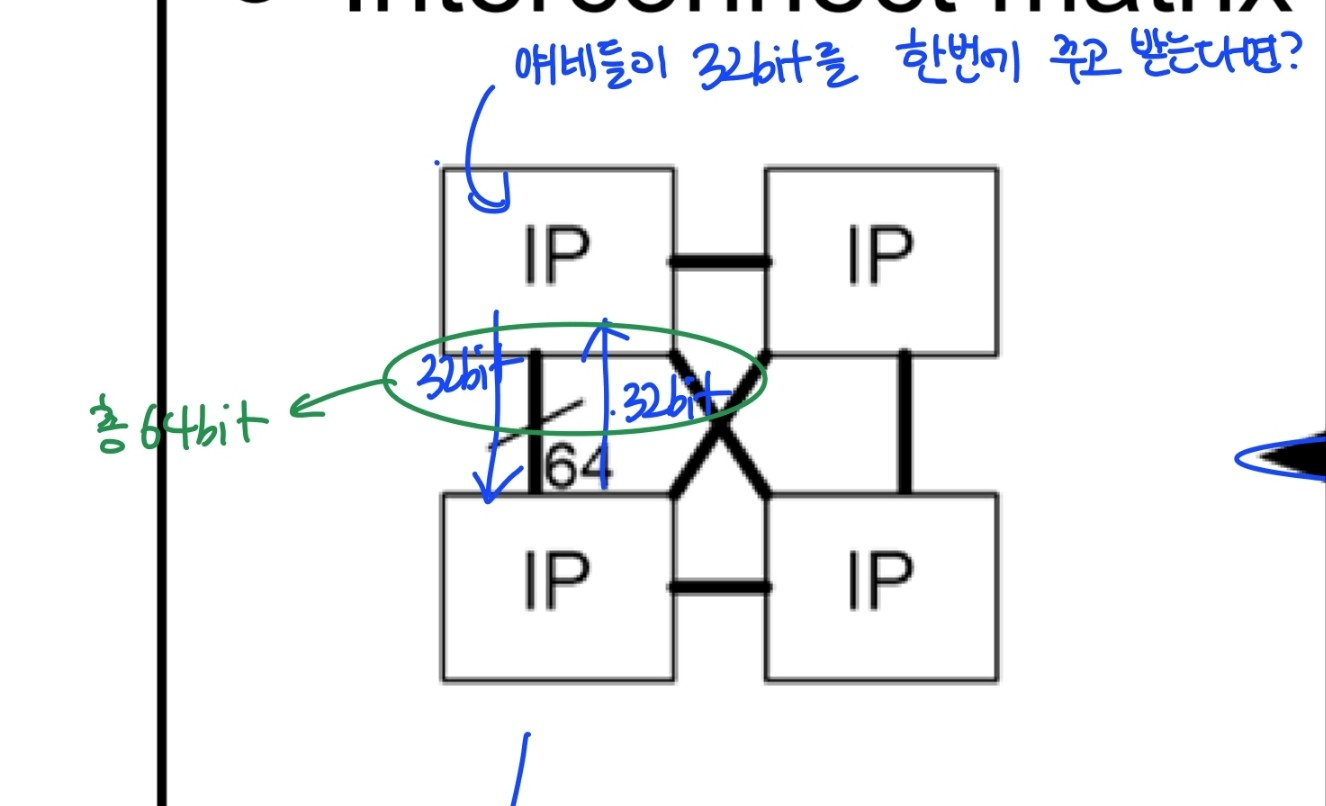

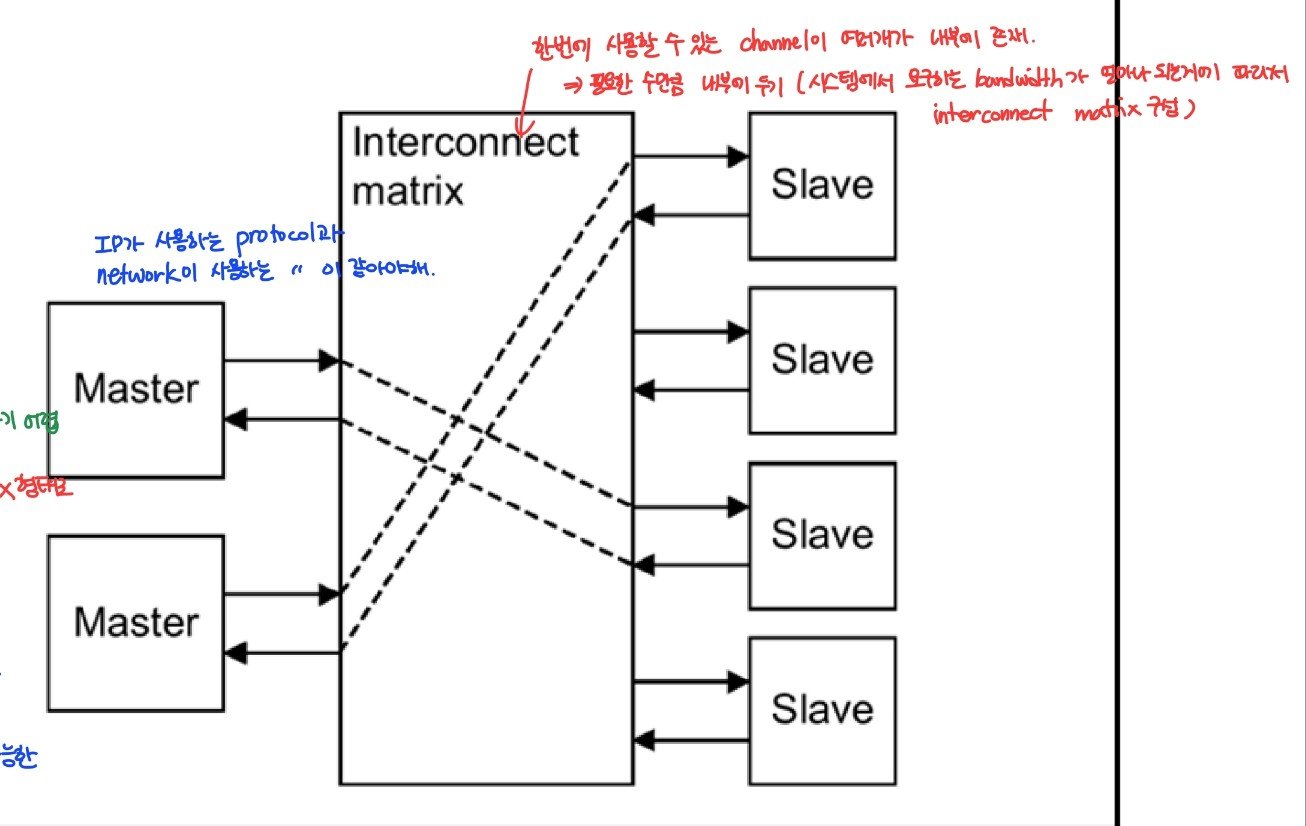

Interconnect matrix

- shared bus의 경우 한번에 하나의 통신

⇒ 요즘엔 data의 양이 많아져서 공유버스만으로는 통신을 제대로 하기 어렵

⇒ Interconnect Matrix 형태로 공유 버스 사용

- channel : data를 물리적으로 전송할 수 있는 전송선(bus와 동일한 개념)

- 한번에 보내고자하는 data의 bit 수에 맞는 line들의 집합(data 뿐만 아니라 제어신호도 같이 움직여야 해)

- interconnect matrix는 channel 여러개가 내부에 존재

⇒ 필요한 수만큼 내부에 두기

- 시스템에서 요구하는 bandwidth가 얼마나 되는지에 따라 interconnect matrix가 구성됨

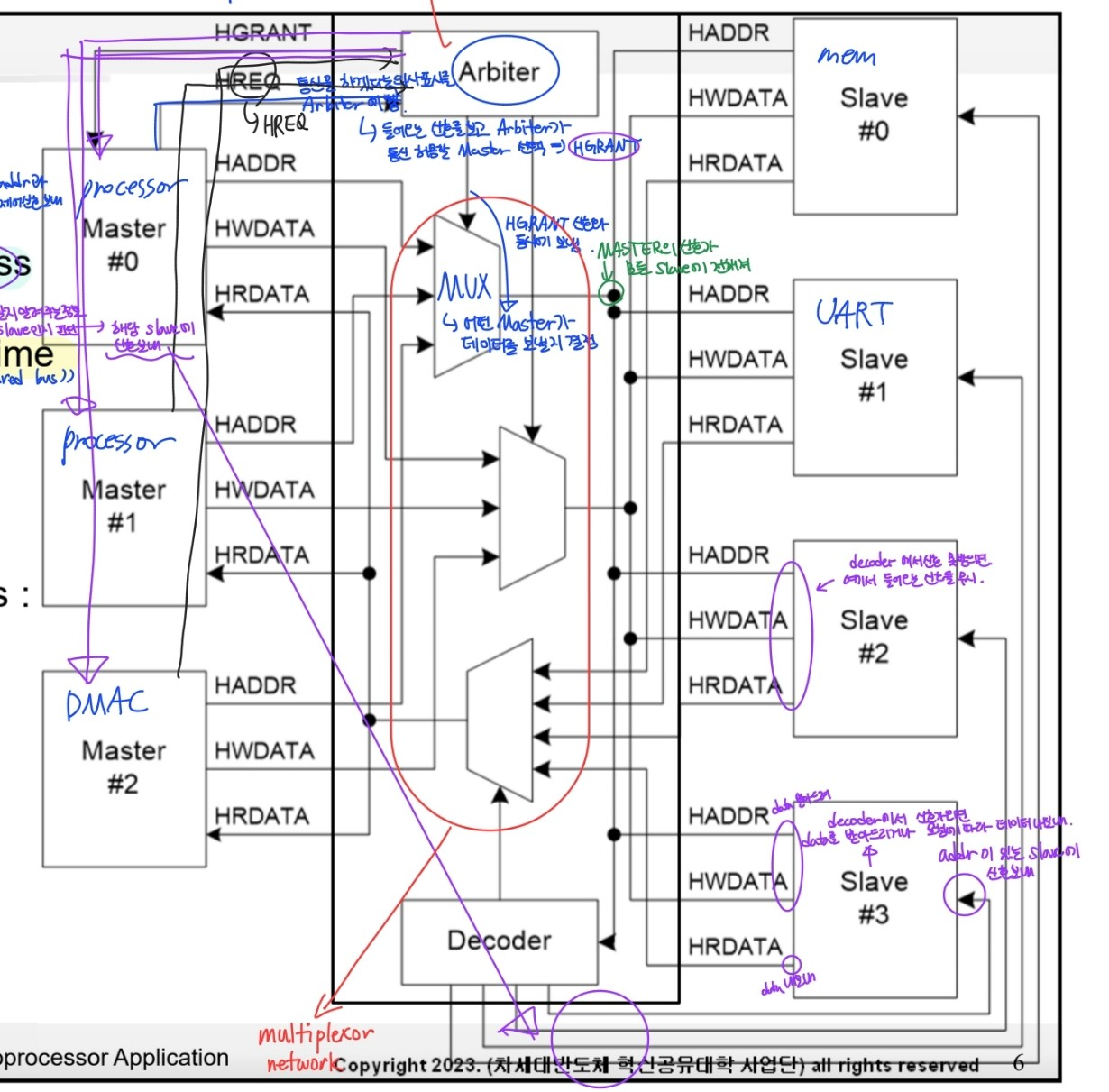

AMBA AHB Interconnection

- 3 AHB masters and 4 slaves interconnection

- AHB master(processor나 DMA등)

- 주소와 제어신호를 이용해서 read/write 동작을 실행

- address : 어떤 slave에 정보를 전달할 지 알려주는 정보

- 이 주소를 decoder가 받아서 어떤 slave인지 판단하고 해당 slave에 신호를 보내

- AHB slave

- decoder에서 신호가 오면 data를 받아드리거나 요청에 따라 데이터를 내보냄

- active master에 반응함(success, failure, waiting)

- AHB arbiter

- master는 arbiter에게 통신을 하겠다는 의사표시를 함(HGRANT 신호)

- 이 신호를 보고 arbiter가 통신을 허용할 master를 선택

- 여러개의 master 중에서 어떤 master가 통신할 수 있는지 알려주는 역할

- AHB decoder

- 주소 해독 후 slave에 신호를 보내는 역할

- Multiplexor network

- Physical channel

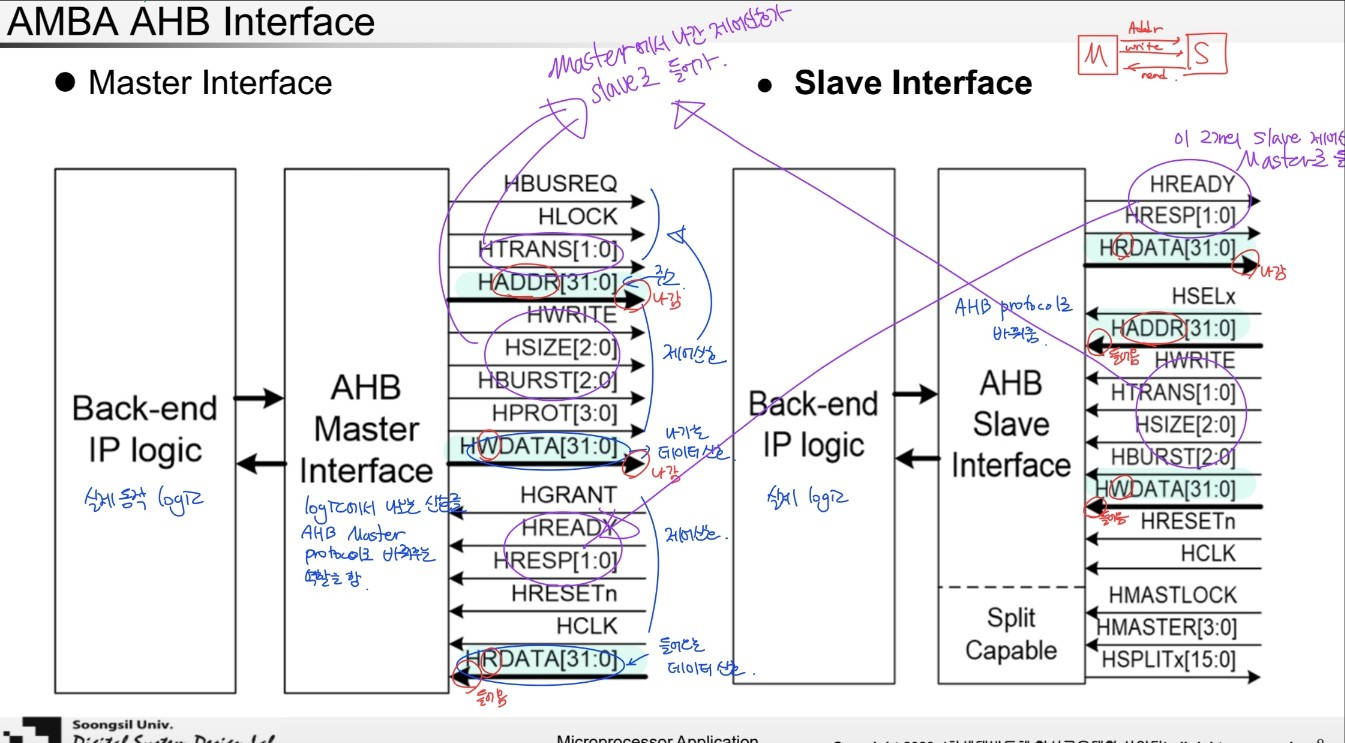

AMBA AHB Interface

- 각각의 IP에는 protocol를 바꿔주는 interface가 있음

- master 쪽에는 AHB Master Interface/slave 쪽에는 AHB Slave Interface

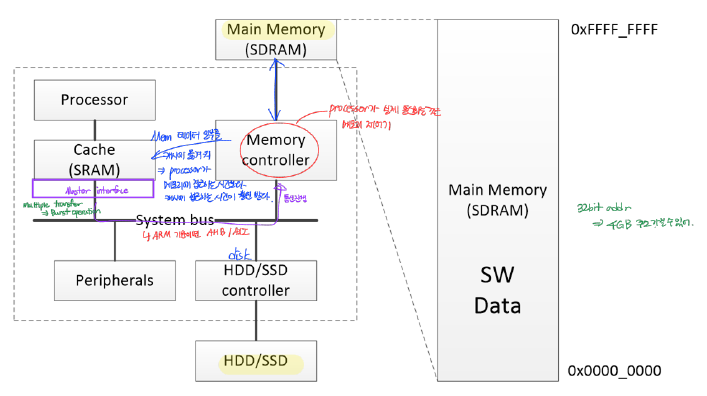

Processor and Memory

System architecture

- Cache(SRAM)

- memory 데이터의 일부를 cache에 옮겨두면 processor가 메모리에 접근하는 시간보다 캐시에 접근하는 시간이 훨씬 빠름 - Memory controller

- 얘가 메모리의 데이터를 캐시로 옮김 ⇒ multiple transfer ⇒ burst operation

- 프로세서와 실제로 통신하는 IP

- 프로세서가 필요한 데이터를 메모리에서 캐시로 옮김

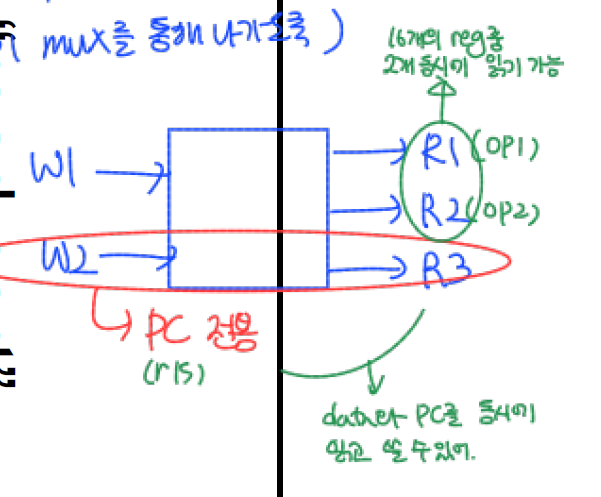

Register File

- register는 CPU가 제일 자주 사용하는 메모리

- ARM : 16*32-bit registers

- 32bit data to write/ read data : data 송수신

- 4bit write address/ read address : register address

- write/read port가 별도로 존재 ⇒ read/write 동시 진행 가능(조건 : 같은 register에서 read/write 해야함)

- 아래 사진은 ARM의 register bank 형태

- read port 2개/ write port 1개 (for data)

- read port 1개/ write port 1개 (for pc)

Cache

- 메모리에 있는 자주 사용하는 data를 복사해서 프로세서가 빠르게 데이터를 읽고 쓸 수 있도록 함

Validity of cache

- Locality : 일정 시간동안 메모리의 한정된 부분에 자주 접근

- Spatial Locality : 메모리의 특정 정보가 필요할 때, 그 데이터 주변의 데이터들도 곧 필요하게 됨.

- Temporal Locality : 메모리의 특정 정보가 필요할 때, 그 데이터 주변의 데이터들도 곧 필요하게 됨.

Cache access

Cache level

- L1 - (L2) - (L3) - Main memory(DRAM)

- L1 - Main memory(DRAM)

Cache hit/miss

- Cache hit : cache 안에 원하는 data가 있을 때

- Cache miss : cache 안에 원하는 data가 없을 때

⇒ 메모리에서 data block들을 읽어옴

(cache controller(or MMU)가 진행/processor 동작 멈춤/register file에 있는 정보들은 유지됨)

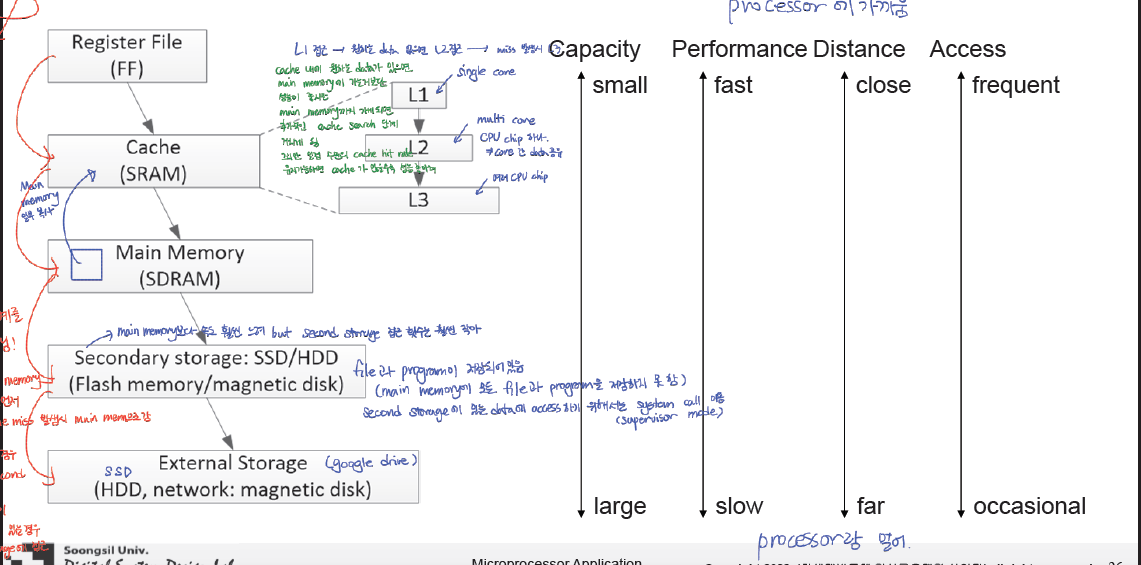

Memory hierarchy

- L1 → (L2) → (L3) → Main memory(DRAM) 방향으로 data 찾으러 다님

- 캐시 내에 원하는 data가 있으면 main memory 접근 횟수가 줄기 때문에 성능이 좋지만 main memory까지 가게 되면 추가적인 캐시 찾는 단계를 거치게 됨

→ 일정 수준의 cache hit rate를 유지할 수 있으면 cache가 많을수록 좋음 - second storage는 많이 느리지만 main memory보다 접근 횟수가 현저히 적다

- second storage에는 file과 program이 저장되어 있음- second storage에 접근하기 위해서는 main memory에 있는 system call를 이용해야해(supervisor mode)

- external storage도 마찬가지

- 항상 모든 메모리를 거쳐 low level 메모리로 가는게 아님

- 캐시와 메모리의 경우 순차적으로 이동하면서 원하는 data를 찾지만

- second storage의 경우 처음부터 data나 program이 second storage에 있을 때 처음부터 second storage에 접근

Memory Management

Memory Space

- 32bit CPU or 32bit OS → 2^32 = 4GB main memory

- 64bit CPU or 64bit OS → 2^64만큼의 byte 가질 수 있지만 64bit addr space 다 사용X

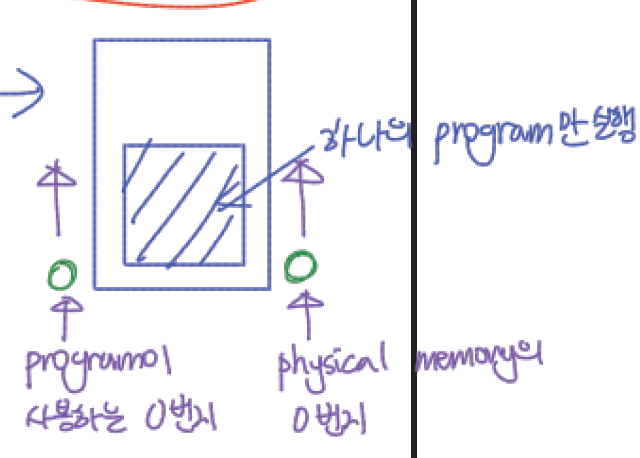

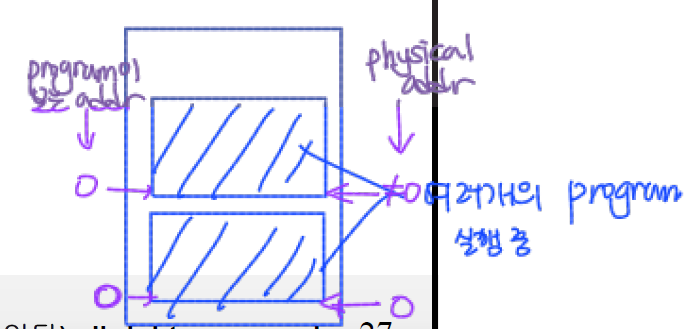

Logical address

- logical address : program에서 사용하는 주소

- program 상에서 보이는 주소- program 명령어에 포함된 주소 값

- single processor/single process(program)인 경우

- logical address = physical memory

- logical address = physical memory

- single processor/multiple processes or multiple processors

- single program with OS도 이에 해당됨

- logical address =/= physical memory

- 프로그램을 실행할 경우 프로그램의 logical address를 physical address로 변환해야함

- physical memory는 가질 수 있는 최대 memory space보다 작아야함.

- 32bit CPU라면 physical memory는 최대 4GB까지 가질 수 있음 - Virtual memory는 주로 secondary storage로 구성됨

1. physical memory가 max memory space보다 작은 경우- 실행돼야하는 program 수가 굉장히 많을 때

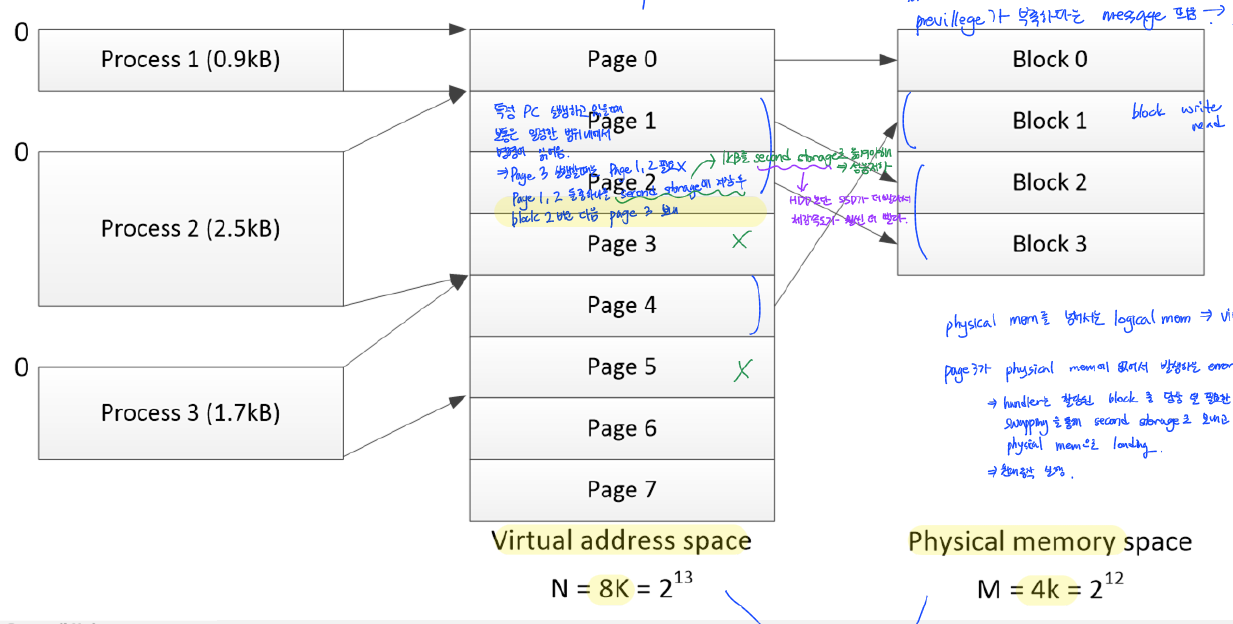

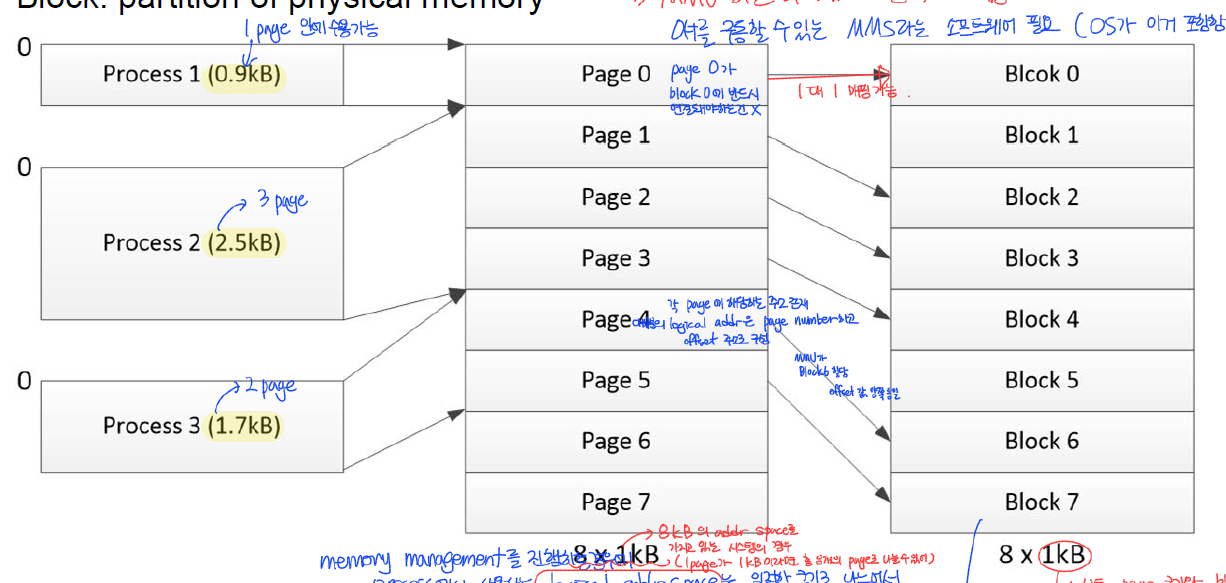

Address mapping using page

Page

- logical address space의 부분

Block

- physical memory의 부분

Memory management

- logical address를 physical address로 변환

- address의 유효성을 검증

⇒ MMU라는 하드웨어 장치가 해줌

- 보통 page의 크기와 block의 크기는 같음

- 각 page에 해당하는 주소가 존재(logical address는 page number와 offset 주소로 구성됨)

- MMU가 page를 block에 할당함

- page0가 block0에 반드시 연결되어야 하는 것은 아님

Address mapping in virtual memory

virtual address space

- physical memory를 넘어서는 logical memory → virtual address space

- virtual address space : 8K / physical address space : 4K 인 경우

⟹ logical address와 physical address를 1대1 mapping 불가

(메모리에 올라와 있는 page는 현재 사용하고 있는 모든 process를 다 수용 불가)

page fault

- page3가 physical memory에 없어서 발생하는 error : page fault

- 특정 PC 실행하고 있을 때 보통은 일정한 범위 내에서 명령어 읽어옴

- page3을 실행할 때는 page1,2가 필요 없으므로 page1,2 둘 중 하나는 second storage에 저장 후 block2 비운 다음 page3 보냄(swapping)

- 이 과정에서 1kB를 second storage로 옮겨야 함 → 성능 저하

access violation

- process1이 previlleged mode에서 동작하는 경우에

process2에서 block0으로 접근하려고 했다면 access violation 발생 - previllege가 부족하다는 message 띄움 → process terminate