Cortex-M3/M4 features

-

아키텍쳐 특징

: ARMv7-M 아키텍쳐 기반

: 16bit, 32bit Thumb 명령어 혼합 사용

: MUL/DIV 명령어가 존재하여 곱셈 및 나눗셈을 수행 가능

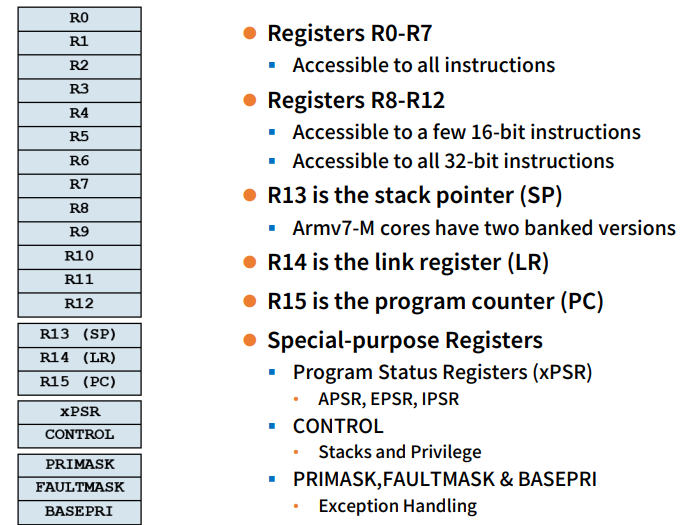

: 16개의 32bit 레지스터 존재 -

효율적인 인터럽트 처리

: 레지스터의 하드웨어 스택 사용

: 즉, 인터럽트가 발생했을 때 레지스터의 상태를 자동으로 저장하여 처리속도를 향상 시킴 -

OS 지원 특징

: User/Supervisor model

: 사용자와 시스템 수준의 권한을 구분하여 보안 강화 시킴

: 2 stacks(Main Stack/Process Stack), SysTick Timer, MPU -

C언어로 완전히 프로그래밍 가능한 설계

-

전력 관리 기능(Power management features)

: WIC/수면모드(sleep mode)/architectural clock gating -

효율적인 디버그 및 개발 지원 기능

: SWD/breakpoints/watchpoints/instruction trace

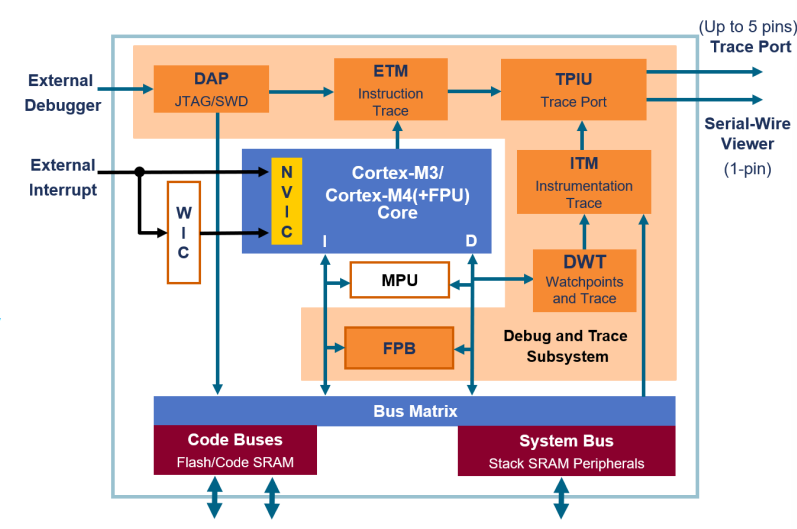

Cortex-M3/M4 processor

- 구성 블록

- Cortex-M3/M4 코어

: M4에서 선택 가능한 부동 소수점 장치(FPU) 포함 - NVIC(Interrupt Controller)

: 인터럽트 1~240까지

: 우선순위 비트 3 ~ 8까지

- 선택적 블록

- Debug and Trace Subsystem

- wakeup interrupt Controller(WIC)

- Memory Protection Unit(MPU)

- 구성 가능한 기능들

- Sleep modes

- Endianness

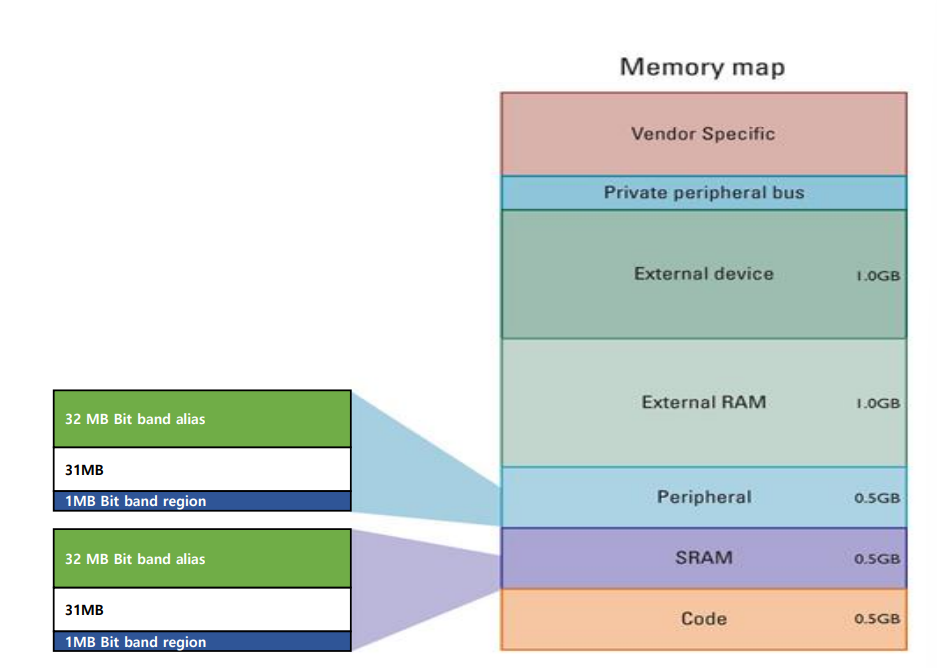

- Bit-Banding

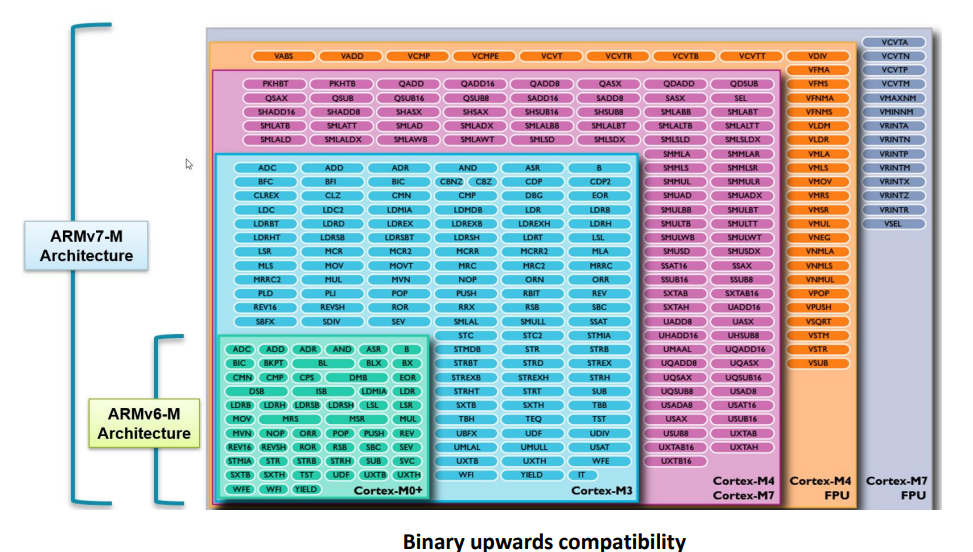

M-profile instructions

Different from other Arm processors

- ARMv7-M Architecture

- No ARM instruction set supper

: Thumb only with Thumb-2 32 bit instructions - No Cache : No MMU

- Only 2 Operating modes

- Debug is optimized for microcontroller applications

- Vector table is addresses, not instructions

- Interrupts automatically save/restore state

- Exceptions Programmed in C

- No Coprocessor 15

: All registers are memory-mapped - Interrupt controller is part of the processor

- Fixed memory map

- Bit banding capbility

- NMI(Non Maskable Interrupt)

: 특별한 종류의 인터럽트로 우선순위가 높음

: 마스킹이 불가능 하다는 것은 해당 인터럽트를 비활성화 시킬 수 없다는 것

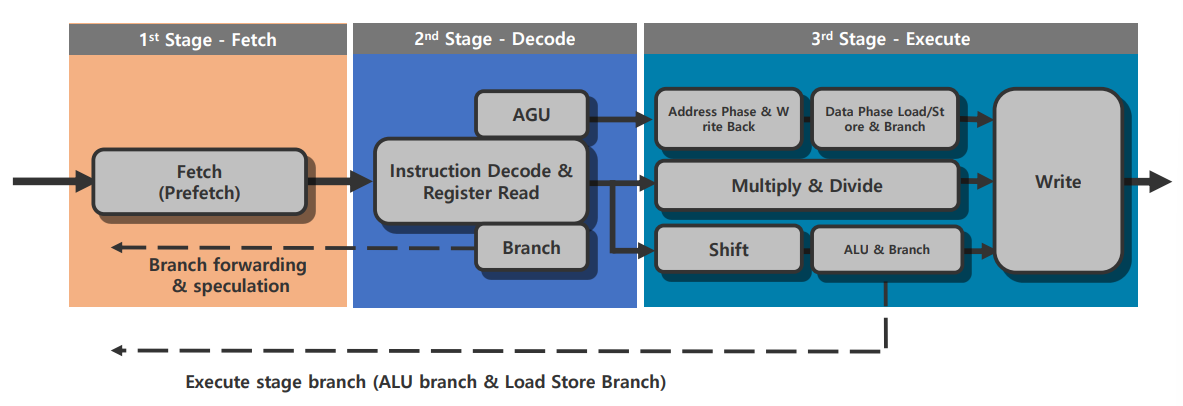

Processor Pipeline

- 3 Stage Fetch Decode Excute Pipeline

Cycle counting

컴퓨터 시스템에서 작업이 완료되는 데 걸리는 clock cycle의 수를 측정

- 대부분의 데이터 처리 명령어는 한 사이클 내에서 실행

- 그러나 메모리 액세스 명령어는 실행에 여러 사이클이 소요될 수 있음

: 이는 파이프라인 스톨(pipeline stall)을 유발할 수 있음

pipeline stall

파이프라인에서 발생하는 지연 현상

: 타이밍은 외부 메모리 시스템에 따라 달라짐

- 제어 흐름 명령어는 파이프라인을 리필할 수 있음

- 데이터 감시 및 추적 유닛(DWT)는 여섯 개의 카운터 레지스터를 제공함

- Cortex-M3 or M4 기술 참조 메뉴얼에는 다음이 포함

: 모든 명령어에 대한 사이클 카운트 정보

: load/store timing에 대한 상세 정보

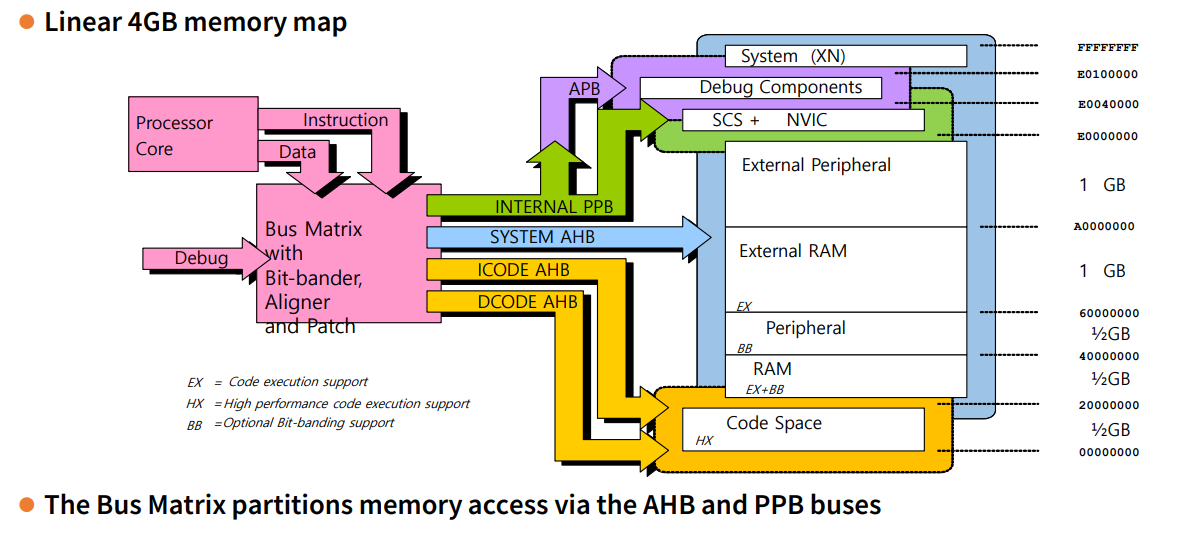

Memory Map

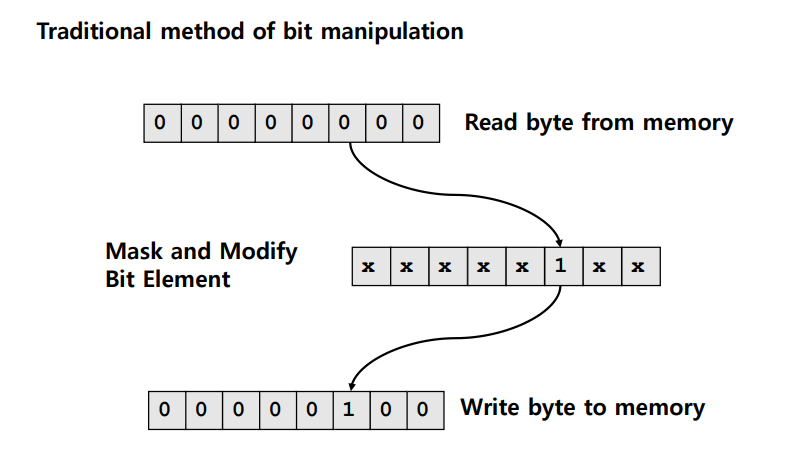

Bitwise memory access

Bit banding

- 구현 시 선택적인 기능

- 메모리의 단일 비트를 읽거나 수정하는 데 사용

일반적으로 프로그래머는 메모리 주소를 사용하여 메모리에 액세스하지만, 비트 밴딩을 사용하면 개별 비트에 대한 액세스가 간소화됩니다. 각 비트에 대해 별도의 비트 밴드(밴딩된 비트) 영역이 마련되어 있으며, 이 영역은 해당 비트를 읽고 쓸 수 있는 특별한 메모리 영역

- 메모리의 워드 주소에 대한 쓰기가 비트 밴딩 별칭 영역에 있는 단일 비트에 영향을 줌

- 버스 매트릭스에 의해 원자적인 읽기-수정-쓰기로 변환되는 쓰기가 이루어짐.

- 레지스터의 Bit[0]이 메모리의 적절한 비트로 쓰여짐.

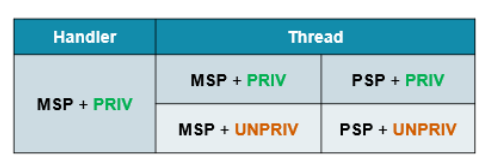

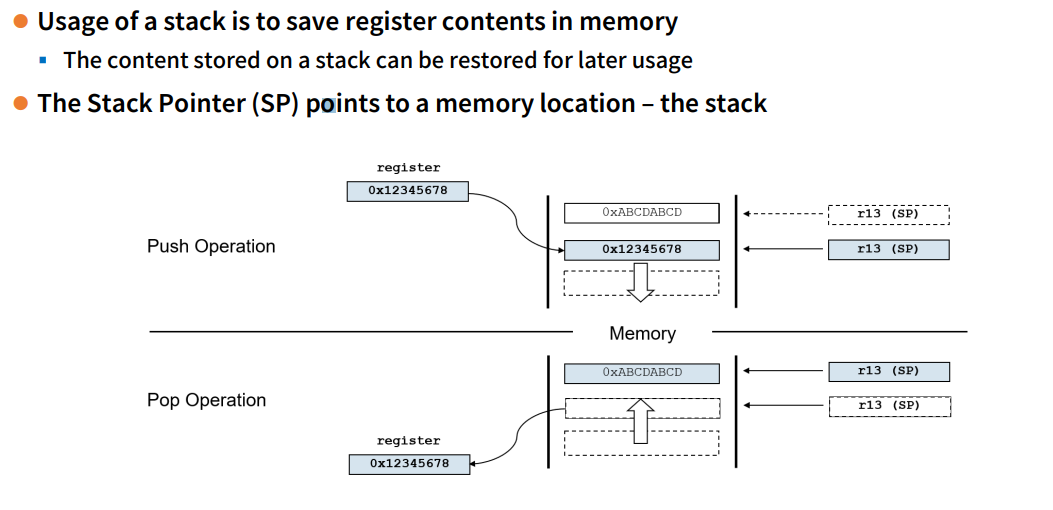

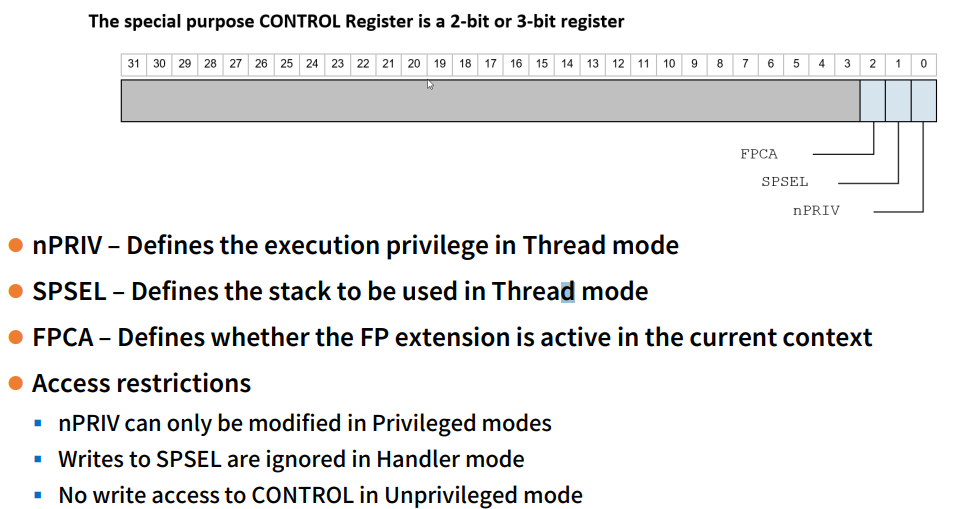

Modes, privilege and stacks

- 프로세서 코어는 특권 작업/비특권 작업 지원

: 이는 메모리 및 레지스터의 접근을 제어하는 데 사용 - two stacks

- Main Stack

: Msp(main stack pointer)를 통해 관리

: 예외 처리나 핸들러 모드에서 사용

: 항상 특권 모드에서 사용

: 시스템 전반의 작업에 필요한 데이터 저장 - Process Stack

: Psp(process stack pointer)를 통해 사용

: 스레드 모드에서 사용

: 특권/비특권 모드 모두 사용 가능

: 주로 사용자 응용 프로그램 코드에 필ㅇ한 데이터 저장

-

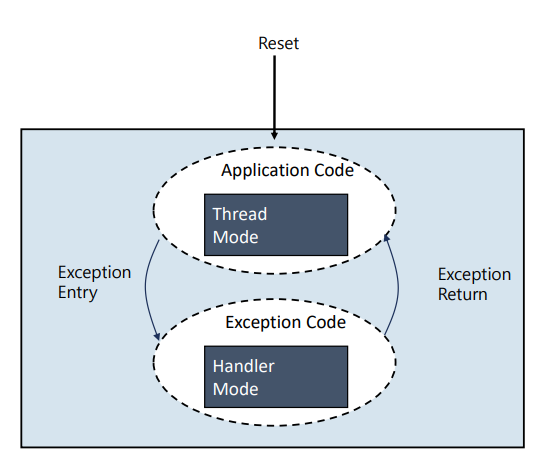

Handler mode

: 예외가 발생하면 핸들러 모드로 진입

: 항상 특권 모드

: 항상 메인 스택 사용 -

Thread mode

: 코어는 리셋 후에 스레드 모드로 진입

: 일반적으로 사용자 응용 프로그램 코드에 사용

: 특권 또는 비특권 모드에서 실행(리셋 핸들러에 의해 구성되어야 함.)

: 메인 스택 또는 프로세스 스택 사용 가능

: 스레드 모드가 비특권 모드인 경우 일반적으로 프로세스 스택을 사용

Interrupts and exceptions

-

low latency(저지연) 및 우수한 인터럽트 성능을 위한 최적화

: 프로세서 레지스터의 자동 저장 및 복원

: 멀티 사이클 명령어는 낮은 인터럽트 지연을 위해 중단 가능 -

Nested Vectored Interrupt Controller(NVIC, 중첩 벡터 인터럽트 컨트롤러)

: 1부터 240까지의 인터럽트 채널에서 선택 가능

: 인터럽트 핸들러는 상태 저장과 병렬로 검색 -

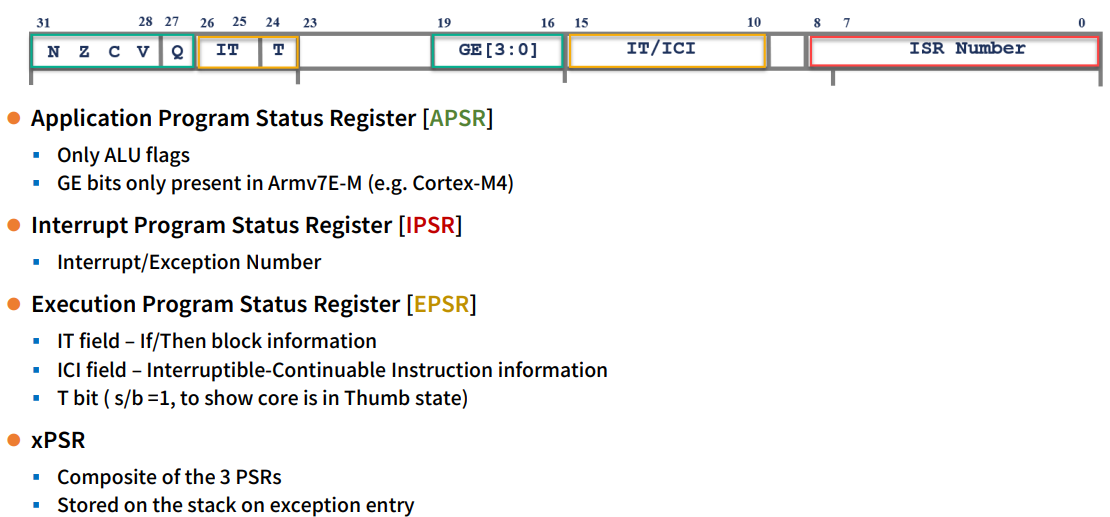

예외 발생 레지스터 스택(Register stacking on exception)

: R0~R3

: R12

: LR(Link Register)

: ReturnAddress(PC)

: xPSR(실행 상태 레지스터)

예외 발생 레지스터 스택이란?

프로세서가 예외(ex. 인터럽트, 예외 처리, 오류) 를 처리할 때 현재 실행 중인 상태를 보존하기 위해 사용되는 레지스터 세트. 이 스택은 프로세서가 예외를 처리하기 전에 현재 상태를 저장하고 예외 처리가 완료되면 다시 그 상태로 복원하는 데 사용.

Memory Protection Unit(MPU)

-

다양한 메모리 영역에 대한 접근 제어를 제공

: 시스템은 다른 메모리 영역에 대한 접근을 허용/제한 하는 기능 제공 -

ZERO LATENCY MEMORY PROTECTION

: 레지스터에 저장된 8개의 영역 지원

: 최소 영역 크기는 32BYTE이며(최대 4GB), 주소 변환 또는 페이지 테이블이 필요하지 않음 -

메모리 매핑된 제어 레지스터를 통해 구성

: 이 기능은 메모리 매핑된 제어 레지스터를 통해 구성. 이를 통해 프로그램이 메모리 영역에 대한 접근을 제어할 수 있음.

★ Power Management

- Multiple sleep modes supported

- SLEEPING

- SLEEPDEEP

: 이는 시스템 컨트롤 레지스터에 의해 제어됨.

: WIC(Wakeup Interrupt Controller, 시스템이 슬립 모드에서 깨어날 때 필요한 외부 이벤트를 감지하고 관리) 기반 SLEEPDEEP

-

sleep now

: WFI(Wait for Interrupt), WFE(Wait for Event), SEV(SendEVent) 명령어 -

Sleep on exit

: 마지막 ISR(Interrupt Service Routine)에서 리턴시 즉시 슬립

: 즉, 시스템이 인터럽트를 처리한 후 슬립 모드로 전환하여 전력을 전환함.

: 결론적으로 마지막 인터럽트 처리 후에는 대기상태로 돌아가는 것이 아닌 바로 슬립 모드로 진입 -

슬립 모드에서 시스템은 클럭 게이팅 됨.

: 시스템이 슬립 모드로 들어가면, 클럭이 해당 시스템의 핵심 구성 요소로부터 제거

: NVIC 인터럽트 인터페이스는 깨어 있음.

: 이는 시스템이 실립 상태일 때도 인터럽트를 처리하고, 필요한 경우 시스템을 깨우기 위해 인터럽트를 발생시킬 수 있음. -

Wakeup Interrupt Controller(WIC)

: 선택적 외부 웨이크업 감지기가 완전히 전원을 끌 수 있게 함.

: 상태 보유 / 전력 차단(SRPG) 방법론과 효과적으로 함께 사용 가능

Core Debug

-

Single Stepping(싱글 스탭핑)

: 프로그램을 한 단계씩 실행하며 디버깅 -

Debug Access Port(DAP)를 통한 모든 메모리 및 레지스터 액세스 제공

: 디버깅 시 모든 메모리 및 레지스터에 접근 가능한 디버그 액세스 포트(DAP)를 통한 액세스 제공 -

Flash Patch and BreakPoint Unit(FPB)

: ROM에 있는 명령을 RAM으로 리매핑하고, 브레이크 포인트 기능을 제공하는 플래시 패치 및 브레이크포인트 유닛 -

Data Watchpoint and Trace Unit(DWT)

: 특정 주소의 데이터 액세스를 감지

: 코드 프로파일링을 통한 이벤트 카운터 제공

: 디버그 이벤트 또는 추적 패킷을 생성하는 데이터 워치 포인트 및 트레이스 유닉 -

Instrumentation Trace Macrocell(ITM)

: Printf 스타일의 소프트웨어 제어 추적을 지원 -

Optional Embedded Trace Macrocell(ETM)

: 명령 추적을 제공하는 선택적 임베디드 트레이스 매크로셀

데이터 워치 포인트(data watchpoint)란?

: 프로그램이 특정 메모리 주소나 변수에 접근할 때 이를 감지하고 이벤트를 생성하는 기능

: 즉, 디버깅에 유용한 도구 중 하나

System timer - SysTick

- 유연한 시스템 타이머

: 24비트 카운터로, 자동으로 다시로드되며, 선택적으로 카운트가 0일 때 인터럽트를 발생시킬 수 있음. - 클럭 소스

: CPU 클럭 또는 선택적으로 외부 타이밍 참조를 사용 가능. - 보정

: 10ms 간격에 필요한 값을 제공하여 정확한 타이밍을 유지

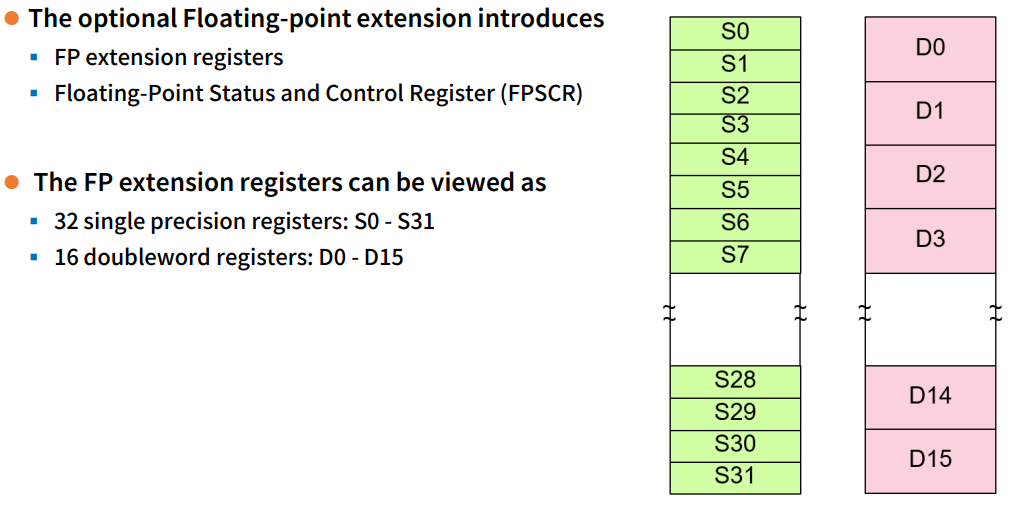

Cortex-M4 Floating Point Unit

-

Cortex-M4는 밀접하게 통합된 하드웨어 부동 소수점 유닛을 포함

: FPv4-SP 아키텍처를 구현

: 별도의 레지스터 파일로 이루어진 16개의 더블 프리시전 레지스터 (32개의 싱글 프리시전 레지스터)

: IEEE-754 호환 -

하드웨어는 싱글 프리시전 산술을 구현

: 더블 프리시전은 소프트웨어를 통해 처리됨 -

하드웨어에서 지원하는 기능

: 곱셈, 덧셈, 뺄셈, 곱셈-누적

: 비교 및 형식 변환

: 나눗셈 및 제곱근 -

다른 작업(예: 벡터화)은 지원 코드가 필요함

-

FPU는 리셋 시 비활성화

: 초기화 코드에 의해 활성화 및 구성되어야 함

: C 라이브러리 초기화 이전에 수행되어야 함

: Cortex-M4 TRM의 7장에 샘플 코드가 제공됨

Core Registers

Armv7-M profile register set

Floating point extension registers

Program Counter(PC)

- FETCH / DECODE / EXCUTION 중 항상 PIPELINE의

FETCH단계를 가리킴 ★★★ - PC는 항상 현재 주소의 +4를 가리킴. ★★★

CF. 32bit일 경우엔 +8

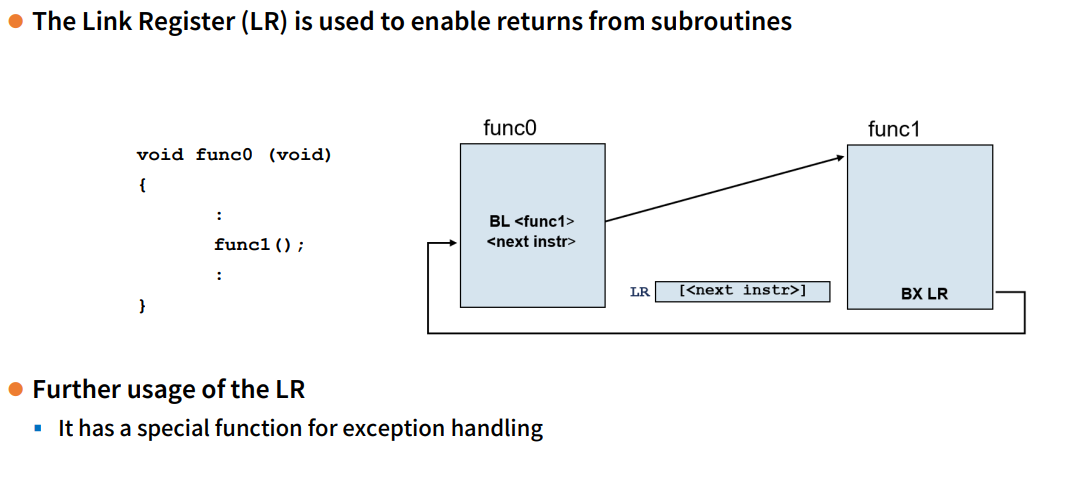

Link Register

Stack Pointer(SP)

Program Status Registers

CONTROL Register

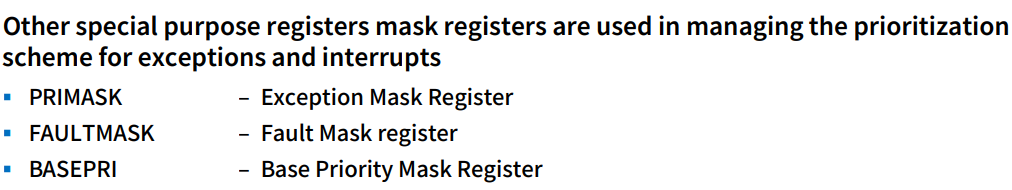

Other Special Purpose Registers