Verilog를 다루기전에 더 큰 범주인 HDL(Hardware Description Language)에 대해서 얘기를 나눠봅시다. Verilog는 HDL이라는 Hardware Description Langauage의 일종입니다.

그렇다면 HDL은 무엇일까요? 해석 그대로 하드웨어를 묘사하는 언어입니다.

외 SW언어가 아니라 HDL이라는 새로운 범주를 사용하는지 C(C++)언어와 비교해서 살펴봅시다.

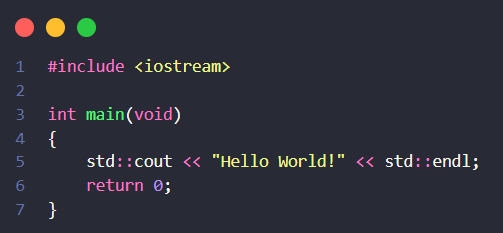

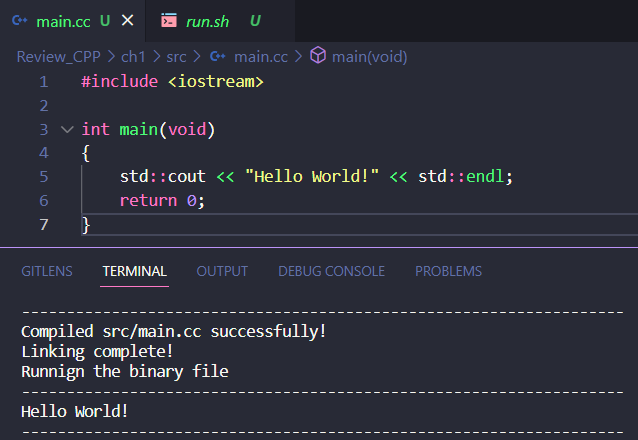

해당 코드는 저희가 코드를 배우면 항상 먼저하는 Hello World!를 출력하는 cpp코드입니다. 문법이 무슨 내용인지는 몰라도 젼혀 상관없습니다. 해당 cpp파일을 run하기 위해서 build또는 compile을 하셨을 겁니다.

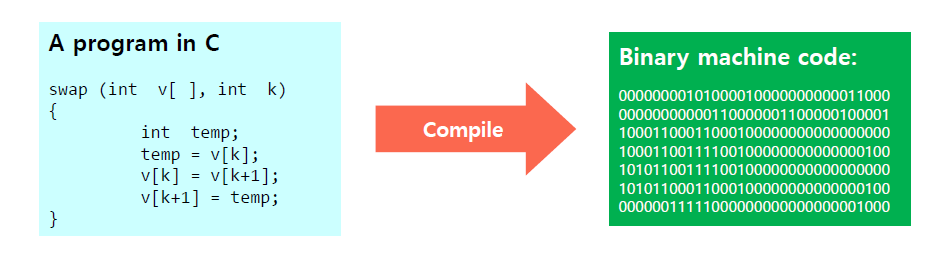

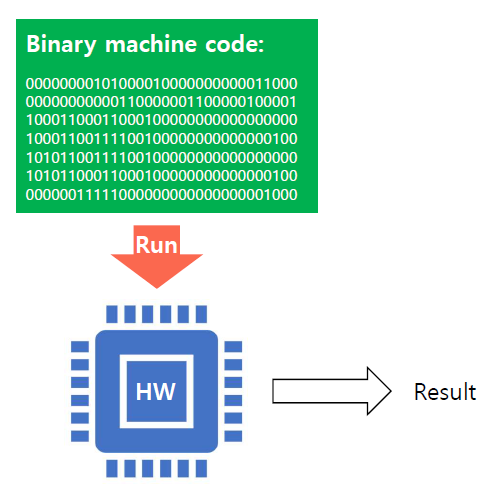

그렇게되면 highlevel language로 작성된 c파일이 assembly language를 거쳐서, 컴퓨터가 동작할 수 있는 0과 1로만 이뤄진 binary machine language로 변환됩니다.

그렇게 생성된 exe파일이 computer에서 실행되면 비로서 Hello World!가 terminal에 출력되게 되는 것이죠.

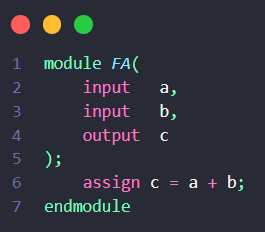

하지만 HDL은 이런식으로 동작하지 않습니다. 위의 그림은 Full adder를 Verilog코드로 작성한 경우입니다.

HDL의 D가 Description(묘사)를 의미하는 것처럼 Verilog로 코드를 작성하고 compile을 수행한 이후에 나타나는 binary 코드는 HW로 변환이됩니다.

그렇기에 Verilog로 작성한 코드가 정상적인 동작하는지 판단하기 위해서는 'testbench simulation'이라는 과정이 필요하게 되는데 이는 차후에 천천히 다뤄보겠습니다.

오늘은 HDL이 무엇인지 다루었습니다. 다음 글에서는 왜 이렇게 HDL과 SW를 구분지어 얘기해야 되는지 말씀드리도록 하겠습니다.

REF.

- Digital Systems Design using Verilog (By C.H. Roth, Jr, L.K. John, and B.K. Lee)

- Contemporary Logic Design (By R. H. Katz, G. Borriello)

- Verilog ICON

https://icon-icons.com/ko/%EC%95%84%EC%9D%B4%EC%BD%98/%ED%8C%8C%EC%9D%BC%EC%9D%98-%EC%9C%A0%ED%98%95-verilog/130092