지난 시간에 HDL(Hardware Description Language)가 무엇인지 알아봤습니다. 그렇다면 왜 HDL이 등장배경에 대해서 알아보도록 하겠습니다.

전자분야의 급격한 발전을 통해서 아주 작은 단위의 '스위치'인 Transistor가 개발되었고 이를 통해서 매우 복잡한 회로를 구성할 수 있게 되었습니다. 그에 따라서 자연히 컴퓨터 공학 분야도 빠른 성장을 이루게 됩니다.

저희가 지금 배우고자 하는 것은 Verilog임으로 Transistor의 원리며, 구조와 같은 내용은 배제하도록 하겠습니다. 중요한건 0과 1을 구분짓는 회로를 매우적은 자원(area)와 전력(vol)으로 구성할 수 있게 되었다는 점입니다.

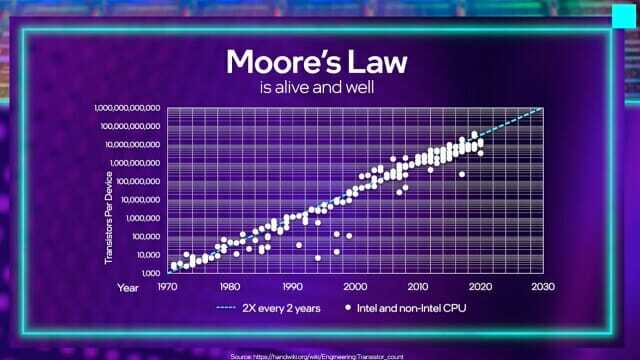

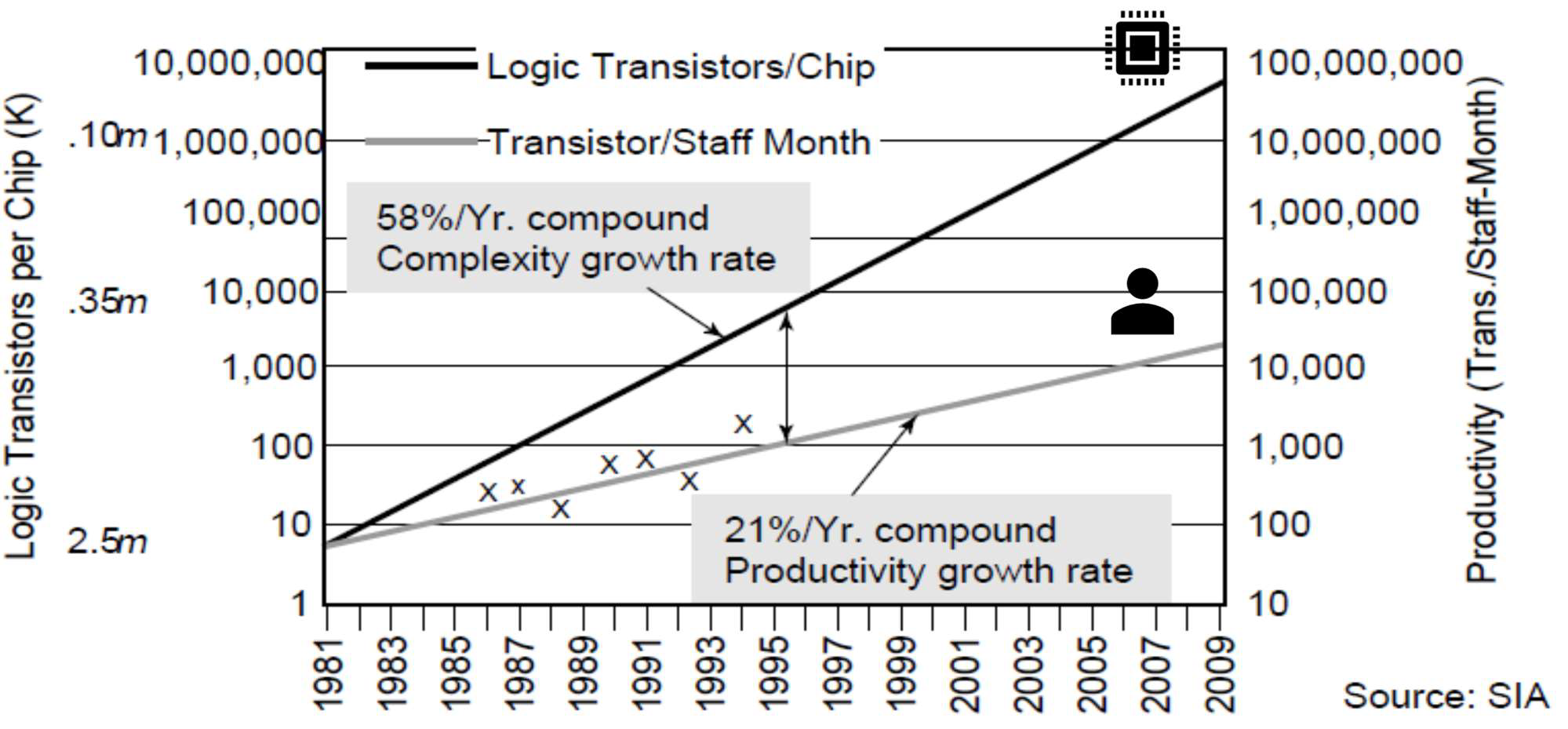

컴퓨터 공학 분야를 공부하면서 Moore's Law(무어의 법칙)이라는 용어를 자주 듣게 될 것입니다.

Intel의 창시자 Golden Moore라는 CEO가 '반도체 시장을 보았을 때 2년마다 집적도가 2배 정도 높아진다'라는 경향성을 말한 것인데 많은 반도체 소자, 공정, 설계 회사들이 '대략 2년뒤에는 집적도가 어느정도 되겠구나'라고 기준을 잡고 제품의 설계 및 생산을 기획하였다고 보시면 될 것 같습니다.

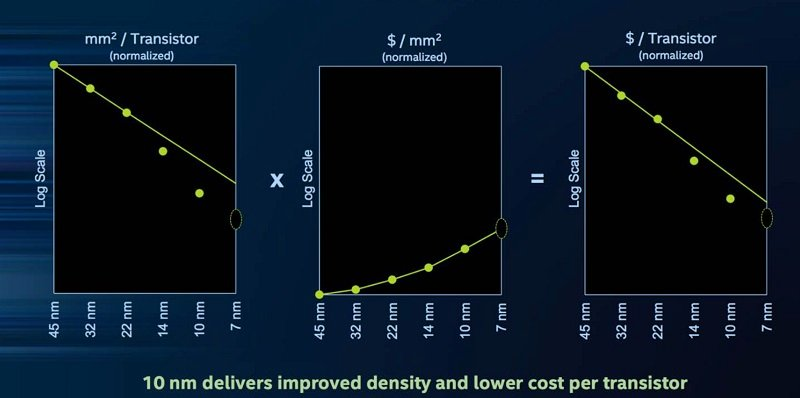

(좀 더 익숙한 얘기를 들자면 10nm공정, 7nm공정 이런 얘기를 들어보셨을 것입니다. 10nm와 7nm 비율이 0.7배 인것을 알 수 있는데 이를 넓이로 계산하면 0.49배, 대략 절반이 됩니다. 공정기술이 대략 2년마다 0.7배가 된다는 것을 위와 같이 간략히 표현한 것이라 생각할 수 있습니다)

결국 하고싶은 얘기는 그래프에서 나오는 것처럼 반도체 chip을 구성하는 transistor의 숫자가 말도 안되게 빠른 속도로 늘고 있다는 것을 의미하고, 저희 교수님이 자주 하시는 말로는 "Tr1개에 엔지니어 1명이 붙는 과거를 현재와 비교하면 현재는 210억명의 엔지니어가 필요하게 되는 상황"이라는 것입니다.

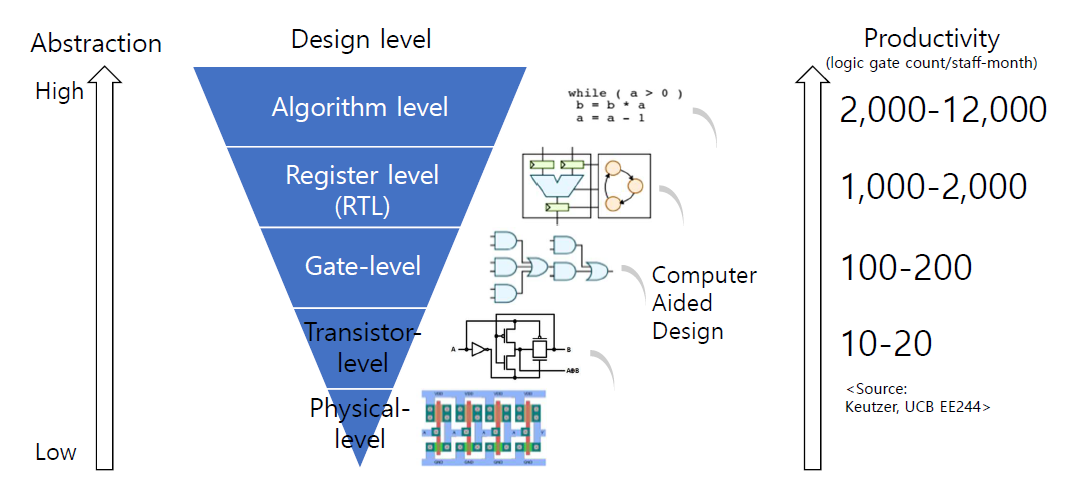

그렇기에 하드웨어 설계 엔지니어들은 추상화 및 여러 방법들을 통해서 설계 방법론을 발전시키고 업무를 분업화시키며, 이를 통해서 생산성을 높여 시장의 욕구를 충족시키고 있습니다.

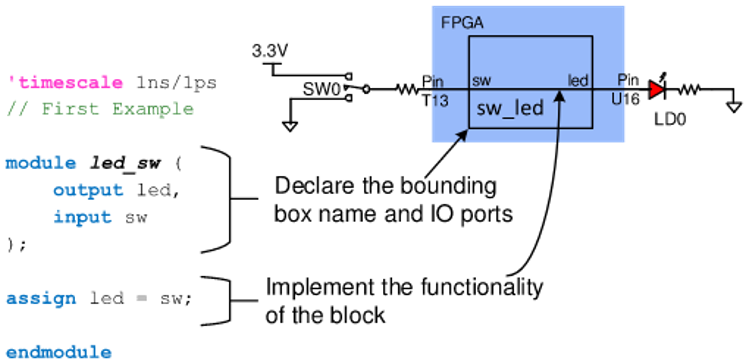

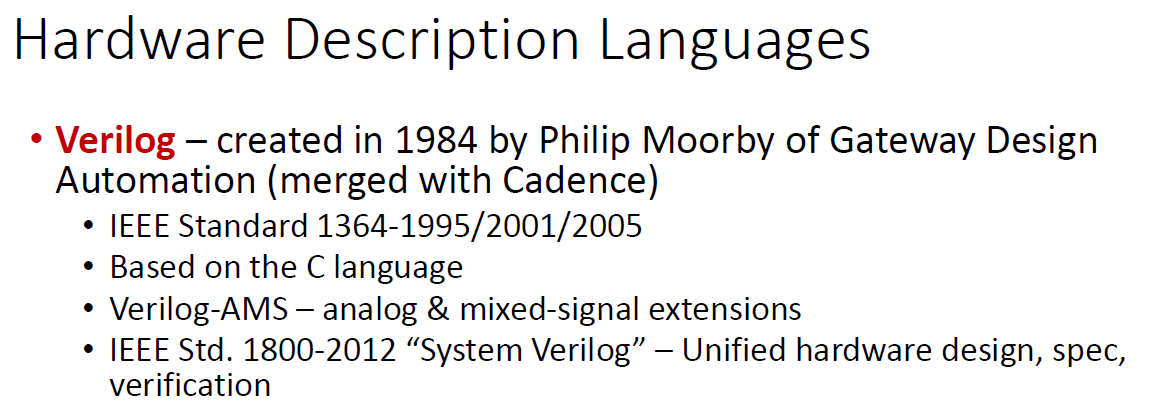

그런 과정에서 Transisotr들의 연결과 구성을 나타내는데 Verilog라는 언어가 출현하게 되었습니다. VHDL이 먼저 나왔고, Verilog의 최초는 검증(Verification)만을 위해서 나타났고 뭐 그 이전에는 CAD를 이용해서 설계를 진행했다는 것은 관심있는 분들이라면 직접 찾아보시면 될 것입니다. 여하튼 Verilog HDL은 이렇게 수작업이던 설계의 편의를 더하기 위해 나타났고, 현재 많은 회로설계 회사들에서 사용되고 있습니다.

(물론 Verilog의 Highend인 SystemVerilog가 실제로 주를 이루고, VHDL을 사용하고 있는 회사가 아직 존재하는 것으로 알고있습니다)

위의 설명의 2번째 줄을 보면 "Based on the C language"라는 문구가 보일 것입니다. Verilog는 C를 기반으로 하고있기 때문에 많은 문법이 C언어와 유사한 것을 앞으로 익히시면서 느낄 수 있을 겁니다.

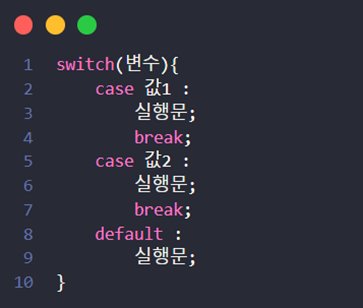

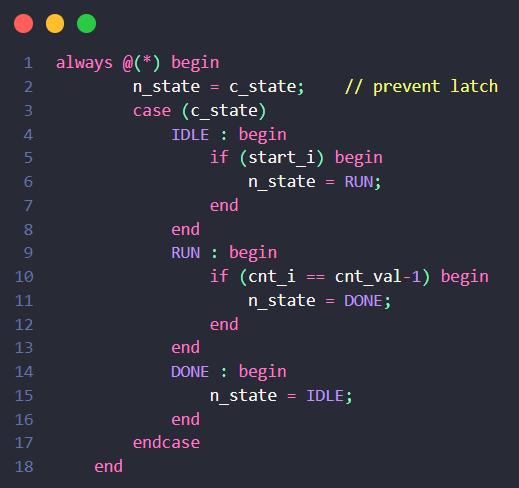

C언어 Switch문

Verilog Case문

그렇지만 이것이 마냥 좋은 얘기는 아니라는 것을 명심해 주세요. 문법을 익히시는데 어려움을 덜 느낄 수 있지만 C와 유사한 문법에서 오는 친숙함 때문에 방향을 잃으실 수 있습니다.

HDL이 왜 나오게 되었는지 배경을 알아보았고 Verilog를 공부할 때 C를 기반으로 두었지만 HDL과 SW language는 다르기 때문에 주의해야된다는 것을 알아보았습니다.

다음은 이제 공부에 앞서 환경 세팅에 대해서 말씀드리겠습니다.

Ref.

-

A Brief History of Electrical Technology

https://www.scaruffi.com/science/elec5.html -

트랜지스터, 전자혁명의 시초가 되다! – 발명 계기와 구조

https://news.lgdisplay.com/kr/2015/05/transistor/ -

Verilog 코드 및 구현 그림 (Digilent)

https://learn.digilentinc.com/Documents/Digital/B01_VerilogFirstExample/FirstExample.svg -

Verilog modeling for synthesis of ASIC designs for native speakers of VHDL (ELEC 4200, By Victor P. Nelson)