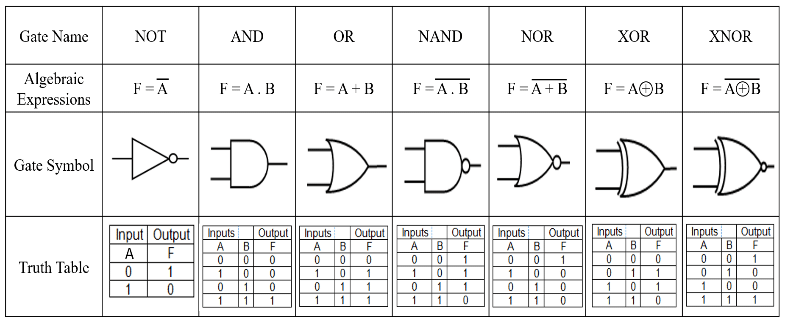

제일 처음 다뤄볼 것들은 아래의 basic gate입니다. 해당 gate들로 합성이 되도록 Verilog코드를 작성해보면서 Verilog코드의 기초형식과 몇 가지 operator, 그리고 Variable type을 다뤄볼 예정입니다. boolean식이 기억이 안난다면 해당 사진을 참고해주세요.

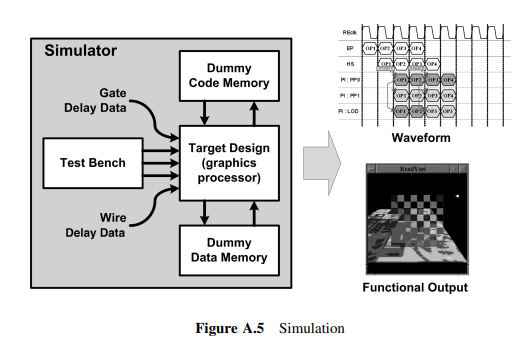

여기서 여러분이 약속해주셔야 되는 부분이 있습니다. 해당 코드들이 제대로 작성되었는지 확인하기 위해서 수행하는 testbench simulation이라는 과정이 있는데 해당 내용은 조금 뒤에 다룰 예정입니다. 따라서 testbench를 다루기 이전에는 블로그에 적혀있는 변수명, 숫자 등을 동일하게 작성해주셔야 됩니다.

(참고로 코드가 길어지는게 아니라면 코드들은 사진으로만 업로드할 예정입니다)

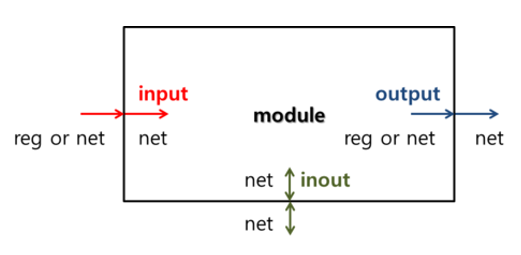

시작해봅시다. 먼저 Verilog에서 하나의 logic을 module이라고 지칭합니다. 그리고 module들을 연결하여 더 큰 module을 만들게 됩니다. 즉 무언가 작성할 때 module이 하나의 설계 단위라고 생각하시면 됩니다.

그리고 Verilog 코드의 module은 다음과 같은 형식을 가집니다.

module name_of_module (

// port list

// port list

);

// declaration of module

// declaration of module

endmodulemodule과 endmodule로 하나의 module을 구별하고, 괄호 사이에 input, output port들을 정의하며 괄호밖에는 해당 모듈의 구조를 기술합니다. 아직 뭐가 뭔지 익숙하지 않으실 겁니다.

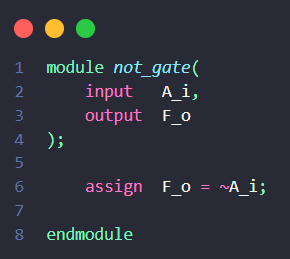

그럼 일단 not gate로 시작해봅시다. vscode에서 아래 코드를 작성해주세요. 여기서 파일명은 not_gate.v로 해주시면 됩니다. 앞으로 verilog코드를 작성해주실 때는 확장자로 .v를 사용해주세요.

코드를 좀 살펴보면 module의 명칭은 'not_gate'입니다. A_i라는 input port가 존재하고, F_o라는 output port가 존재합니다. 또한 module의 동작을 기술하는 부분에는 A_i의 not(~)을 F_o에 assign(할당)하라 라는 구문이 적혀있습니다. 즉 input이 A_i이고 output이 F_o인 하나의 not_gate를 설계한 것입니다.

input과 output의 변수명 뒤에 underbar + i, o는 해당 변수가 input인지 output인지 구분해주기 위한 것입니다. 나중에 module이 커지게되면 port의 숫자도 많아지고 그에따라 설계자의 실수를 줄이기 위해서 관습적으로 많이 달아주는 것이니 습관화 해주시는 것을 추천드립니다.

(참고로 해당 첨자는 선언되어있는 module의 기준입니다. 여기선 not_gate기준에서 input과 output을 따지는거겠죠)

그러면 확인을 해봐야겠죠? tb_not_gate.v라는 파일을 생성해주시고, 해당 폴더에 위의 코드를 복붙해주세요. 그렇게 되면 not_gate.v 파일과 tb_not_gate.v 파일이 준비되게 됩니다. 그런다음 modelsim을 열어주시면 됩니다.

`timescale 1ns/1ns

module TB_not_gate(

// Testbench don't have any I/O port

);

reg A_i;

wire F_o;

// DUT inst

not_gate u_not_gate(

.A_i ( A_i ),

.F_o ( F_o )

);

initial begin

#0 A_i = 1'b0;

#5 A_i = 1'b1;

#5 A_i = 1'b0;

#5 A_i = 1'b0;

end

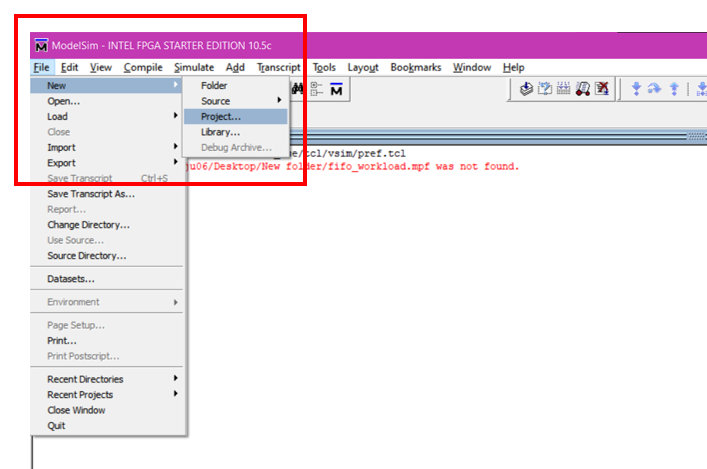

endmodulemodelsim을 다뤄봅시다. modelsim은 project라는 폴더 단위로 module들을 관리합니다. 지금은 not_gate 1개이지만 나중에 여러 module들의 verilog파일(.v파일)들이 inst라는 방법으로 연결되기 위해서는 하나의 project에 존재하면 됩니다. 일단 project를 만들어봅시다. 아래처럼 왼쪽 상단의 File - New - Project를 눌러주세요.

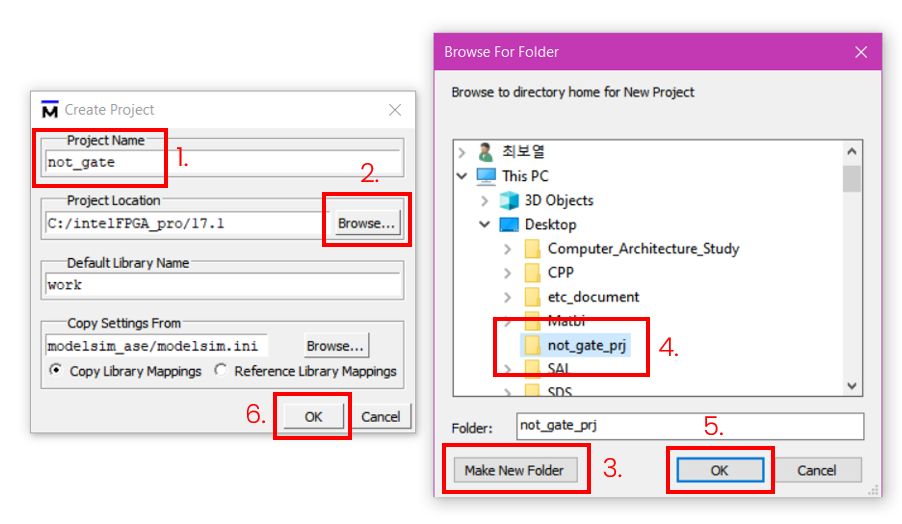

그럼 다음에 왼쪽과 같은 창이 켜질텐데 project명칭을 바꿔주시고, project location에 browse를 눌러서 project파일의 경로를 바탕화면에 해줍시다.

(뭐 이건 상관없는데 나중에 폴더들 정리할 때 편하실겁니다)

이후에 project를 정리할 폴더를 하나 만들어서 6번까지 진행해주시면 됩니다. 이렇게 폴더를 하나 만들어서 관리하는 이유가 compile, simulation을하면 .o파일이며, waveform파일이며 이것저것 파일들이 생성되는데 이런식으로 하시면 정리하시기 편하실겁니다.

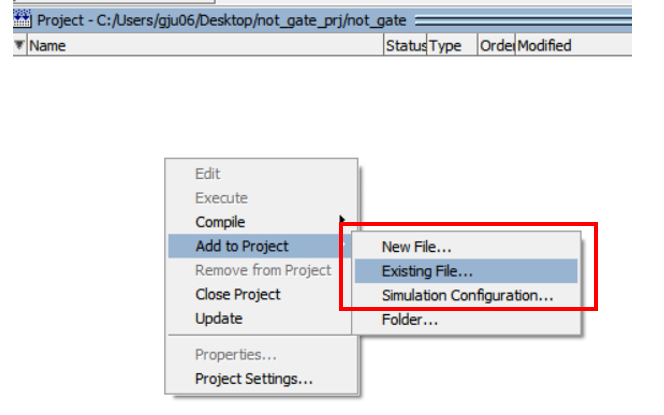

그러면 해당 창이 뜰텐데 저희가 확인하기 위해서 아래의 파일 2개를 추가해주어야 합니다.

- not_gate.v

- tb_not_gate.v

2개의 파일을 추가해주기 위해서 add existing file을 눌러줍시다.

창을 실수로 나가셨어도 상관없습니다. 아래처럼 흰색창에 마우스 오른쪽 클릭이후 나오는 옵션에서 Add to Project - Existing File...을 눌러주시면 동일하게 파일을 추가할 수 있습니다.

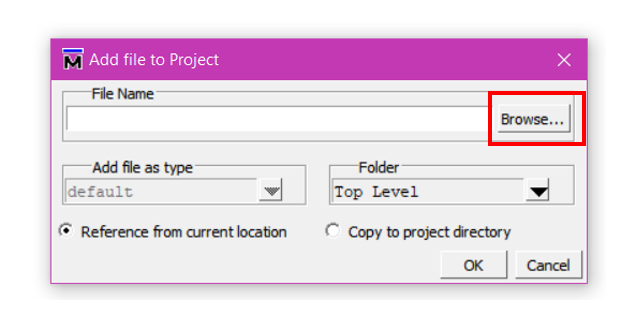

여하튼 해당 과정까지 하시면 아래와 같이 Add file to Project라는 창이 나오게 되고, Browse...을 눌러서 파일들을 찾아서 추가해주시면 됩니다.

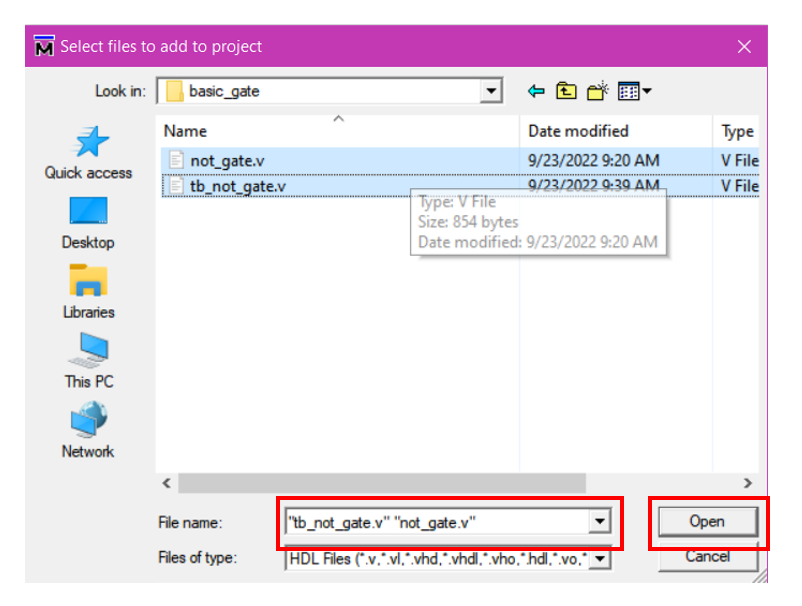

아까 vscode로 작성하신 2개의 파일이 있는 경로로 가시면 파일이 존재할텐데 여기서 한번에 둘다(or 여러개)를 추가하기 위해서 ctrl을 누르고 유지한 상태에서 파일들을 누르게 되면 저렇게 다중선택을 할 수 있습니다. 모드 선택하셨다면 Open으로 추가해줍시다.

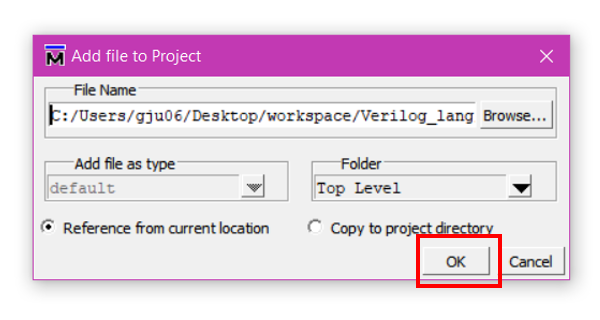

다음 나오는 창에서 OK까지 눌러주면 파일 추가가 끝나게 됩니다.

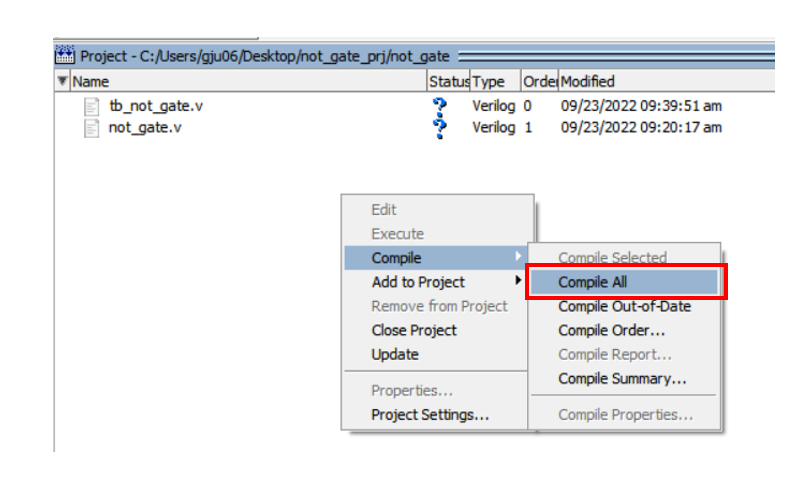

이렇게 되면 아래와 같이 project에 2개의 파일이 추가된 상태입니다. 여기서 status를 보시면 '?'표시가 되어있는데 이는 파일변경 이후에 아직 compile이 안되어있는 상태입니다. 따라서 compile을 해주려면 공백에 마우스 오른쪽 클릭을 해주시고 Compile - Compile All을 해주세요.

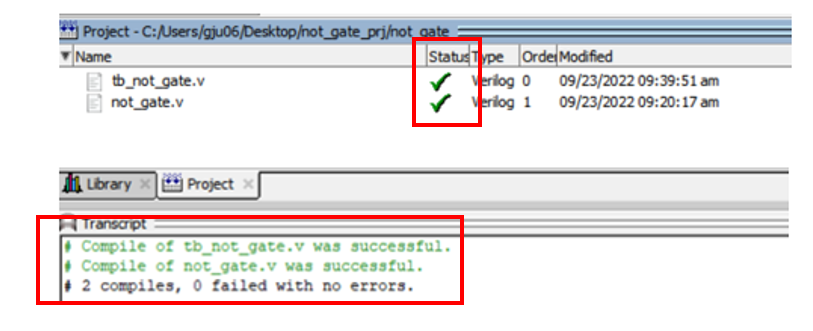

그럼 다음과 같이 체크 표시로 바뀌게 되고 아래 transcript라는 터미널 창에는 Compile을 완료했다는 표시가 나옵니다. 혹시나 Status에 'X'표시 그리고 아래 transcript에 붉은색 경고문구가 나온다면 문법적으로 오류가 존재하는 것임으로 해당 오류문구를 더블클릭하여 문제점을 확인하고 수정해주시면 됩니다.

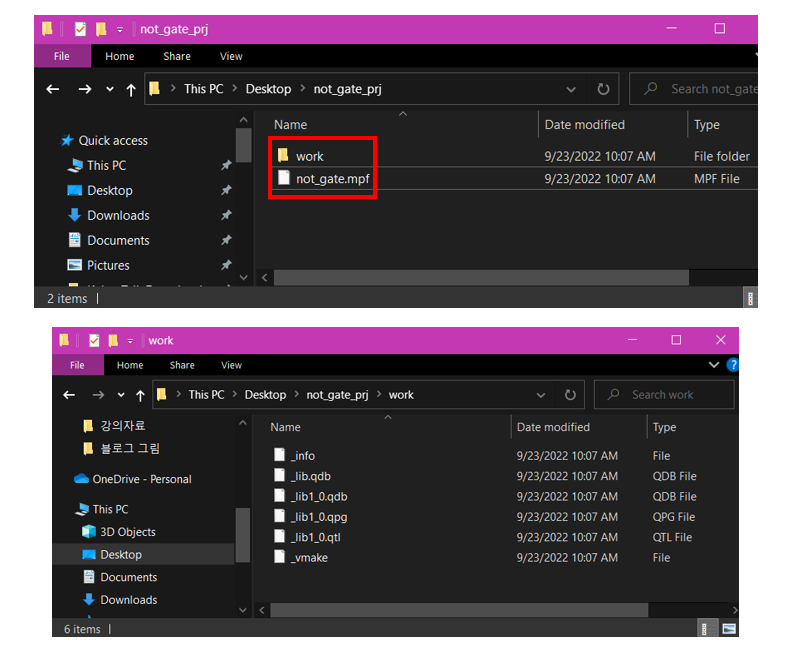

여기까지 진행하시면 Verilog파일을 Compile, 즉 binary까지 변환이 완료된 상태입니다. Project폴더를 살펴보시면 Work와 .mpf확장자가 보일텐데 이 mpf파일이 project를 지칭하는 파일입니다. 나중에 project를 다시 열고싶으면 해당 파일을 modelsim에서 열어주시면 됩니다. 뭐 다른 이런저런 파일이 생겼는데 이건 신경안쓰셔도 됩니다.

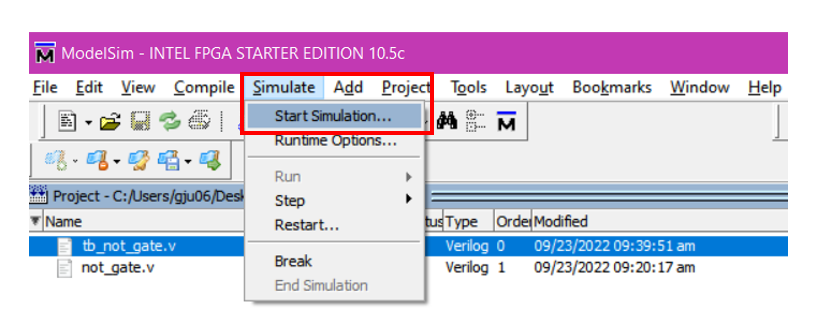

시뮬레이션을 시작해봅시다. 아래와같이 상단바에서 Simulate - Start Simulation을 눌러주세요.

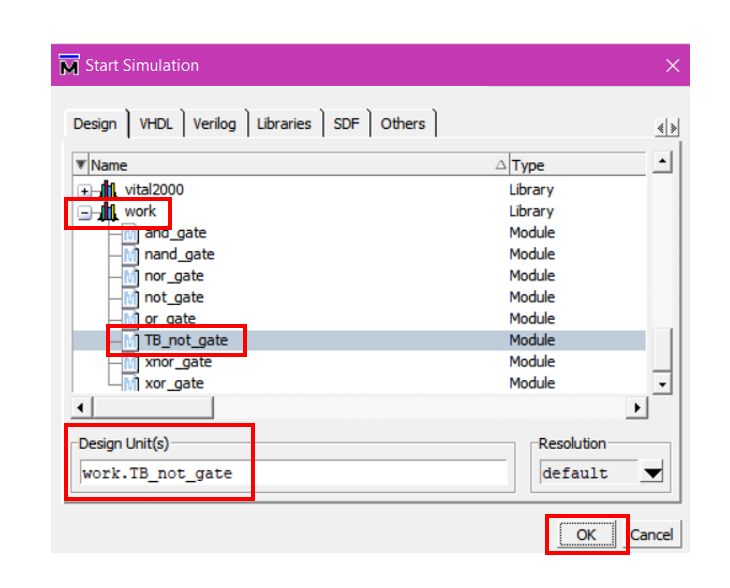

그럼 아래와 같은 창이 나오는데 오른쪽 바를 이용해서 스크롤을 아래로 하시면 work라는 것이 있고 왼쪽에 '+'가 있습니다. 눌러주시면 목록들이 나오는데 여기서 TB_not_gate를 누르고 ok를 해주세요.

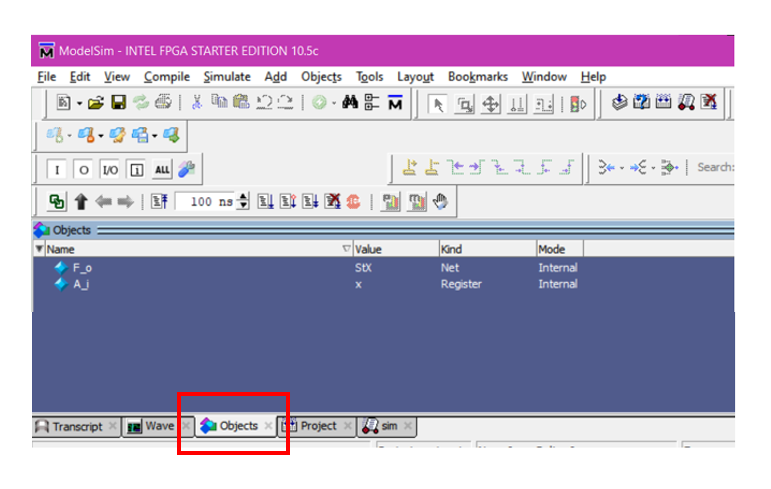

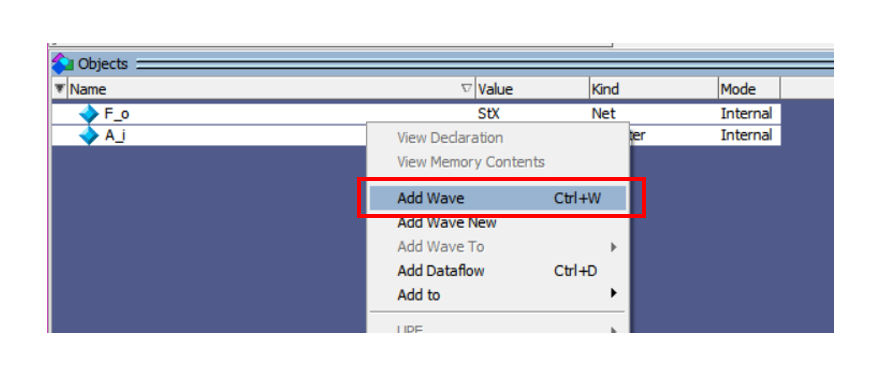

그러면 창이 잠시후에 이리저리 바뀌면서 열리게 되는데 그림의 하단에 Object를 눌러주시면 해당 파란 창이 나타나게 됩니다.

여기는 이제 waveform을 관찰할 Object들을 추가하는 곳인데 마우스 오른쪽 클릭 혹은 ctrl+w 단축키를 이용해서 waveform에 추가해주시면 됩니다. 여기서도 ctrl을 유지한채로 F_o, A_i를 누르면 다중선택할 수 있습니다.

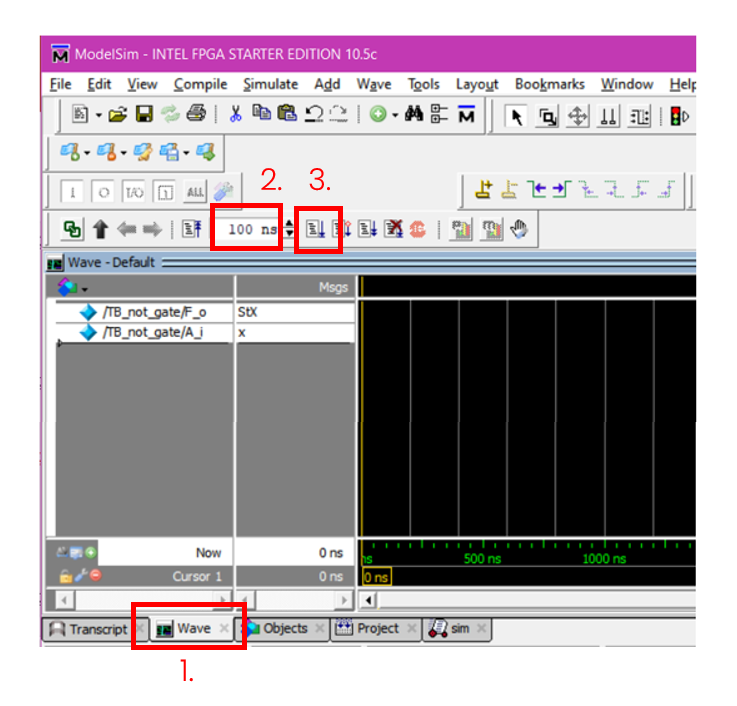

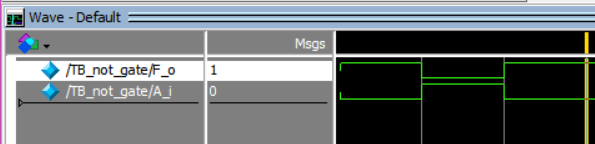

이후에 아래의 wave라는 바를 눌러서 wave창으로 전환해주시고, simulation시간을 100ns(이건 뭐 충분히만 주시면 됩니다) 그리고 오른쪽의 run을 눌러주면 simulation이 됩니다.

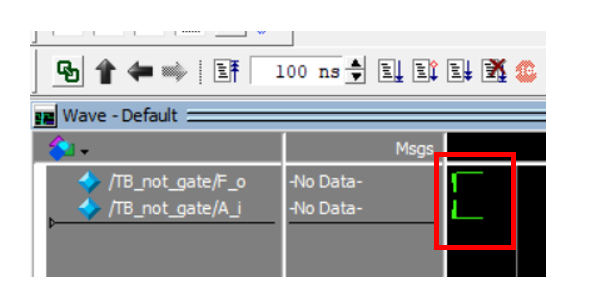

그러면 매우 작게 무언가 나타난게 보일텐데 마우스 스크롤을 이용해서 확대, 축소할 수 있습니다. 그리고 위의 메뉴바들을 잘살펴보면 돋보기 표시가 있는데 전체 waveform을 확대 축소할 수 있으니 참고해주시기 바랍니다.

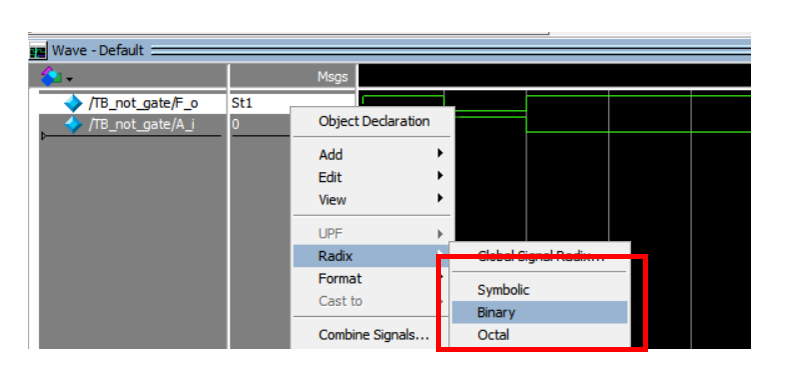

Msgs에 St1이라 되어있는데 관찰하는 값을 바꿔주기 위해서 현재 1bit를 사용하고 있음으로 마우스 오른쪽 클릭 - Radix - Binary로 바꿔주면 이진수로 표기됩니다.

대망의 waveform을 살펴봅시다. 아래의 A_i에 0을 주었을 때 F_o는 1이 되었습니다. A_i에 1을 주었을 때 F_o는 0이 되었습니다. 다시 A_i에 0을 주었을 때 F_o는 다시 1이 되었습니다. 즉 not연산을 제대로 하고 있는 것을 관찰할 수 있습니다.

정리해봅시다.

- Vscode에서 module을 Verilog code로 작성합니다.

- Vscode에서 Testbench를 작성합니다(차후 다룰 예정).

- Modelsim을 열어서 Project를 생성합니다.

- Project에 우리가 simulation할 파일을 추가합니다.(module file, testbench file)

- Simulation을 시작합니다.

- Waveform에 관찰할 Objects(input output port등)을 추가해줍니다.

- Waveform을 관찰합니다.

여기까지가 Simulation까지의 전과정입니다. 많이 길어보이지만 실제로 익숙해지시면 별거 없는 내용이고, 현재 modelsim기준으로 설명을 드렸지만 대부분의 Digital Circuit Design용 IDE는 사용 방식이 대부분 동일합니다.

(Ex. Xilinx Vivado, Synopsys Verdi 등)

수고하셨고 다음 글에서는 다른 and, or, nand, nor, xor, xnor gate등을 다루면서 해당 과정과 코드 구성, operator등을 적응해보는 시간을 가지겠습니다.