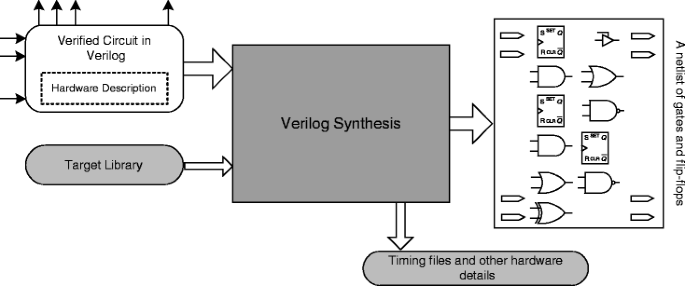

Verilog는 HDL로 앞서 말한대로 하드웨어를 기술하는 언어입니다. 따라서 해당 Verilog코드가 제대로 작성하였는지의 기준점이 SW와 다르게 'run이후에 제대로 동작하는가'에 있지않고, '합성(Synthesis)이 가능한가'에 있습니다. 따라서 설계 엔지니어는 해당 코드가 어떻게 합성이 되는지를 염두해두고 작성하는 것이 중요합니다.

따라서 해당 블로그에서는 논리회로에서 다루는 순서대로 and, or, nor, nand, xor과 같은 아주 기초적인 회로들로부터 좀 더 복잡한 회로들까지 논리회로 수업의 순서에 맞춰서 어떻게 합성되는지 까지를 자세히 다룰 예정입니다.

논리회로에서 수업을 어떤 과정으로 진행하였는지 한번 되새겨봅시다.

- 이진(boolean)의 개념을 논의하고 기초적인 and, or, nor, nand연산과 xor연산을 배웠습니다.

- 이후에 해당 기본 gate들을 기반으로 mux, demux, adder, encoder, decoder와 회로설계에서 자주 사용되는 combination logic들을 다루었습니다.

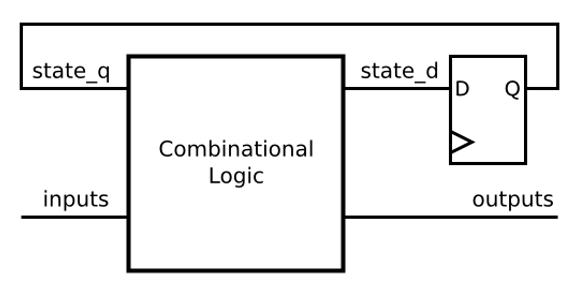

- 그리고 우리는 '시간'의 개념을 더하여서 저장의 역활을 하는 latch, flipflop등을 다루었고 이를 기반으로 기초적인 sequential logic인 counter, shifter를 다루었습니다.

- 마지막으로 fsm에 대하여 다루고 이를 바탕으로 프로젝트를 진행하셨을 것입니다.

만약 여기 적혀있는 회로들이 어떤 기능을 하는지, 개념이 무엇인지 기억이 안나셔도 괜찮습니다. 해당 내용도 같이 다룰 예정입니다.

여러분이 해당 시리즈를 보시면서

1) Verilog문법

2) 해당 코드가 어떤식으로 합성이 되는지

위의 2가지를 중점적으로 보시면서 진행해주시면 좋을 것 같습니다. 서론이 많이 길었습니다. 그럼 시작하겠습니다.