지난 시간에는 operator를 다뤄보는 시간을 가졌습니다.

이번시간에는 element들의 연결을 위한 Verilog문법인 wire에 대해서 알아보겠습니다.

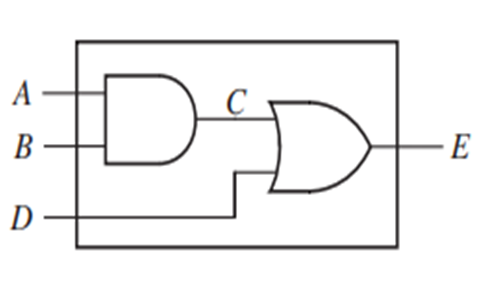

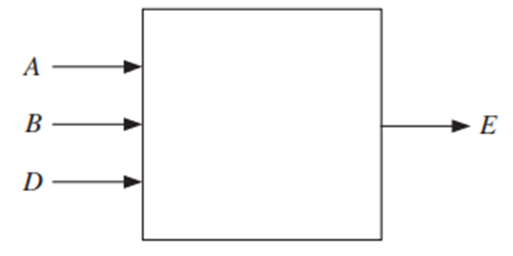

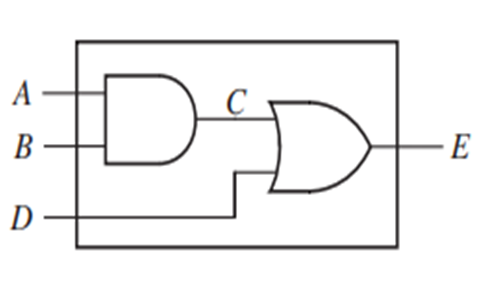

해당 그림을 보고 어떻게 Verilog로 기술해야될지 잠시 고민해봅시다. 이건 엄청 간단한 코드이지만 module이 점점 커질 수록 해당 구조를 한번에 파악하기에는 어렵게됩니다. 따라서 가장먼저 할 일은 Input과 Output port를 살펴보는 것입니다. 따라서 아래 그림과 같이 내부를 가리고 외부에 돌출되어있는 port만 살펴봅시다.

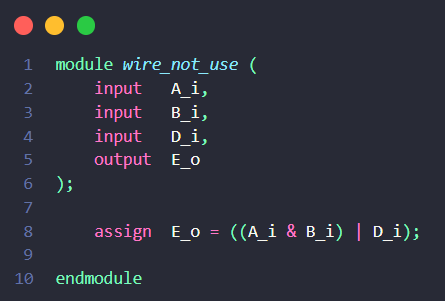

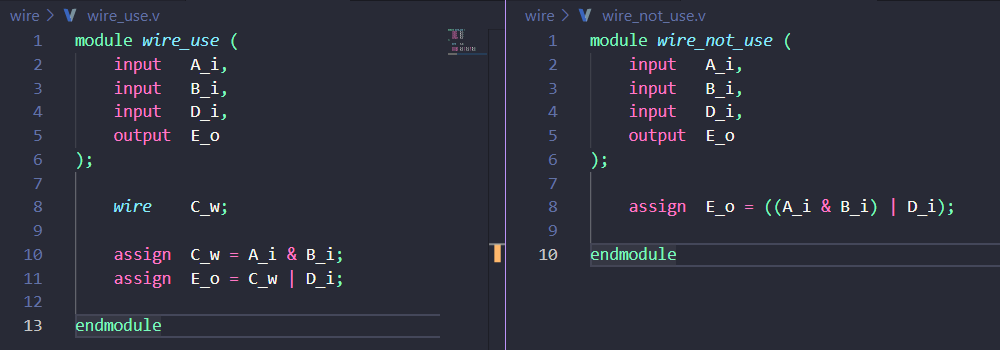

Input으로 A, B, D가 있고 Ouput으로 E가 있습니다. 그럼 다시 위의 그림으로 가서 내부를 살펴봅시다. A와 B를 AND연산을 수행하고 해당 결과를 D와 OR연산을 해서 E라는 Output과 연결되게 됩니다. 그러면 코드는 아래와 같이 적을 수 있을 것 같습니다.

별로 어렵지 않은 것 같습니다. 아직 wire를 왜써야되는지 모르겠습니다. 그렇다면 좀 더 어려운 logic을 가져와볼까요?

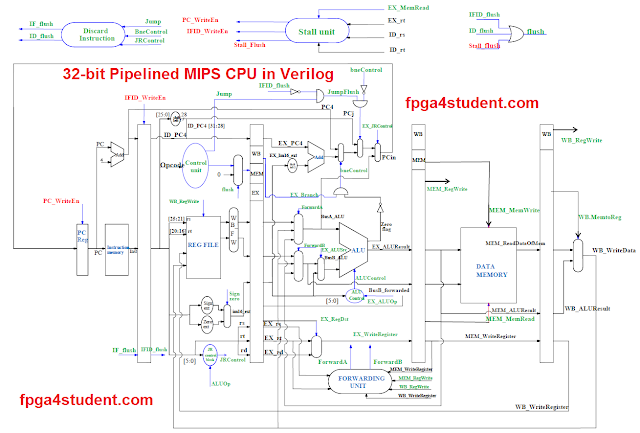

해당 module은 fpga4student라는 site에서 가져온 32bit MIPS processor입니다. 처음 마주치는 분들은 저게 뭐지 하면서 벙찔 수 있습니다.

자세히 말하면 이것은 많은 대학에서 '컴퓨터구조(Computer Architecture)'라는 강의를 진행할 때 가르치는 ISA(Instruction Set Architecture)의 일종인 MIPS instruction을 이해하고 수행할 수 있는 HW processor입니다.

간단히 말하자면 과거에 사용되던 CPU의 일종입니다. 즉 여러분의 컴퓨터, 스마트폰에 달려있는 CPU의 아주 초기버전이라고 볼 수 있습니다. 뭐 이게 뭔지 이해하는 건 여기서 다룰 내용이 아니니 일단 넘어갑시다.

(컴퓨터 구조를 안배우셨는데 CPU가 궁금하다 하면 해당 영상을 참고해주세요)

https://www.youtube.com/watch?v=Fg00LN30Ezg

여하튼 제가 하고싶은 말은 logic이 복잡해지면 저희가 위의 AND랑 OR연산으로 적는 것처럼 한번에 적기에 어렵다는 것입니다. 그래서 wire라는 문법이 존재하는데 wire는 앞서 말한 것처럼 element의 연결을 기술하는데 사용됩니다.

즉 여기서는 C처럼 A와 B의 AND연산의 결과를 OR gate에 연결해주는데 사용됩니다. 사용 방법은 C언어에서 변수를 선언하고 할당하는 것과 유사합니다. 그럼 wire를 이용해서 해당 코드를 다시 적어보도록 해보겠습니다.

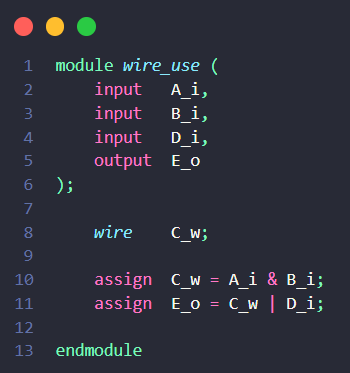

코드를 살펴봅시다.

1) input output을 기술하는 부분말고 logic을 기술하는 부분의 위에 C_w라는 wire를 선언합니다.

2) 그런다음 A와 B를 AND연산한 결과를 C_w에 연결합니다.

3) C와 D를 OR연산한 결과를 E에 연결합니다.

즉 여러분이 어느 부분을 다른 부분과 연결해야되는 경우 wire선언하고 assign구문을 이용해서 간단히 연결할 수 있습니다.

여기서 방금 제가 '연결'이라는 용어를 사용하였습니다. 이전까지 계속 SW와 HDL은 다르다고 말씀드렸는데 HDL에서 assign이라는 것은 '연결'을 의미합니다. 다음 내용은 약간 어려울 수 있으나 중요한 내용임으로 집중해주시길 바랍니다.

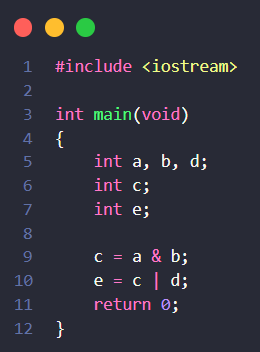

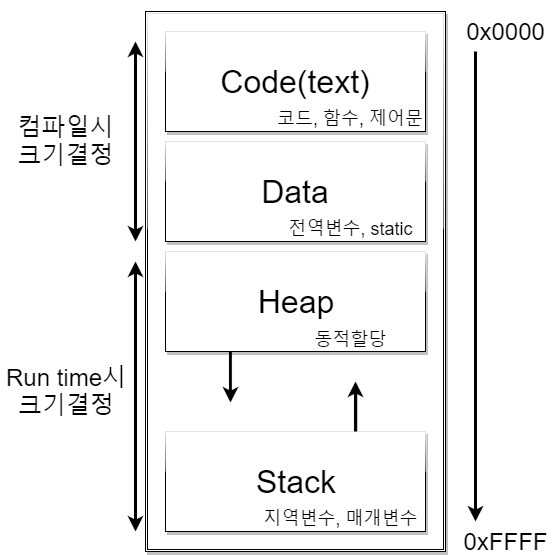

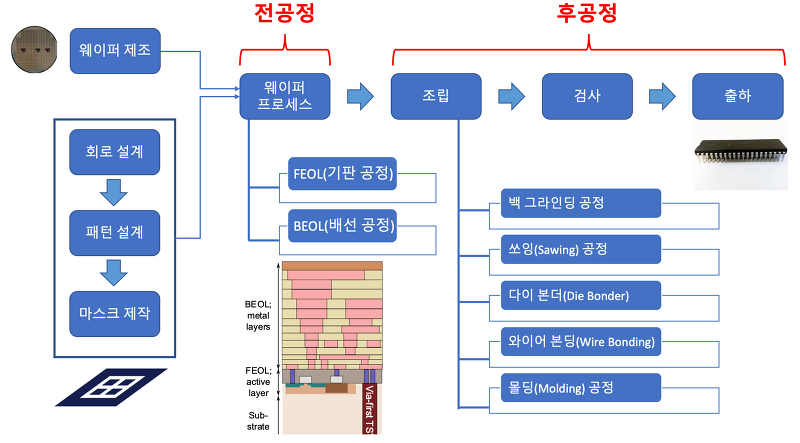

해당 코드와 같이 c(cpp)언어를 작성하면 컴퓨터에는 어떤 일이 일어날까요? a, b, c, d, e라는 변수(variable)이 생성된다고 알고 계실겁니다. 그렇다면 변수의 생성은 무엇을 의미하나요? C를 좀 더 자세히 배우신 분들이라면 a, b, c, d, e를 위한 '공간'이 컴퓨터의 memory에 할당(allocation)된다는 것을 알고 계실겁니다.

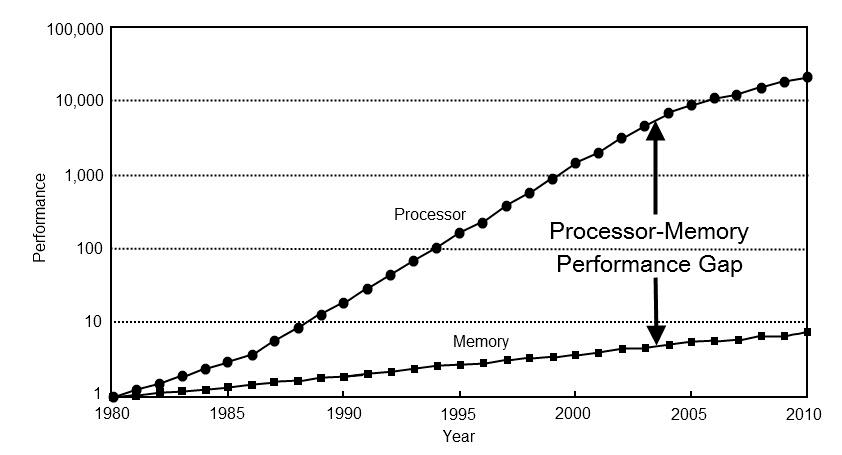

컴퓨터의 memory, 즉 스마트폰이나 노트북, 컴퓨터에서는 Cache나 DRAM(Dynamic Random Access Memory)의 일부를 해당 변수들을 위한 공간으로 프로그램에게 주어지고 여러분은 코드를 통해서 해당 공간을 이용할 수 있는 것입니다. 그렇다면 Verilog에서는 어떨까요?

Verilog는 이전에 말씀드린 것처럼 '기술'하는 언어이고, wire는 '연결'을 위한 문법이라 말씀드렸습니다. 즉, 왼쪽처럼 wire를 사용하나 오른쪽처럼 wire를 사용하지 않거나 둘다 물리적으로 뭔가 더 만들어지는(합성되는) 것은 아닙니다. wire라는 것을 선언한다고해서 뭔가 공간이 생성되거나 resource(자원)을 사용하는 것이 아니라는 의미입니다.

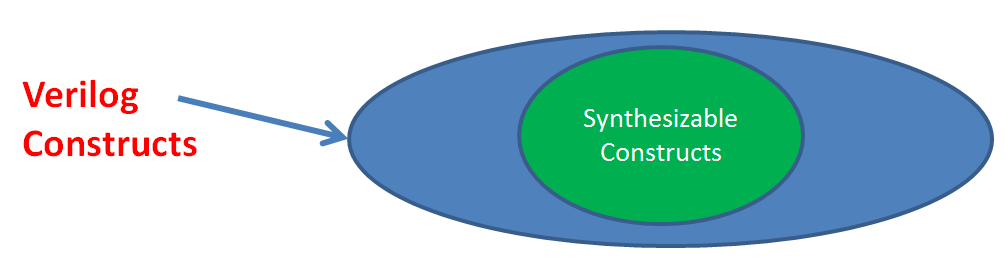

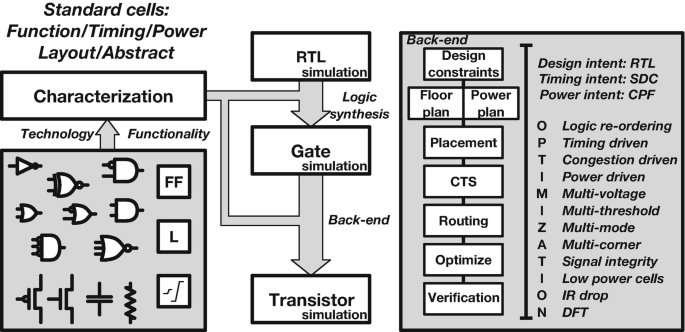

이것이 HDL을 배울 때 가장 유념해야되는 점입니다. 여러분은 본인이 의도한 회로를 설계하기 위해서, 검증하기 위해서 Verilog 코드를 이용할 것입니다. 여기서 가장 중요한 것은 여러분 본인의 '의도(Spec)'대로 '합성(Synthesis)'되는 코드를 작성하였는가 입니다.

반도체 분야가 크게 소자, 공정, 설계가 나뉘어 있는 이유는 해당 분야가 너무나 넓고, 방대하기 때문인데 공통의 목표는 '더 복잡하고 어려운 회로를 효율적으로 잘 만들어낼까'입니다. 그중 회로설계의 입장에서 기반이 되어야 되는 기초는 '어떻게하면 낭비없이 의도대로 설계할까' 입니다.

앞으로 포스팅을 따라오시면서 Verilog코드를 작성하실 때 머리에 염두해야 되는 내용이 바로 해당 코드는 어떤 식으로 합성될까? 입니다. 학부생 입장에서 저희가 실제 설계회사의 값비싼 합성툴을 만지거나 직접 chip을 구워보는 일은 접하기 어렵습니다.

그렇기에 실제 코드가 어떻게 합성되는지 눈으로 관찰하기도 현실적인 어려움이 따릅니다. 하지만 최소한 어떤식으로 합성될지 예측할 수 있어야 차후에 마주칠 timing, energy, resouce, bandwidth, latency 등 많은 문제들을 다룰 수 있습니다.

내용이 길었지만 결국 하고자 하는 말은 '의도한대로 합성 가능한 코드를 작성하자' 로 동일합니다.

다음 시간에는 HA(Half Adder)와 FA(Full adder)에 대해서 알아보도록 하겠습니다. 또한 이를 통해서 multi bit의 개념을 알아보겠습니다.

Code.

- github site 링크

https://github.com/gju06051/Verilog_study_public

REF.

-

Synthesisable VS non-Synthesisable code

https://asic-soc.blogspot.com/2013/06/synthesizable-and-non-synthesizable.html