지난 시간은 wire에 대해서 알아보았습니다.

이번 시간은 가장 기본 연산자들을 이용해서 adder를 설계해 봅시다.

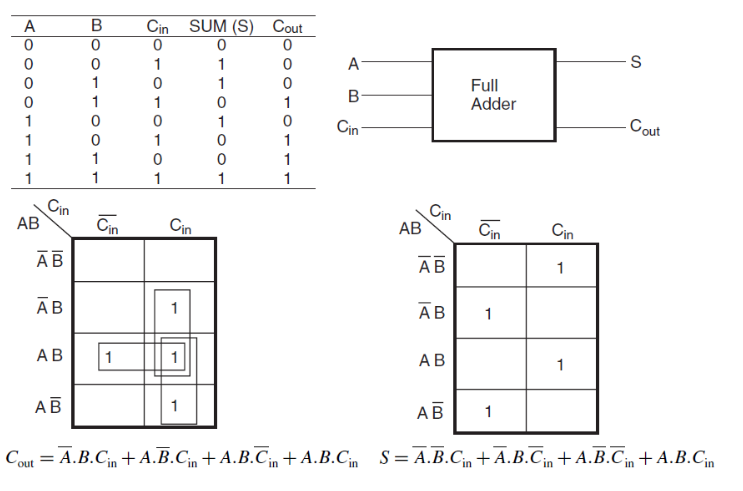

사실 뭐 adder를 설계하는 것이 어렵진 않습니다. 아마 여러분도 논리회로 시간에 full adder가 무엇인지, 어떻게 설계하는지 배우셨을 것입니다. 아마 정리해보자면

- truth table을 그린다.

- 카르노맵으로 정리한다.

- Boolean expression으로 나타낸다.

이런 과정이었을 겁니다. 오늘은 half adder, full adder를 다뤄보고 bit에 관한 얘기도 좀 나누고자 합니다. 더불어 concatenation이라는 문법도 다뤄볼 것입니다.

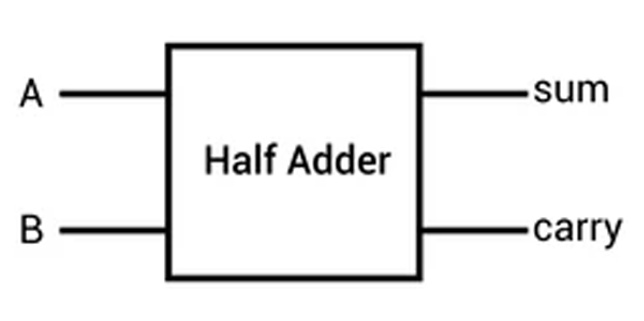

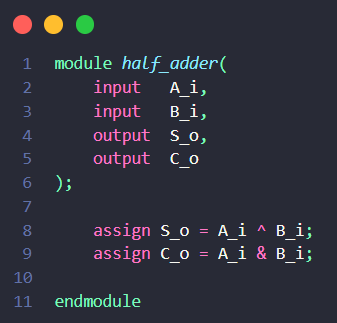

Half Adder

Half adder의 그림은 다음과 같습니다. Input으로 A와 B가 있고, Output으로 Sum과 Carry가 있습니다. 여기서 Sum이라는 것은 합을 Carry라는 것은 올림을 나타내는데 이를 모르시는 분들을 위해 예시로 설명드리겠습니다(아는 분들은 넘어가세요).

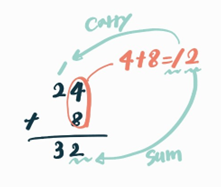

십진수로 24 + 8 = 32가 됩니다. 이 연산을 뜯어보면 1의 자리수 4 + 8이 12가 되는데 이는 10을 넘어감으로 carry를 발생시킵니다. 해당 carry는 10의 자리수 2와 더해져서 10의 자리수는 3이되고, 1의 자리수는 12에서 1의자리 2가 되어 결국 32라는 값이 나오는 것입니다.

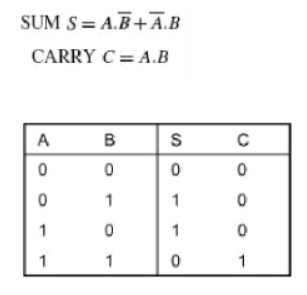

Truth Table(진리식)과 boolean expression은 다음과 같습니다. 이를 기반으로 Verilog코드를 작성하면 아래와 같이 나타납니다.

^연산자는 XOR인거 기억해주세요. 생각보다 회로 구성에 자주사용됩니다. Testbench도 github에 첨부해두었으니 다운로드 받아서 한번 확인해보세요.

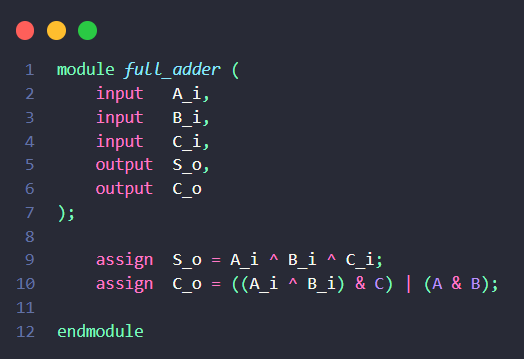

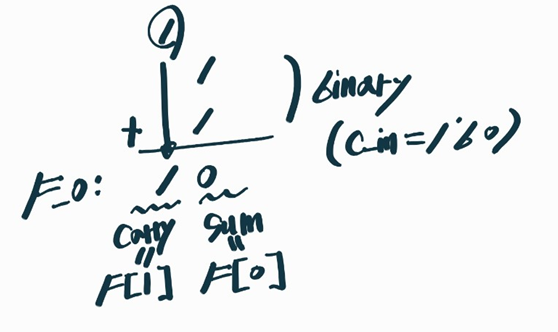

full adder에 대한 정보는 다음과 같습니다.

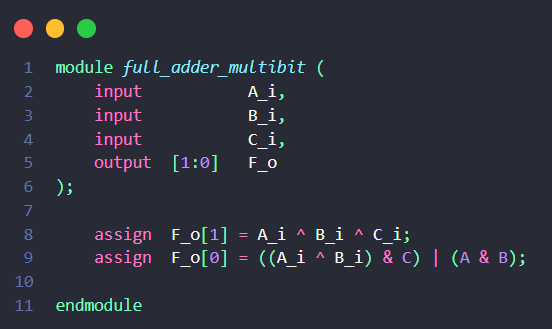

Input으로 A, B, C_in을 받고, Ouput으로 Sum, C_out을 출력합니다. 이를 그림 아래의 Boolean expresssion을 기반으로 Verilog코드를 이용해서 작성하면 아래와 같이 나옵니다.

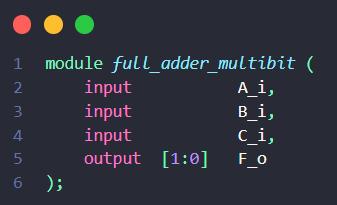

그런데 우리는 F = A + B와 같이 sum과 carry를 따로따로 나타내는 것이 아니라 그냥 결과값 하나에 나타내는 것에 익숙합니다. 지금까지 A, B, C, S 등 모든 변수는 1bit였습니다. 그런데 만약 다음과 같이 Sum과 Carry를 동시에 나타내려면 어떻게 해야될까요?

바로 output을 2bit로 선언해주시면 됩니다. 이를 위해서 2가지 문법을 오늘 다룰 것입니다.

- Multi bit 표현방법

- Concatenation

먼저 Multi bit를 표현하는 방법을 알아봅시다. Verilog에서 하나의 변수를 선언할 때 해당 변수가 지금까지처럼 1bit가 아니라 2bit, 3bit 등 multi bit를 나타내기 위해서는 다음과 같이 나타냅니다.

F_o라고 선언되어있는 output이 보이실 겁니다. 무언가 python에서 index slicing과 비슷하게 보이는데 Verilog에서 multi-bit를 나타낼 때는 다음과 같이 대괄호를 적고, ':'를 이용하여 범위를 구분해줍니다. 지금은 0부터 1까지를 나타내고 있는데 즉 0번째 1bit, 1번째 1bit로 총 2bit를 나타냅니다.

이는 python이나 c에서 array를 다루는 것처럼 index로 접근할 수 있습니다. Verilog에서는 index가 왼쪽이 높은 순으로 읽는데 위의 그림처럼 F라는 output의 1번째 자리가 carry이고, 0번째 자리가 sum임으로 이를 Verilog코드로 나타내면 아래와 같이 표현할 수 있습니다.

이렇게 왼쪽이 MSB(Most Significant Bit)를 나타내고 오른쪽이 LSB(Least Significant Bit)를 나타내는 것을 명심해주시고, 해당 변수가 몇 bit인지는 구간의 길이를 확인해보시면 됩니다. [1:0]과 같은 경우에는 1 - 0 + 1으로 2가되는 것을 알 수 있습니다.

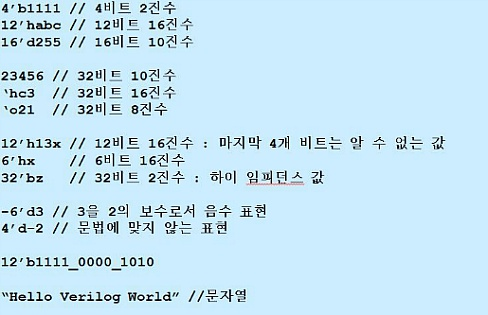

다음 concatenation을 배우기 앞서 Verilog에서 숫자를 표현하는 방법을 알아야되는데 Verilog에서 숫자를 표현할 때 ' 앞에 bit수를 적어주고 뒤에 영문은 binary(b)인지, decimal(d)인지 hexadecimal(h)인지 표현해줍니다.

예제

- 4'b1010 : 4bit, binary표현, 1010이라면 2^3 x 1 + 2^2 x 0 + 2^1 x 1 + 2^0 x 0 = 8 + 2 = 10(십진수)가 됩니다.

- 4'd10 : 4bit, decimal표현, 10^1 x 1 + 10^0 x 0 = 10으로 십진수 10을 나타냅니다.

- 4'hc : 4bit, hexadeciaml표현, c는 16진수의 12를 의미합니다.

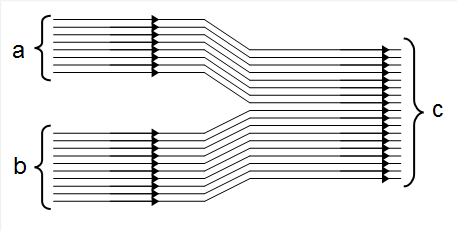

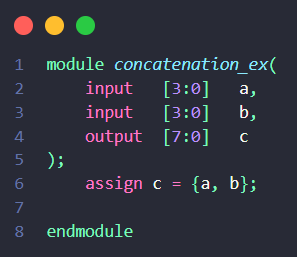

다시 돌아와서 F_o의 각각을 index로 표현해야 되는 문제가 있습니다. 이런 문제는 adder말고도 여러 회로에서 마주치는 경우인데 이를 위해 Verilog에서는 Concatenation이라는 문법을 가지고 있습니다. 여러 wire를 모아서 하나의 변수로 표현하는 경우를 위한 것인데 아래의 그림을 먼저 보겠습니다.

해당 그림처럼 a랑 b를 묶어서 하나의 변수 c로 사용하고 싶은 경우에 사용되는 operator로 기호는 중괄호 '{}' 입니다. 일단 한가지 예시를 들어보겠습니다.

해당 모듈은 위의 그림과 같이 단순히 a와 b를 concatenation해서 c에 연결하는 형태입니다. bit수는 뭐 그림과 같지는 않지만 4bit인 a와 b를 붙여서 8bit짜리 c에 연결되는 것을 볼 수 있습니다.

여기에 만약 a가 4'b0101이고, b가 4'b1111이라면 결과인 c는 8'b01011111이 되게 됩니다. a와 b가 중괄호에 적힌 순서 그대로 연결된다고 보시면 됩니다.

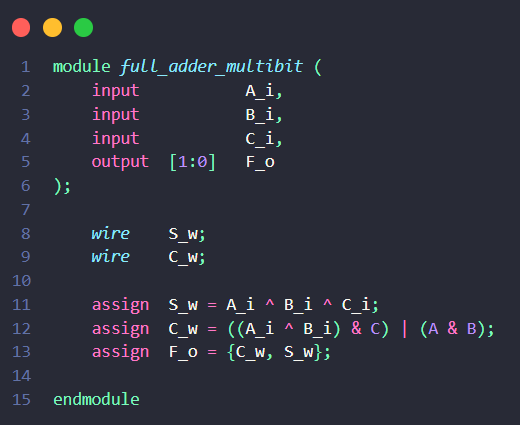

그러면 full adder의 예제에서는 어떤 식으로 F_o에 붙여서 표현할 수 있을까요?

해당 그림처럼 기존의 S_w와 C_w를 wire로 선언 이후에 계산 결과를 연결해주고 2개의 wire를 concatenation으로 F에 붙일 수 있습니다. 아직 concatenation의 효용성에 대해 얘기하기는 이른 것 같습니다. 그런데 회로설계에서 여러 wire를 묶어서 하나의 wire로 보는 경우는 매우 많이 발생하기 때문에 알아두시기 바랍니다.

이번 시간은 full adder 설계 및 concatenation, multi bit표현 등에 대해 알아보았습니다.

다음 시간은 현재 만든 full adder를 이용해서 4bit full adder를 설계해보면서 instination에 대해 알아보도록 합시다.

CODE.

- Github repo site

https://github.com/gju06051/Verilog_study_public

REF.