지난 시간에는 full adder와 cocatenation을 다뤄보았습니다. 이번 시간에는 4bit full adder를 설계하면서 instination에 대해서 알아봅시다.

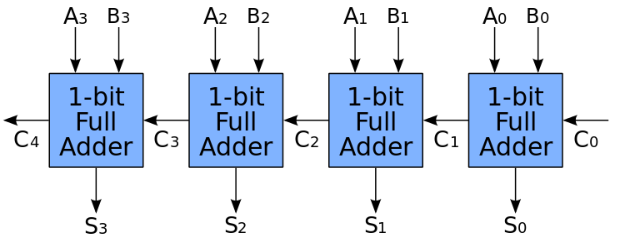

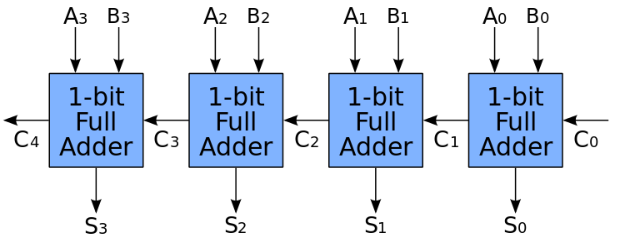

오늘 만들 4bit full adder는 RCA(ripple carry adder)의 형태로 full adder 4개를 이어서 만든 회로입니다. carry값이 ripple되는 형태라 저런 이름이 붙은 것으로 알고있습니다.

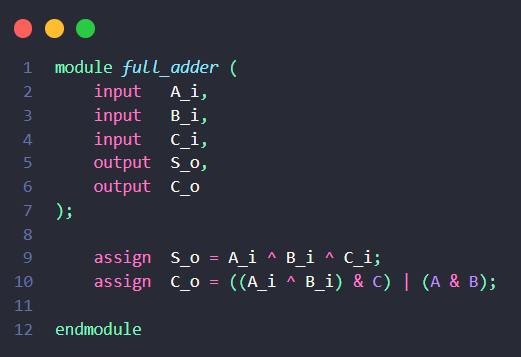

이것을 설계하기 위해서 어떻게 해야될까요? 저희가 지금까지배운 내용을 바탕으로라면 wire로 아래와 같은 코드의 C며 S며 각각 모두 선언하고 boolean 식을 계속 wire로 게속 연결해주어야 할 것입니다.

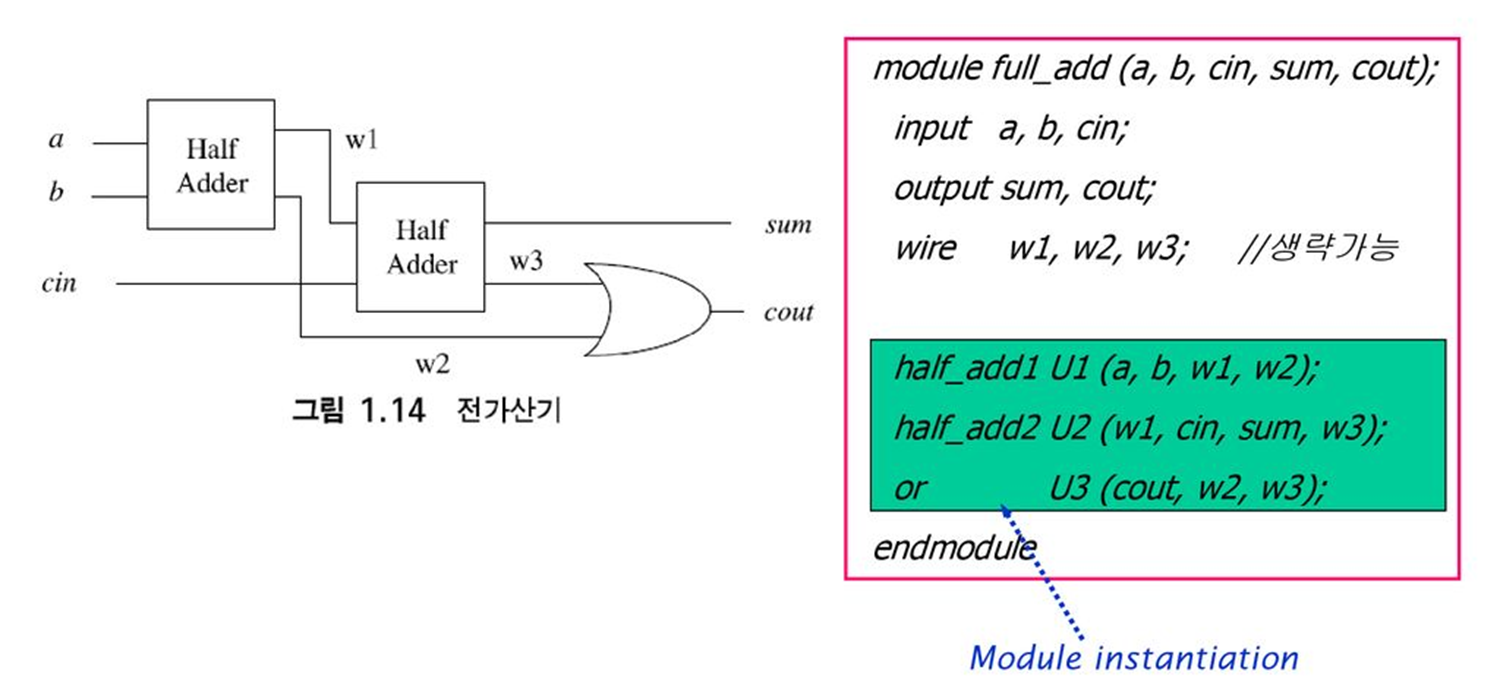

앞서 말씀드린 회로설계 내용에서 작은 module들이 연결되어 큰 모듈을 구성한다고 말씀드린적 있습니다. 당연히 Verilog는 이런 상황을 지원하는 문법이 존재하는데 오늘 배울 'instination'입니다. 직역하자면 호출, 인용이라는 뜻인데 어떠한 module에서 다른 module을 불러오는 것과 같습니다.

굳이 C언어로 비유하자면 function과 같은 느낌으로 받아드리시면 될거 같습니다.

(물론 동일하게 받아드리라는 말은 아닙니다)

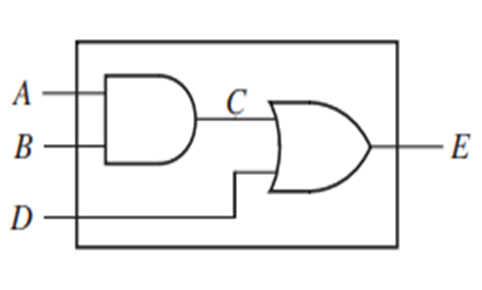

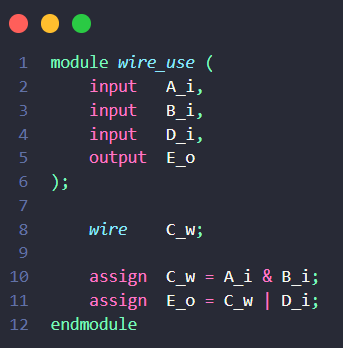

instination을 먼저 알아보기 위해서 이전에 사용하였던 위의 예제를 살펴봅시다. 해당 module은 AND gate와 OR gate로 구성되어 있는데 아래와 같이 wire와 and, or operator를 사용해서 해당 module을 설계하였습니다.

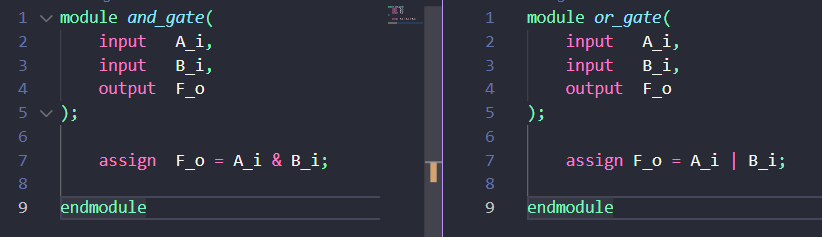

그런데 이번에는 '&'와 '|'을 사용해서 설계하는 것이 아니라 and_gate와 or_gate를 inst해서 사용해봅시다. and gate와 or gate는 아래와 같이 작성하였습니다.

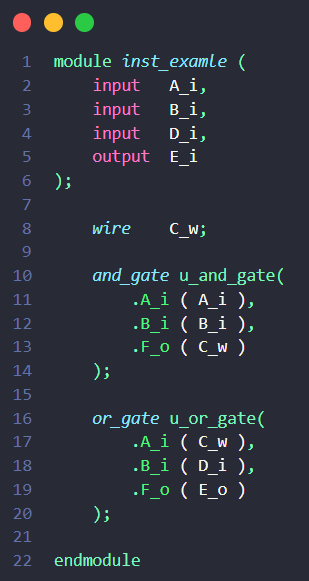

inst를 이용해서 해당 module을 구성하면 아래와 같이 기술할 수 있습니다.

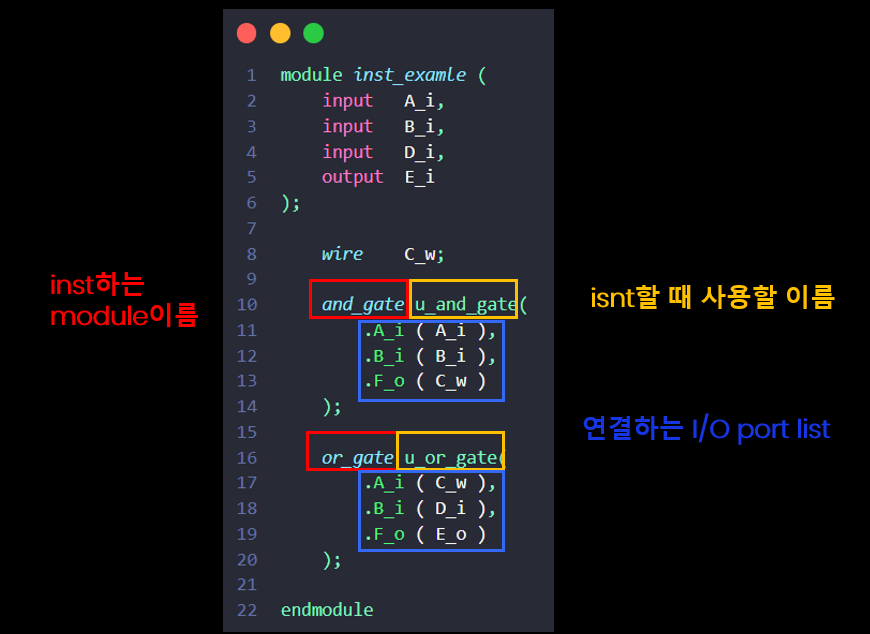

한번 잠시동안 살펴봅시다. 앞의 and_gate, or_gate는 저희가 and_gate, or_gate를 기술할 때 이름이고, 뒤의 u_and_gate, u_or_gate는 isnt할 때 사용하는 이름입니다. 그리고 아래 부분은 inst되는 I/O 포트와 현재 커다란 module사이에 연결을 위한 부분입니다.

왜 주황색 부분이 필요한지는 위의 4bit full adder를 생각해보면 됩니다. full adder 4개를 inst하게되면 어떤게 어디의 full adder인지 구분을 하기 위한 것이라 이해하실 수 있을겁니다.

파란 부분을 살펴보면 .뒤에 초록색으로 기술된 부분은 and, or gate내부의 I/O포트이고, 흰색 부분은 커다란 A, B, D를 input으로, E를 output으로 받는 module의 포트입니다. 자세히 보면 A와 B가 and gate로 들어가서 C로 결과가 나오고, C와 D가 or gate로 들어가서 E로 나오는 것을 알 수 있습니다.

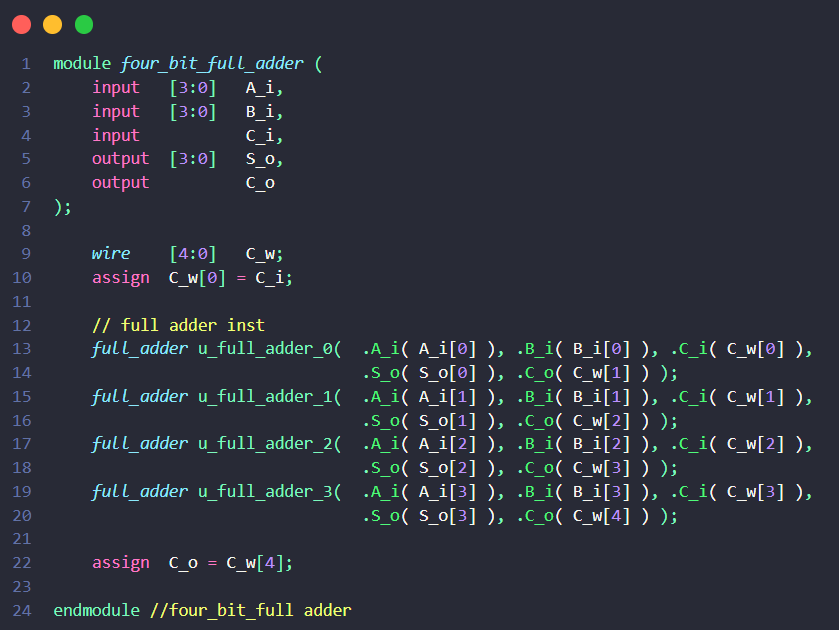

다시 원론으로 돌아와서 4bit full adder를 생각해봅시다. 저희는 full adder를 기존에 설계하였습니다. 4bit full adder는 이 full adder 4개로 구성되어 있습니다. 따라서 해당 full adder를 inst해서 4bit full adder를 만들 것입니다.

A와 B, S값은 4bit로 구성해주고 A[3]은 그림의 A3를 나타낸다고 생각하시면 됩니다.

C와 같은 경우에는 5bit로 선언해주도록 하겠습니다.

Verilog로 구성하면 다음과 같습니다.

이제 좀 코드가 길어지기 시작하나요? 길어보이지만 구성은 단순합니다. full adder를 4개 inst해와서 각각을 그림과 같이 연결해준 과정입니다. inst할때 full adder별로 녹색 부분에 이름이 다른 것과 파란색 부분의 이름이 동일한 것을 잘 확인해주시고, port끼리 연결이 어떤 식으로 되었는지도 한번 그림과 비교해보면서 파악해보시길 바랍니다.

이렇게 작은 모듈들이 모여서 복잡한 회로들을 구성하게 되고 이를 통해서 우리는 일상생활의 많은 여려움과 불편한 점들을 해소해왔습니다. 이번 글은 여기서 마치며 다음 시간에는 testbench에 대해 알아보도록 하겠습니다.

CODE.

- github repo 링크

https://github.com/gju06051/Verilog_study_public

REF.

-

4bit full adder 사진

https://ko.m.wikipedia.org/wiki/%ED%8C%8C%EC%9D%BC:4-bit_ripple_carry_adder.svg -

full adder instination 사진

한밭대학교 반도체 설계 실습 https://slidesplayer.org/slide/14073261/