나는 흐름이 있는 공부방식을 선호한다. 바로 전 글의 ISA가 어떤지에 대해 배웠고,RISC와 CISC 의 특징 및 차이점, 5가지의 ISA ISSUE 에 따른 각각이 무엇을 뜻하는지 알아 봤다.

ISA의 기초적인 부분을 배웠기에 ISA 중 하나인 RISC-V는 어떤 특성을 가지는지를 배울수 있다 생각한다.

그런 방식으로 계속 흐름이어가면서 공부해보자.

operand는 어디에 저장되는지

연산자는 얼마나 많은지

메모리에 어떻게 접근하는지

피연산자의 크기와 타입

어떤 연산자가 지원되는지.

이제 우리는 RISC-V 의 각각은 어떠한지에 대해 알아볼것이다.

먼저 RISC-V Architecture 은 R-R ISA 방식이다.

CPU는 Register에서만 연산을 한다는 말인데.

Memory에서 Register에 값을 Load 하고 Register에서 명령어를 수행한다는 말이다.

1) What is RISC-V Architecture?

1) where are operands stored?

먼저 RISC-V 는 32개의 General Purpose Register 를 가지고 1개의 특별한 Register(PC)를 가진다. 이는 Integer Register만 나타낸것이다.

각 Register Size는 64-Bit 이다.

2) How many explicit operands are there?

전 글에서 RISC 방식은 피연산자의 개수가 Register-Register 이라 설명한적이 있다.

피연산자 중 Memory는 0 Register는 3개이다.

3) How is the operand location specified (How to access memory)

64비트에서는 메모리의 주소가 0~2의 64제곱 -1 까지 이다.

Data는 Memory와 Register 사이에서 8Byte 단위로 끊겨서 이동된다.

근데 명령어는 4Byte 씩 끊겨서 이동된다.

이거 왜일까?

일단 RISC 방식에서 명령어의 크기는 4B로 고정된다.

명령어의 크기를 8B로 바꾸게되면 기계어의 문법을 바꿔야하고

그렇게 되면 전체적인 프로그램을 다 바꿔야하기 떄문이다!

4) what type & size of operands are supported?

생략

5) what operations are supported?

생략

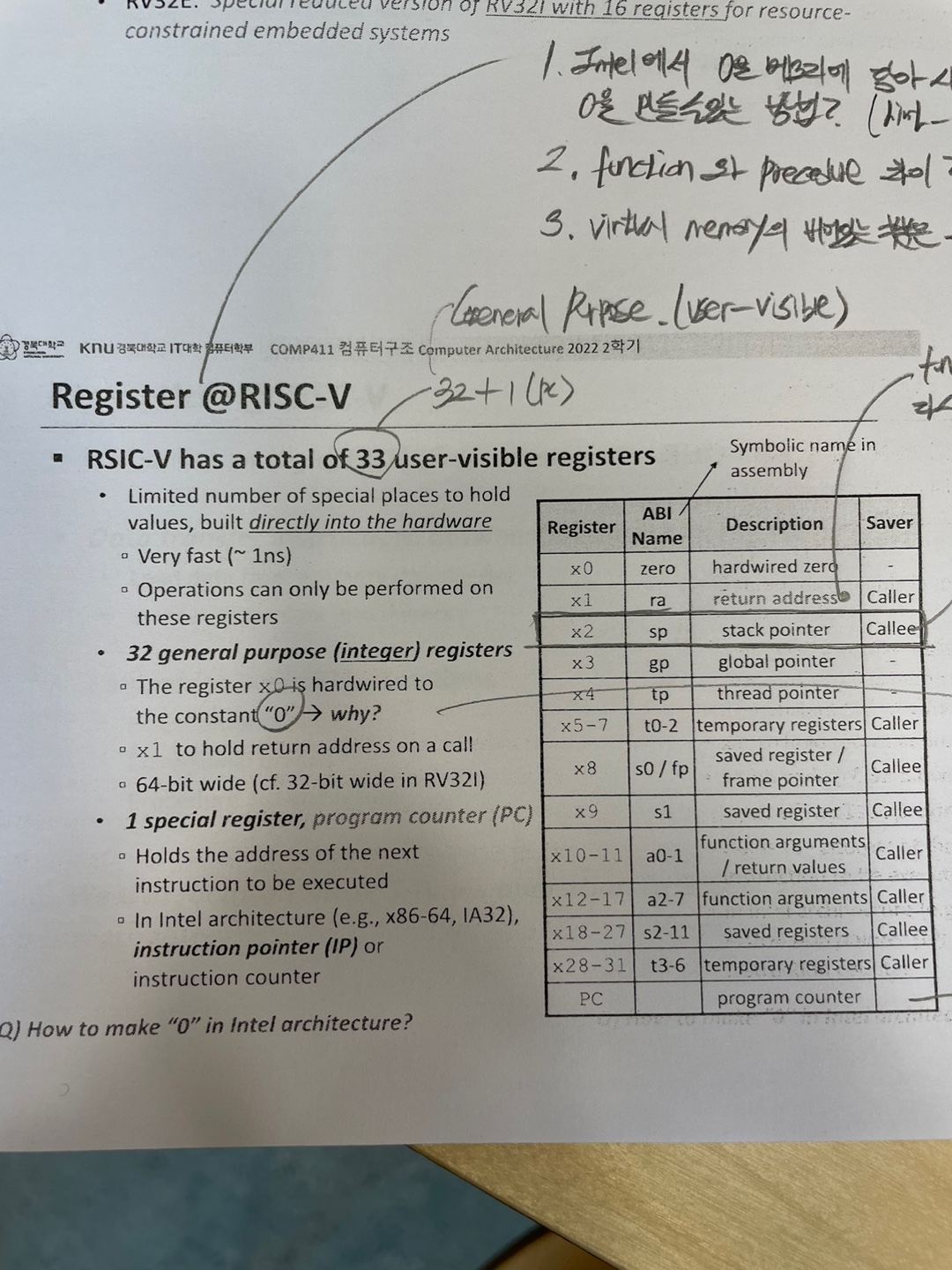

2) Register @RISC-V

RSIC-V 는 33개의 유저에게 보여지는 Register 들이 있다.

(32+pc)

각각 하는 일들이 다른데

x0은 0이란 값으로 Fix 되어있다.

0을 자주 사용하기에 0이 사용될때는 메모리에가서 접근하지말고 그냥 상수로 0을 사용하기위해 x0은 0으로 되어있는것이다.

X1은 function call 하고나서 다시 돌아갈 위치를 말하고

x2는 Stack Top 위치이다.