아무리 CPU를 Tomasulo 알고리즘으로 화려하게 설계해도, 데이터를 담고 있는 메모리가 느리면 CPU는 멍하니 기다려야 합니다. 이를 'Memory Wall' 문제라고 부릅니다. 이 벽을 깨기 위한 하드웨어의 노력을 파헤쳐 봅시다.

1. 지역성의 원리 (Principle of Locality)

캐시가 존재하는 근본적인 이유입니다. 프로그램은 데이터를 무작위로 쓰지 않습니다.

시간적 지역성 (Temporal Locality): 한 번 접근한 데이터는 조만간 또 접근할 가능성이 높다. (예: 반복문의 변수)

공간적 지역성 (Spatial Locality): 특정 데이터에 접근하면 그 주변 데이터도 같이 쓰일 가능성이 높다. (예: 배열 순회)

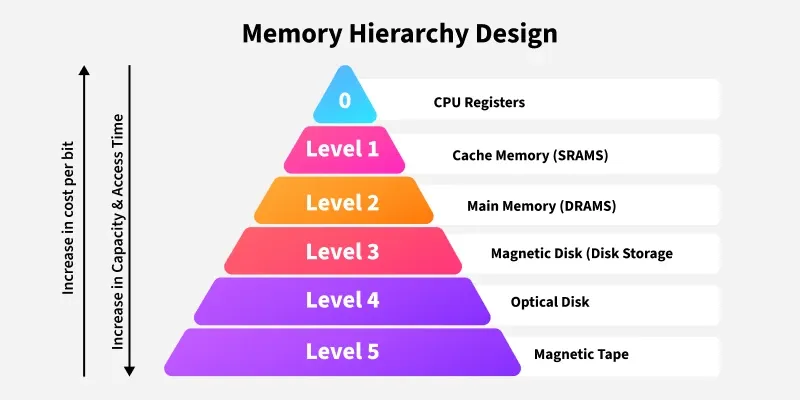

2. 메모리 계층 구조 (Memory Hierarchy)

상위로 갈수록 빠르고 비싸며 용량이 작고, 하위로 갈수록 느리고 저렴하며 용량이 큽니다.

Registers: CPU 내부. (1 cycle 미만)

L1, L2, L3 Cache: CPU 근처 SRAM. (수~수십 cycle)

Main Memory (DRAM): 우리가 흔히 말하는 RAM. (수백 cycle)

3. 캐시 매핑 방식 (Cache Mapping) - 시험 단골 문제

메모리의 데이터를 캐시의 어느 위치에 저장할 것인가에 대한 규칙입니다.

Direct Mapped Cache: 메모리 주소에 따라 캐시 내 자리가 딱 정해져 있는 방식. (설계는 쉽지만 충돌이 잦음)

Fully Associative Cache: 캐시의 아무 빈자리나 들어갈 수 있는 방식. (찾기가 힘들고 하드웨어가 복잡함)

Set-Associative Cache (현대 표준): 위 둘의 절충안. 캐시를 여러 개의 'Set'으로 나누고, 특정 주소는 지정된 Set 내의 아무 칸에나 들어갈 수 있습니다.

4. 캐시 미스 (Cache Miss)의 3요소 (3C's)

교수님이 "캐시 미스를 줄이려면 어떻게 해야 할까?"라고 물으시면 이 세 가지 카테고리로 답해야 합니다.

Compulsory Miss (강제 미스): 처음 불러오는 데이터라 생기는 미스. (해결: Prefetching - 미리 가져오기)

Capacity Miss (용량 미스): 캐시 용량이 부족해서 생기는 미스. (해결: 캐시 크기 키우기)

Conflict Miss (충돌 미스): 자리는 비었는데 매핑 규칙 때문에 겹쳐서 쫓겨나는 미스. (해결: Associativity 높이기)

석사 과정 심화 주제: Cache Coherence (캐시 일관성)석사 수업(Advanced)에서는 코어가 여러 개인 멀티코어 시스템을 다룹니다. 이때 아주 골치 아픈 문제가 생깁니다."코어 1이 변수 를 10으로 바꿨는데, 코어 2의 캐시에는 여전히 가 5라고 되어 있다면?"이것이 Cache Coherence 문제이며, 이를 해결하기 위한 MESI 프로토콜 같은 메커니즘을 배우게 됩니다. 각 캐시가 서로의 상태를 감시(Snooping)하며 데이터의 일관성을 유지하는 기술이죠.