이 강의는 하드웨어 검증 교육을 위해 자체 제작된 가상의 모듈인 'Aligner (정렬기)'의 구조와 동작 사양을 설명하는 튜토리얼입니다.

강의의 핵심 내용은 이 Aligner가 외부 인터페이스(RX, TX, Register)를 통해 어떻게 데이터를 주고받고 동작하는지, 그리고 검증 엔지니어로서 어떤 기능들을 테스트해야 하는지 파악하는 것입니다.

Universal Verification Methodology (UVM) is the industry-standard modular framework used to verify complex digital designs (ASIC/FPGA). Built on top of SystemVerilog, it provides a structured library of classes and a "manual" on how to build a verification environment that is reusable, scalable, and robust

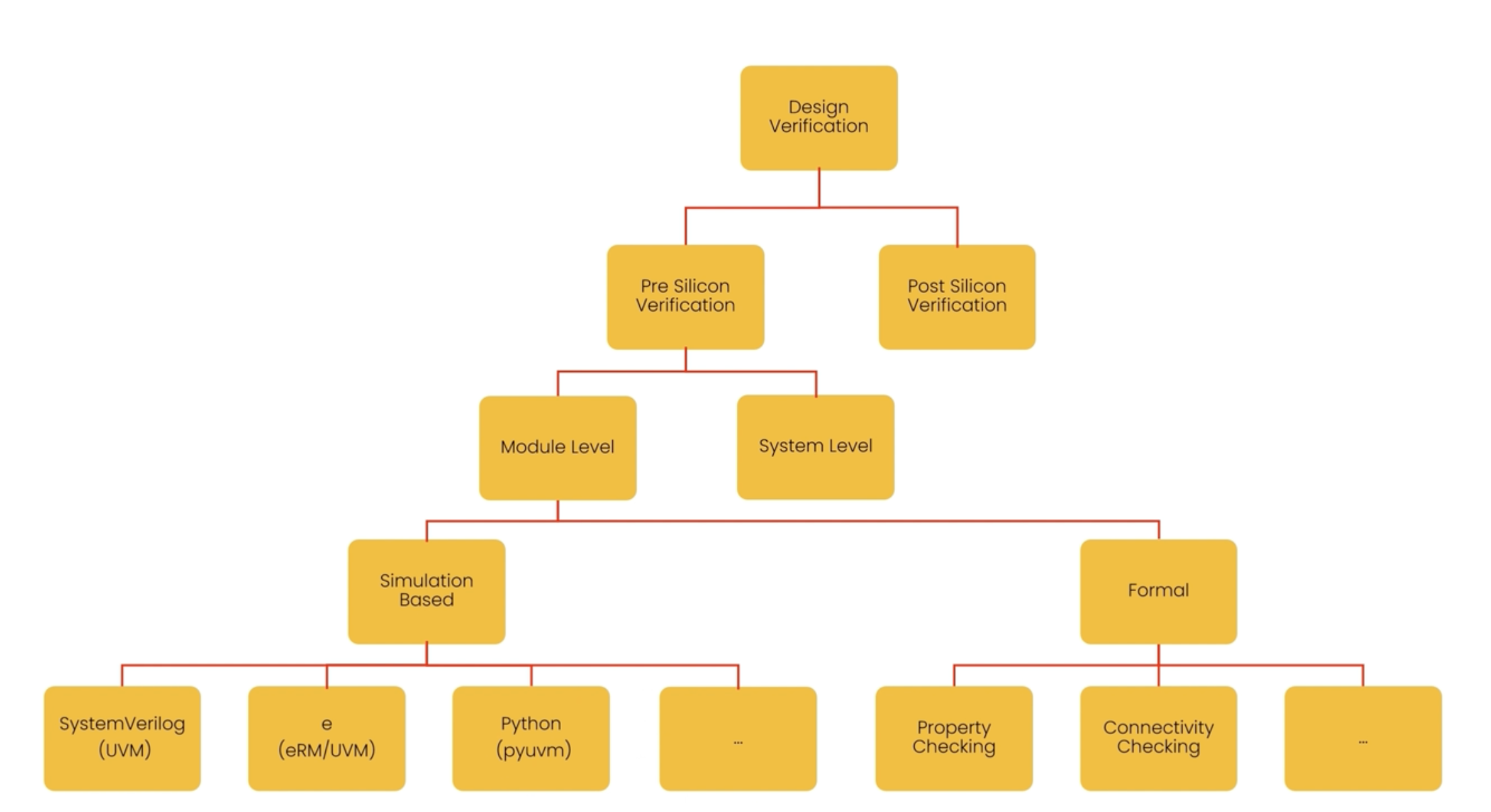

What is Design Verification

하드웨어 검증의 분류 (Verification Tree)

Post-silicon Verification (실리콘 생산 후): 실제 웨이퍼나 패키징된 물리적 칩을 테스트 장비에 연결하여 버그와 제조 결함을 찾는 과정입니다.

Pre-silicon Verification (실리콘 생산 전): 칩을 굽기 전, Verilog/VHDL 등으로 작성된 RTL 코드 상태에서 논리적인 오류를 찾는 과정입니다.

강의에서는 Pre-silicon Verification을 다시 두 가지 레벨로 나눕니다.

System-level: 모든 모듈을 다 합친 전체 칩 단위의 검증.

Module-level: 전체 칩을 구성하는 개별 블록(예: 통신 컨트롤러, CNN 가속기 등) 하나하나를 떼어내서 독립적으로 검증.

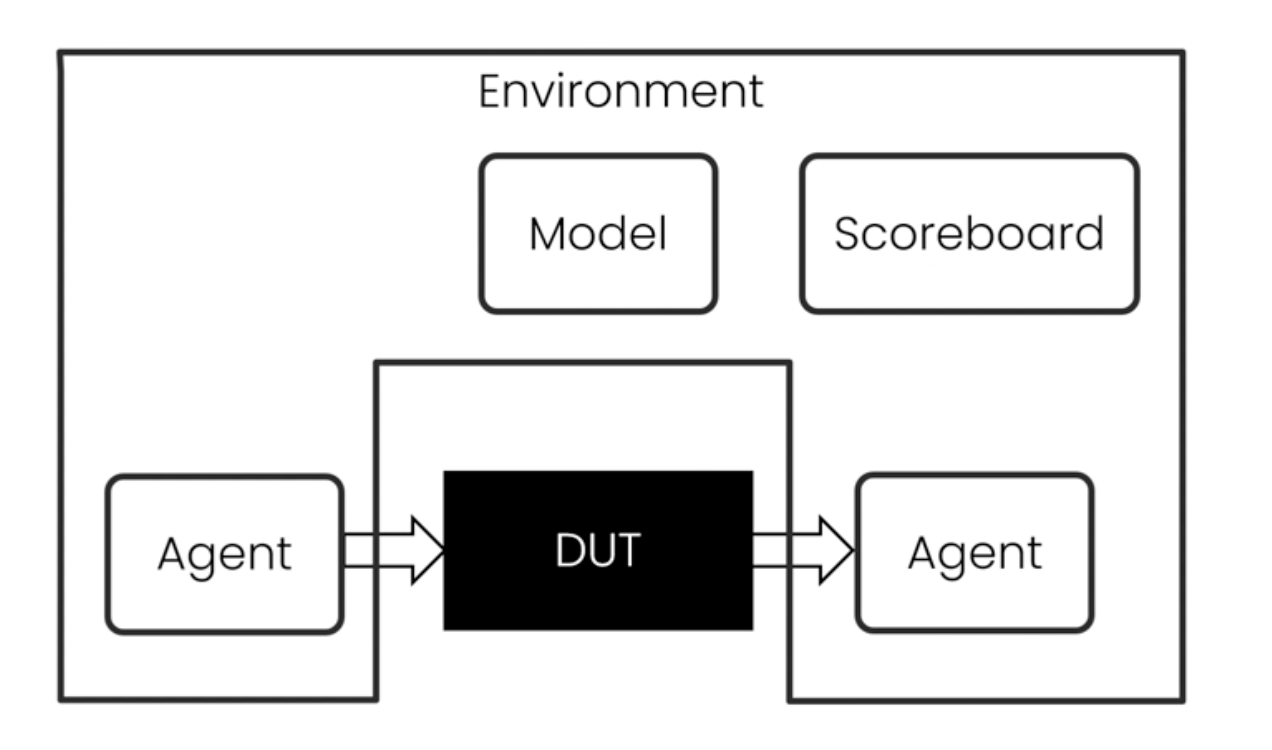

- 하나는 Agent->DUT->Agent를 통과하고, (TEST)

- 다른 하나는 Agent -> Model을 통과한다 (정답지)

- 위 두 결과를 Scoreboard에서 같은지 다른지 확인한다

Agent (에이전트):

DUT의 입력과 출력 인터페이스에 딱 달라붙어 있는 컴포넌트입니다.

랜덤한 트랜잭션 데이터를 생성해 DUT의 입력단으로 밀어 넣고(Drive), DUT에서 튀어나오는 출력 신호를 관찰(Monitor)하여 데이터를 수집합니다.

설계자가 짠 RTL 모듈(DUT)에 끊임없이 랜덤 데이터를 쏟아붓고(Agent), 그 결과가 이상적인 소프트웨어 정답지(Model)와 일치하는지 자동 채점(Scoreboard)하는 소프트웨어 인프라(Environment)를 만드는 것. 이것이 바로 UVM 검증입니다.

Aligner

1. Aligner의 핵심 기능

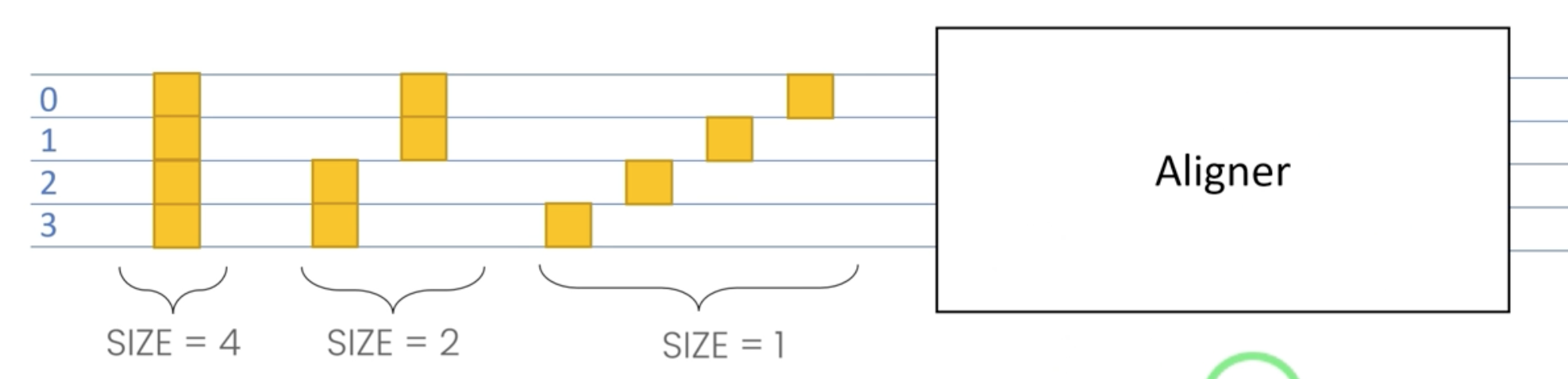

데이터 정렬 (Data Alignment)

Aligner의 주된 역할은 RX(수신) 인터페이스로 들어온 정렬되지 않은 데이터를 내부적으로 모아, 지정된 규칙에 맞춰 정렬한 뒤 TX(송신) 인터페이스로 내보내는 것입니다.

-

데이터 버스 구조: RX와 TX 인터페이스 모두 32-bit (4 Bytes) 넓이를 가집니다. 이를 4개의 'Lane (0~3)'으로 부릅니다.

-

Size와 Offset: 입력 및 출력 데이터의 유효한 위치와 크기를 결정하는 두 가지 핵심 파라미터입니다.

-

Size: 몇 바이트(Lane)의 데이터가 유효한지 나타냅니다. (1, 2, 4 가능 / 3은 불법)

-

Offset: 유효한 데이터가 시작되는 위치(Lane 번호)를 나타냅니다.

-

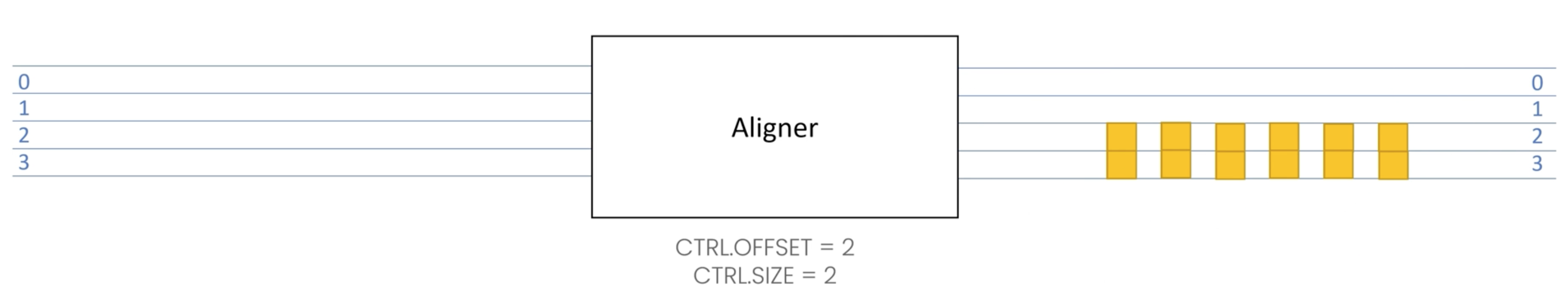

동작 예시: 사용자가 레지스터를 통해 출력 방식을 Size=2, Offset=2로 설정했다면, Aligner는 RX로 들어오는 데이터를 계속 모으다가 2바이트가 채워지는 순간, TX 인터페이스의 Lane 2와 3을 통해 데이터를 전송합니다.

데이터가 받고, 전송될 수 있는 size와 offset

size 4, offset 0

size 2, offset 0,1

size 1, offset 0,1,2,3

위에 사진이 Aligner에 의해 이렇게 재 배열된다

2. 내부 구조 및 상태 확인 (RX / TX FIFOs)

Aligner 내부에는 데이터를 임시로 저장하는 버퍼인 FIFO(First-In-First-Out)가 존재합니다.

- RX FIFO: 합법적인 RX 트랜잭션이 들어오면 이곳에 쌓입니다.

- Controller: RX FIFO에서 데이터를 꺼내 정렬 규칙에 맞게 데이터를 쪼개거나 합친 뒤 TX FIFO로 보냅니다.

- TX FIFO: 정렬이 완료된 데이터가 이곳에 쌓이고, 이후 TX 인터페이스를 통해 밖으로 전송됩니다.

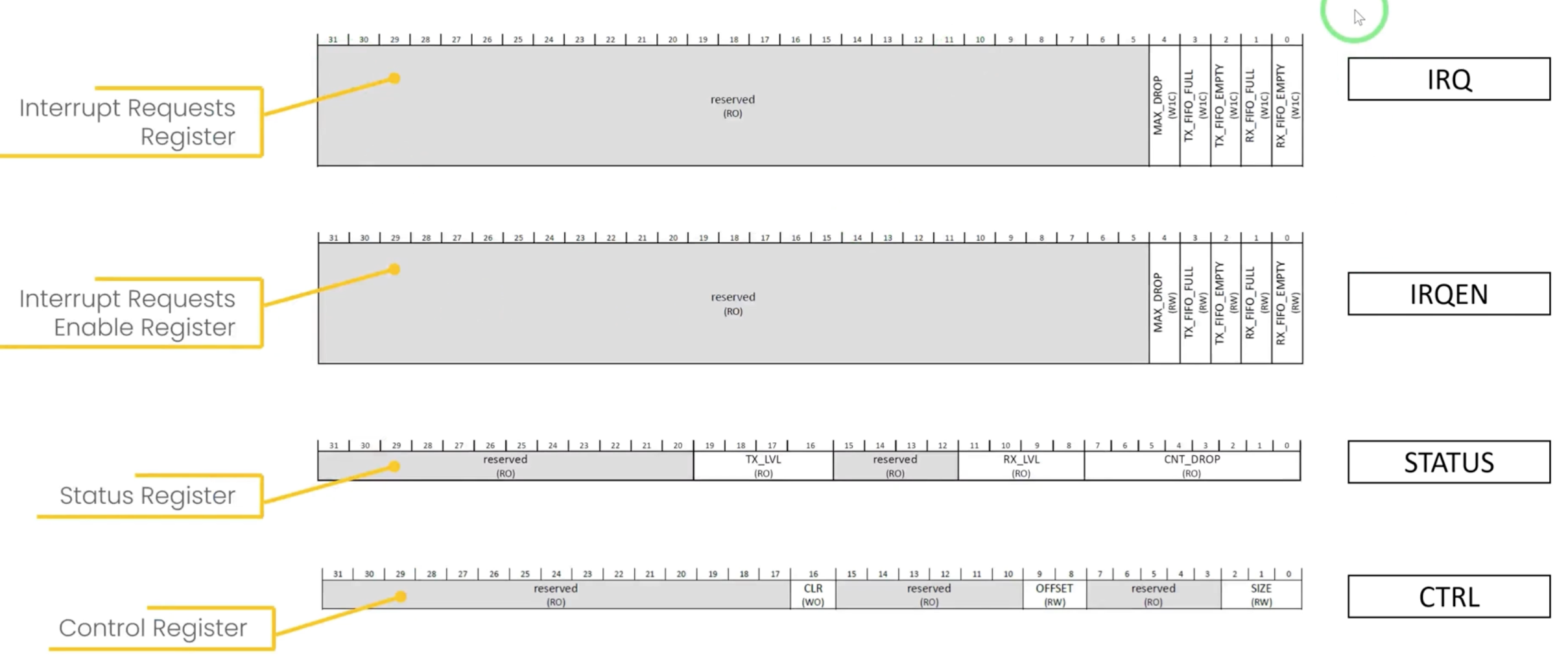

- 상태 레지스터(Status Register)를 통해 현재 RX FIFO와 TX FIFO에 몇 개의 '트랜잭션(바이트 수가 아님)'이 들어있는지 레벨을 확인할 수 있습니다.

3. 에러 처리 및 인터럽트 (Drop Counter & Interrupts)

Aligner는 잘못된 입력이나 내부 상태 변화를 감지하고 처리하는 기능이 있습니다.

-

Drop Counter (드롭 카운터): RX 인터페이스로 불법적인 조합(예: Size=3 또는 Size=2, Offset=1)이 들어오면, Aligner는 에러 응답을 보내고 해당 트랜잭션을 버립니다(Drop). 이때 내부에 있는 Drop Counter가 1씩 증가합니다. 최대 255까지 증가하며 다시 0으로 돌아가지 않습니다. (Clear 레지스터를 통해 초기화 가능)

-

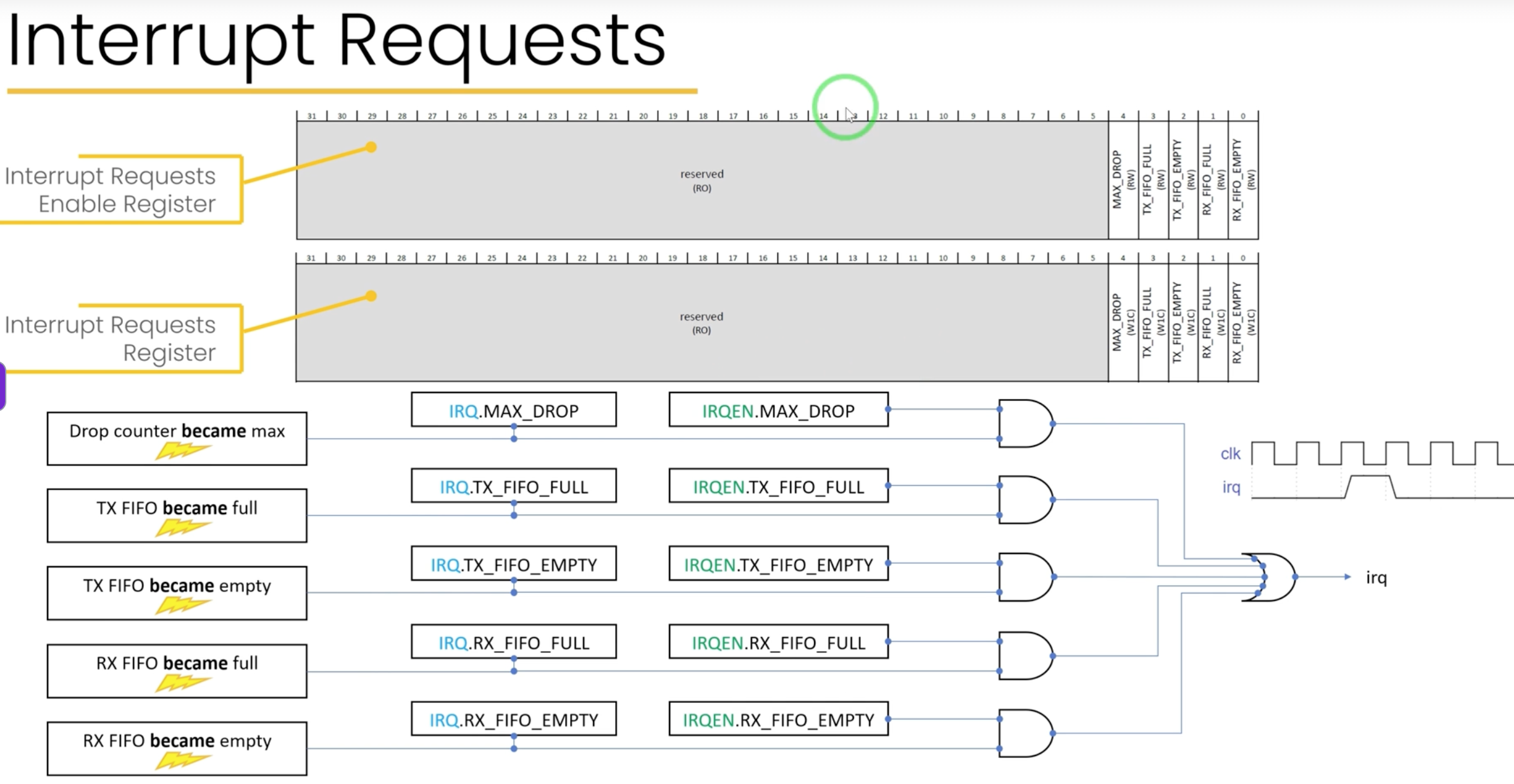

Interrupt Requests (인터럽트 요청): 특정 이벤트가 발생하면 외부에 알림(Pulse 신호)을 보냅니다.

-

인터럽트 발생 조건 5가지: Drop Counter 최대치 도달, RX FIFO Full/Empty, TX FIFO Full/Empty.

-

Enable 레지스터를 통해 특정 인터럽트만 켤 수 있으며, 발생한 인터럽트 기록은 'Write 1 to Clear' 방식으로 지울 수 있습니다.

4. 외부 인터페이스 프로토콜 (APB & MD)

- h1, h2 는 illegal 이라서 오류뜸

- rx에서 받느 앞에 3개를 합쳐 아래 tx가 됨

Aligner는 외부와 통신하기 위해 두 가지 프로토콜을 사용

1. APB Protocol (레지스터 제어용):

업계 표준 프로토콜로, Aligner 내부의 4개 레지스터(Control, Status, Interrupt Enable, Interrupt Request)를 읽고 쓰는 데 사용됩니다. PSEL, PENABLE, PWRITE 등의 신호를 사용해 Setup 단계와 Access 단계로 나뉘어 통신합니다. 잘못된 주소나 읽기 전용 레지스터에 쓰기를 시도하면 에러(PSLVERR)를 뱉어냅니다.

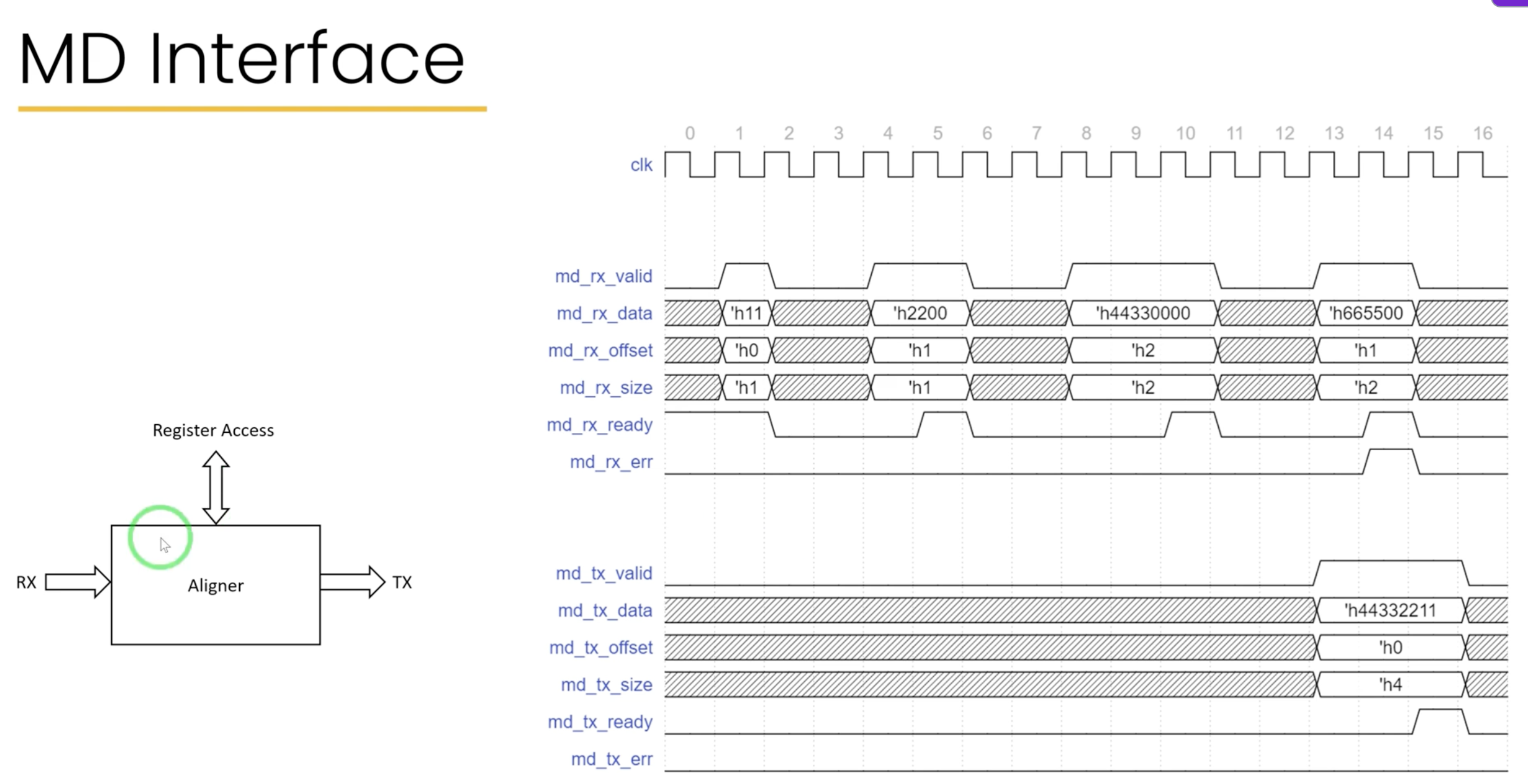

2. MD Protocol (RX/TX 데이터 전송용):

이 교육을 위해 임의로 만들어진(Memory Data) 프로토콜입니다. valid 신호와 ready 신호가 동시에 High가 될 때 한 번의 트랜잭션이 완료되는 전형적인 핸드셰이크(Handshake) 방식을 취하고 있습니다.