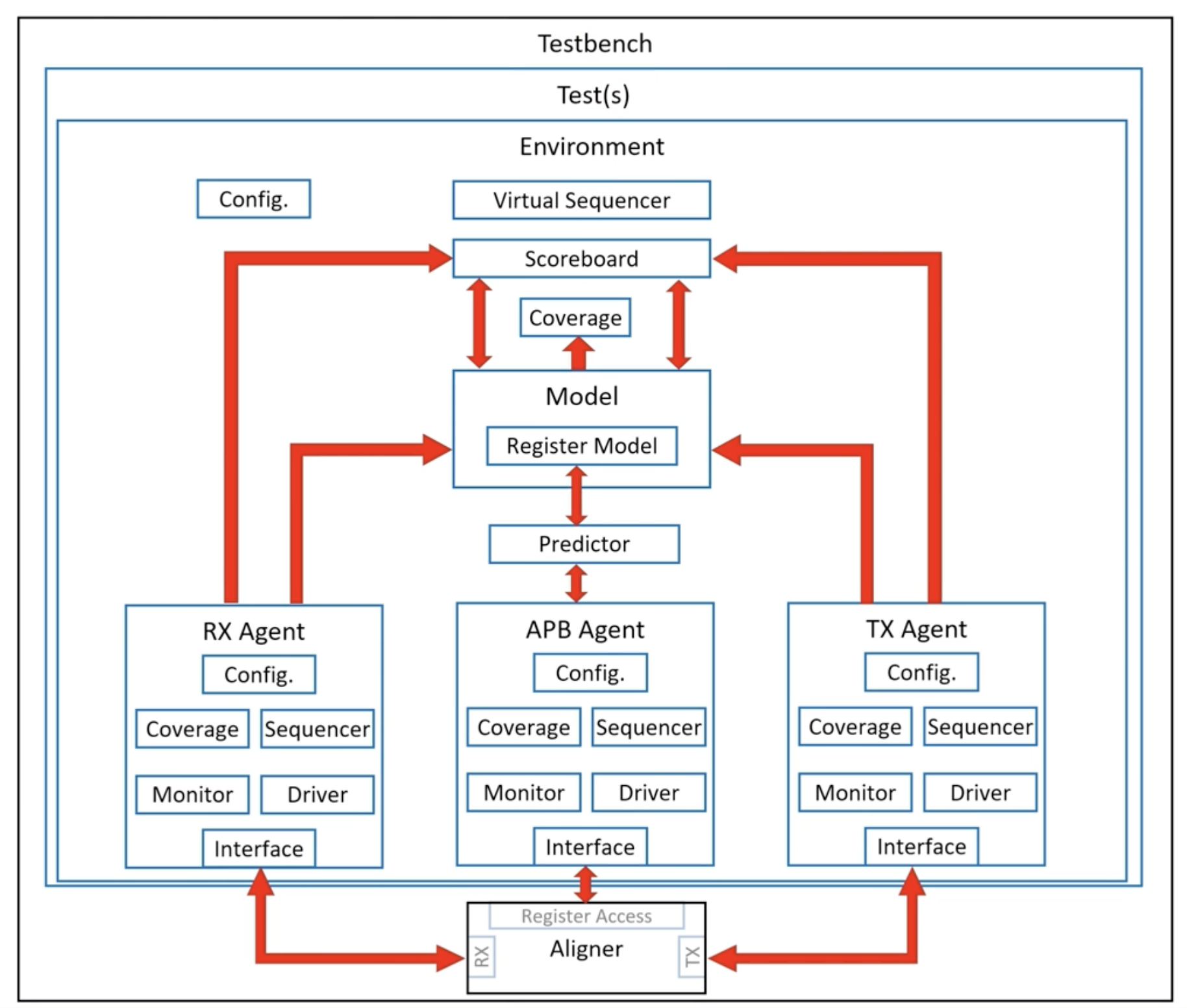

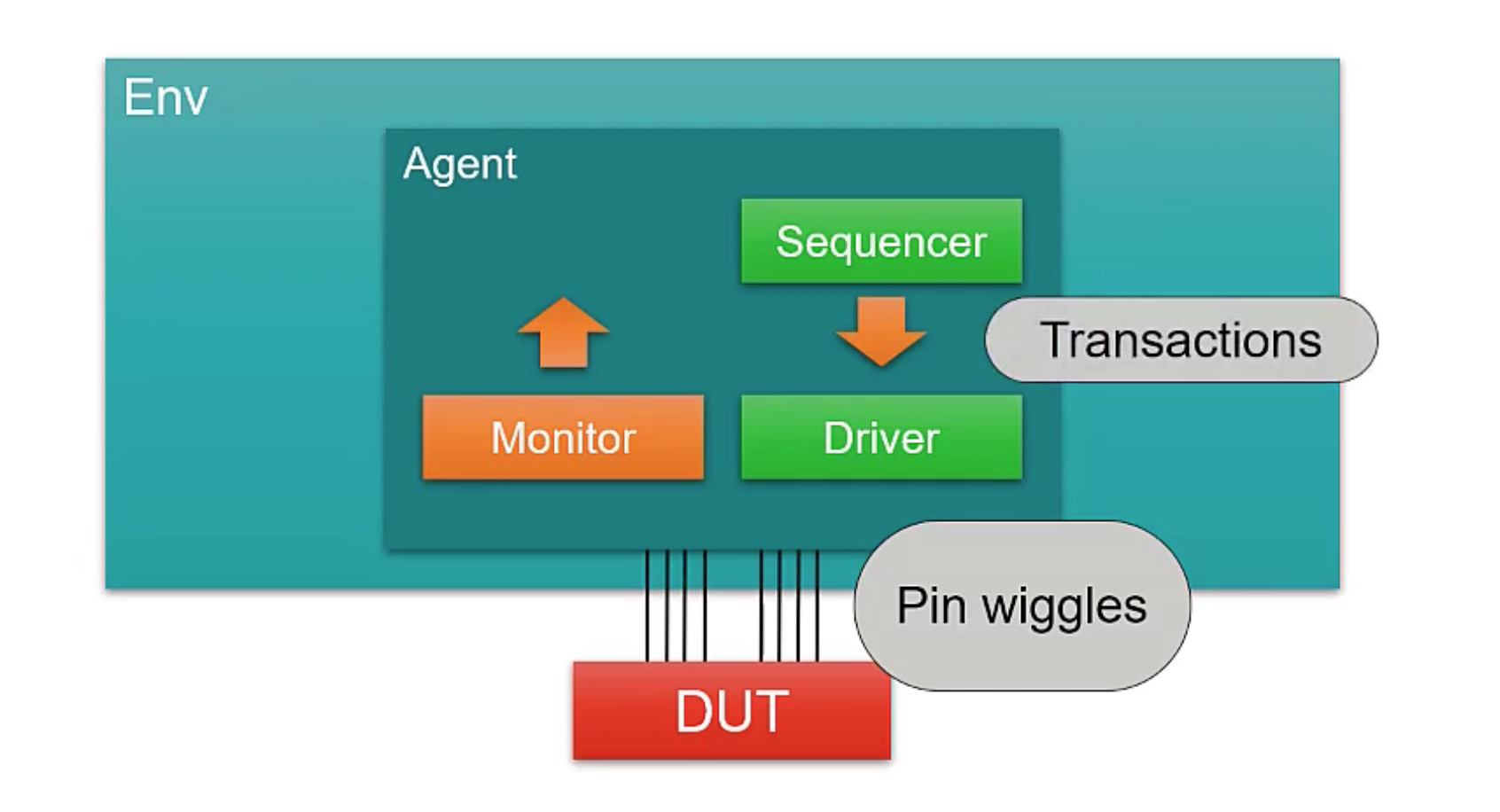

Environment Architecture

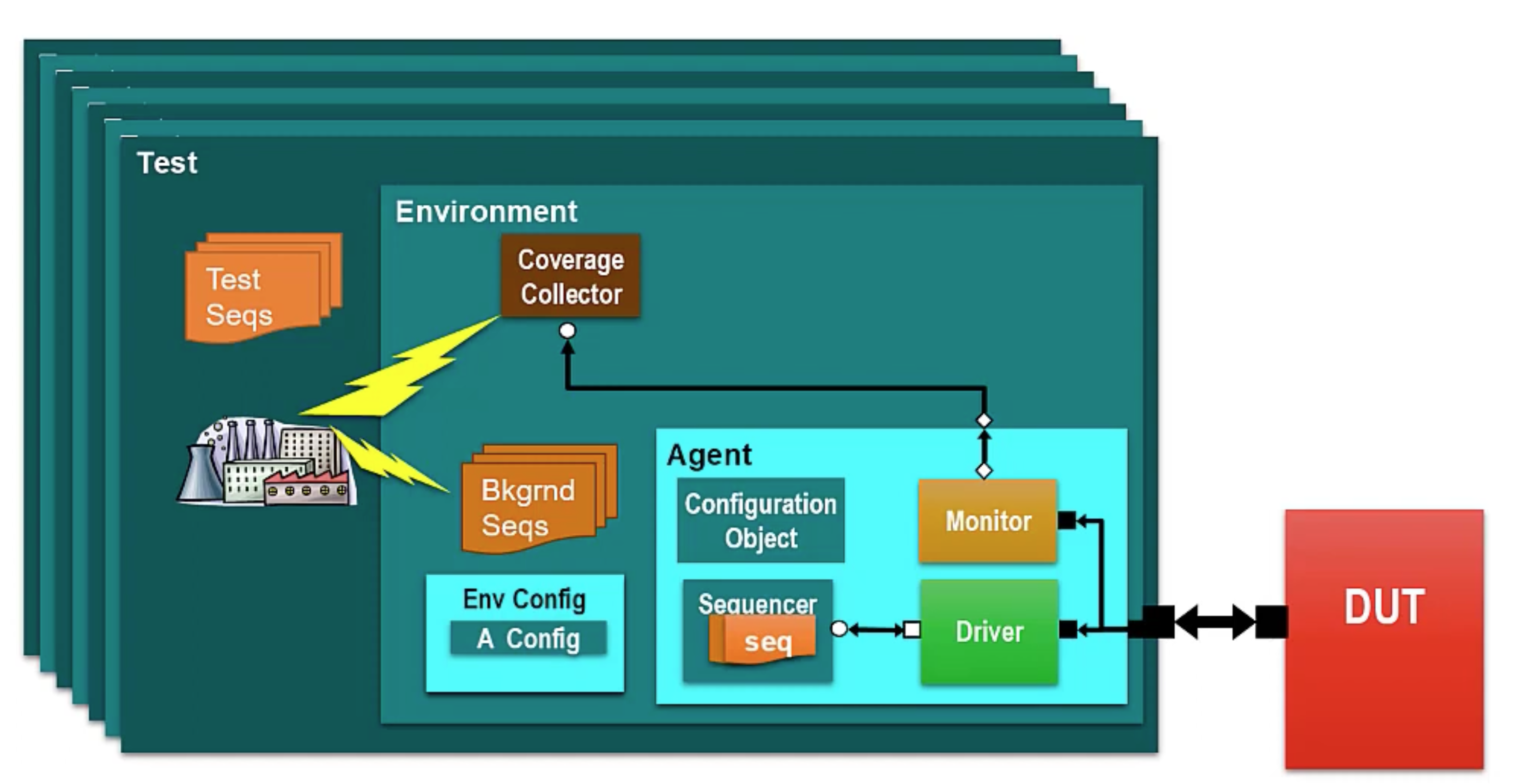

1. Agent (에이전트)의 내부 구조

Agent는 DUT(Aligner)의 특정 인터페이스(RX, TX, Register) 하나에 1:1로 전담 마크하여 붙는 단위입니다. 강의에서는 APB Agent (레지스터 제어용)를 시작으로 다음과 같은 내부 부품들을 조립한다고 설명합니다.

-

Interface : 소프트웨어인 UVM이 하드웨어인 DUT의 핀 신호에 접근하기 위한 다리 역할을 하는 표준 Verilog 인터페이스입니다.

-

Sequencer & Driver: 이 둘은 짝꿍입니다. 테스트 시나리오(Transaction)를 받아서 실제 APB 인터페이스의 핀 신호로 구동(Drive)합니다.

driver

class my_driver extends um_driver # (my_transaction);

'uvm_component_utils (my_driver)

virtual dut if dut vi;

function new (string name, uvm_component parent);

super. new (name, parent);

endfunction: new

function void build_phase (uvm_phase phase);

task run_phase (uvm_phase phase) ;

forever

begin

my_transaction tx;

@(posedge dut_vi.clock);

seq_item_port.get_next_item(tx);

dut_vi.cmd = tx.cmd;

dut_vi.addr = tx.addr;

dut_vi.data = tx.data;

@(posedge dut_vi.clock)

seq_item_port.item_done();

end

endtask: run_phase-

Monitor: 인터페이스에서 일어나는 모든 핀 신호의 변화를 조용히 지켜보다가, 이를 다시 SystemVerilog 클래스(트랜잭션)로 묶어서 환경 전체에 방송(Broadcast)합니다.

-

Coverage (에이전트 레벨 커버리지): 해당 인터페이스에서 '어떤 종류의 트랜잭션이 발생했는지' 기록하는 데이터베이스입니다. (예: "주소 0번에 쓰기 동작을 테스트했는가?")

-

Configuration: 이 에이전트의 세부 설정을 조작하는 컴포넌트입니다.

RX 및 TX Agent 개발 전략 (상속의 활용):

RX와 TX 인터페이스는 둘 다 'MD 프로토콜'이라는 동일한 규칙을 쓰기 때문에 코드가 겹칩니다. 따라서 공통 코드를 먼저 짠 뒤, 객체 지향 프로그래밍의 상속(Inheritance)을 활용해 각자 필요한 부분만 덧붙여 RX/TX Agent를 확장성 있게 개발한다고 합니다.

2. Model (레퍼런스 모델 / 예상 출력 생성기)

Model의 역할은 Agent(모니터)들이 수집한 입력 데이터를 바탕으로, "Aligner가 정상이라면 이런 출력이 나와야 해!"라고 정답지를 계산하는 것입니다.

-

Register Model: Aligner 내부의 4개 레지스터를 UVM 라이브러리를 활용해 소프트웨어적으로 똑같이 복제해 둡니다.

-

Predictor: UVM에서 기본 제공하는 기능으로, DUT의 레지스터 상태를 추적하고 업데이트/검증하는 역할을 합니다.

3. Scoreboard (스코어보드 / 채점자)

가장 핵심적인 검증 로직이 들어가는 곳입니다.

DUT가 실제로 내뱉은 결과물과, 위의 Model이 계산한 완벽한 정답지(Expected outputs)를 비교합니다.

두 값이 다르면 Error를 띄워 설계자에게 버그가 있음을 알립니다.

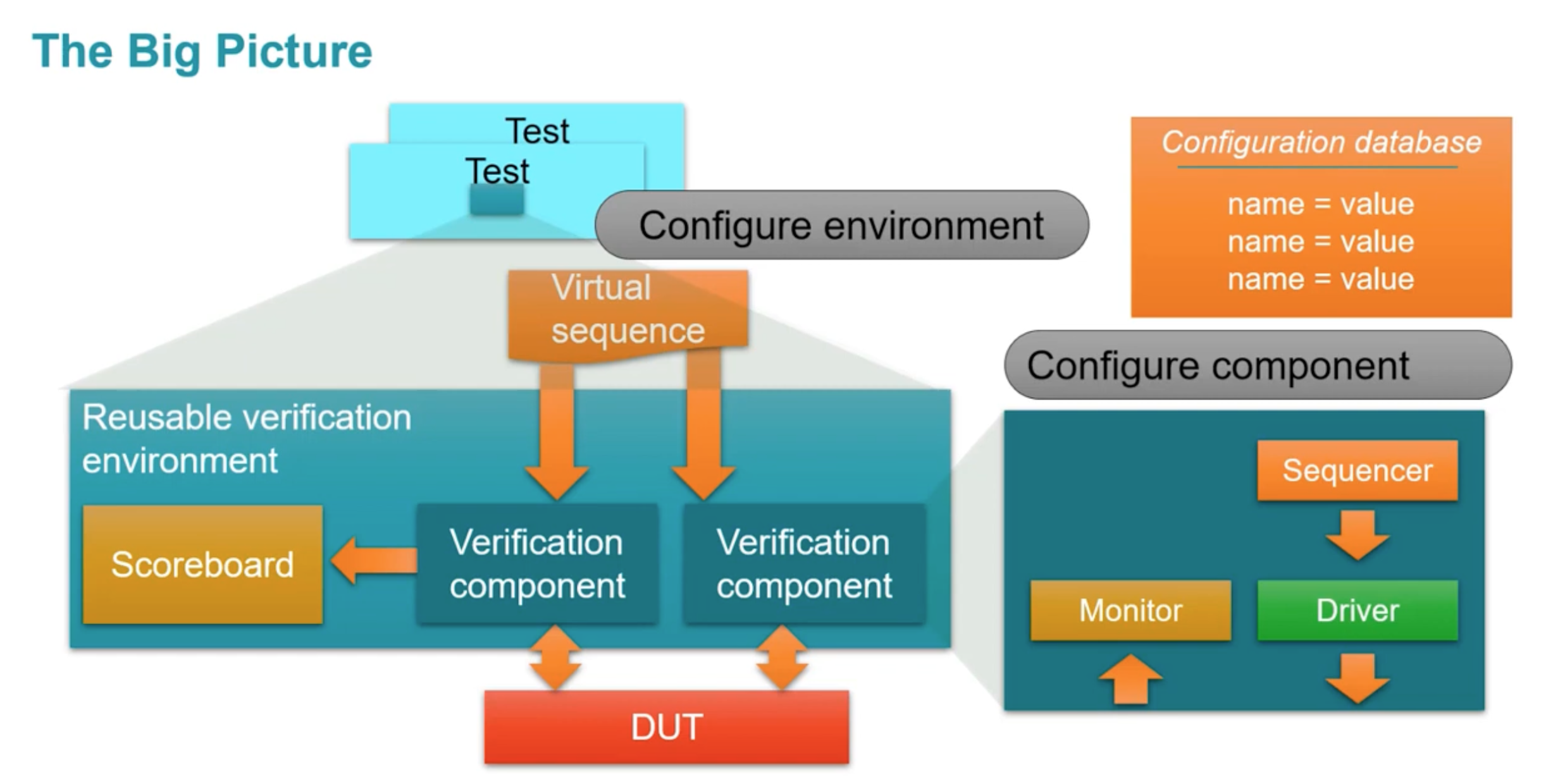

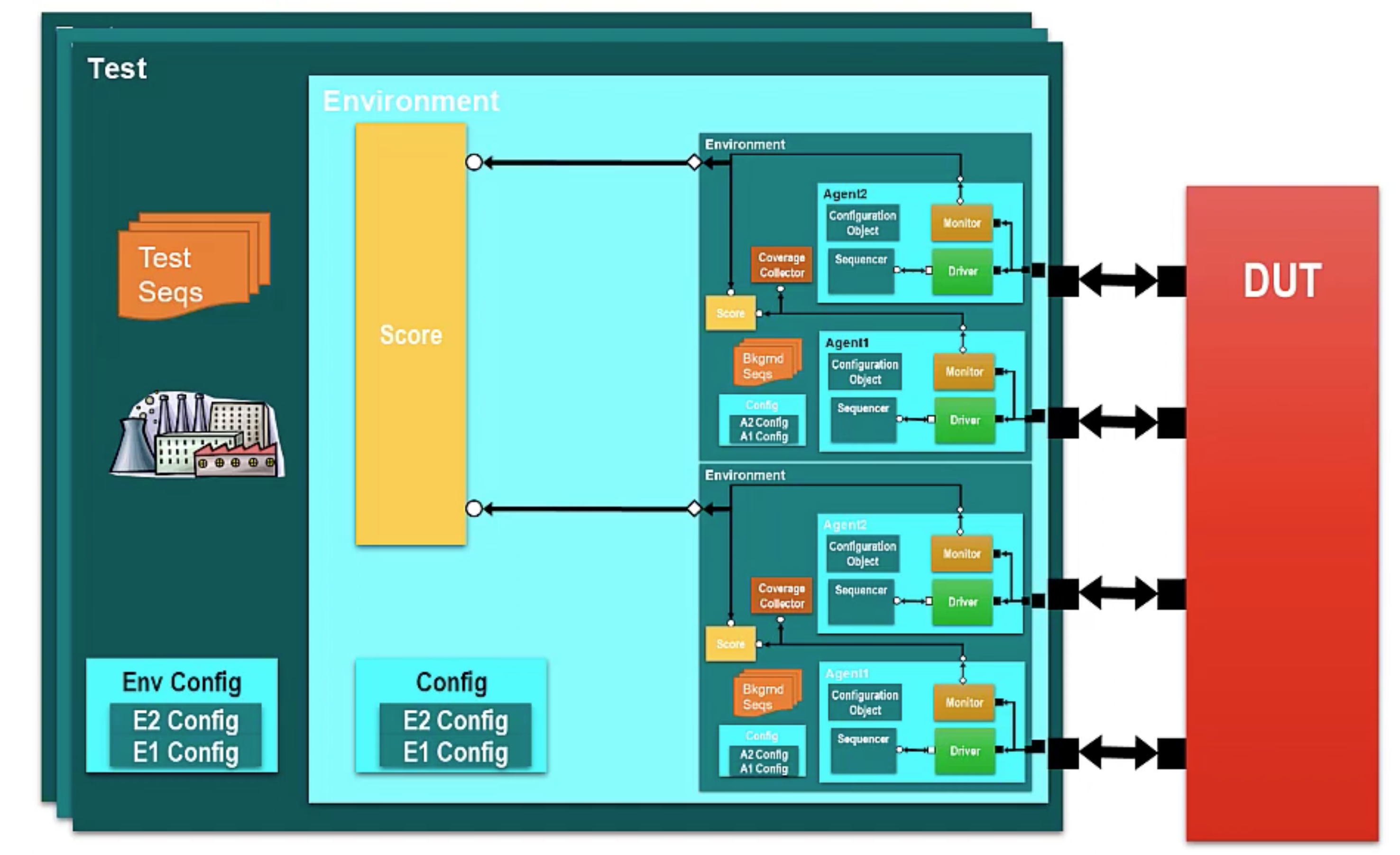

4. Environment-level (환경 전체 통합 컴포넌트)

개별 Agent들을 넘어, 전체 환경을 아우르는 부품들입니다.

-

Environment Coverage (환경 레벨 커버리지): Agent의 커버리지가 '단일 인터페이스'만 확인했다면, 여기서는 'Aligner 전체 기능이 여러 조합으로 잘 테스트되었는지' 숲을 보는 큰 그림의 데이터베이스를 구축합니다.

-

Virtual Sequencer (가상 시퀀서): 여러 Agent들(APB, RX, TX)을 지휘자처럼 한 번에 통제하고 순서를 맞출 수 있게 해주는 최상위 컨트롤러입니다.

-

Environment Configuration: 환경 전체의 파라미터를 조율합니다

5. Test & Testbench (최상위 계층)

지금까지 만든 모든 SystemVerilog 클래스(소프트웨어)들을 실제 Verilog 모듈(하드웨어) 위에 올리는 작업입니다.

-

Base Test (클래스): 위에서 만든 전체 Environment를 하나로 찍어내는(Instantiate) 틀입니다. 이를 상속받아 수많은 엣지 케이스 테스트들을 찍어냅니다.

-

Testbench (Verilog 모듈): 가장 꼭대기에 있는 껍데기입니다. 물리적인 하드웨어인 DUT를 생성하고, UVM 시뮬레이션 시스템을 "시작(Start)" 시키는 방아쇠 역할을 합니다.

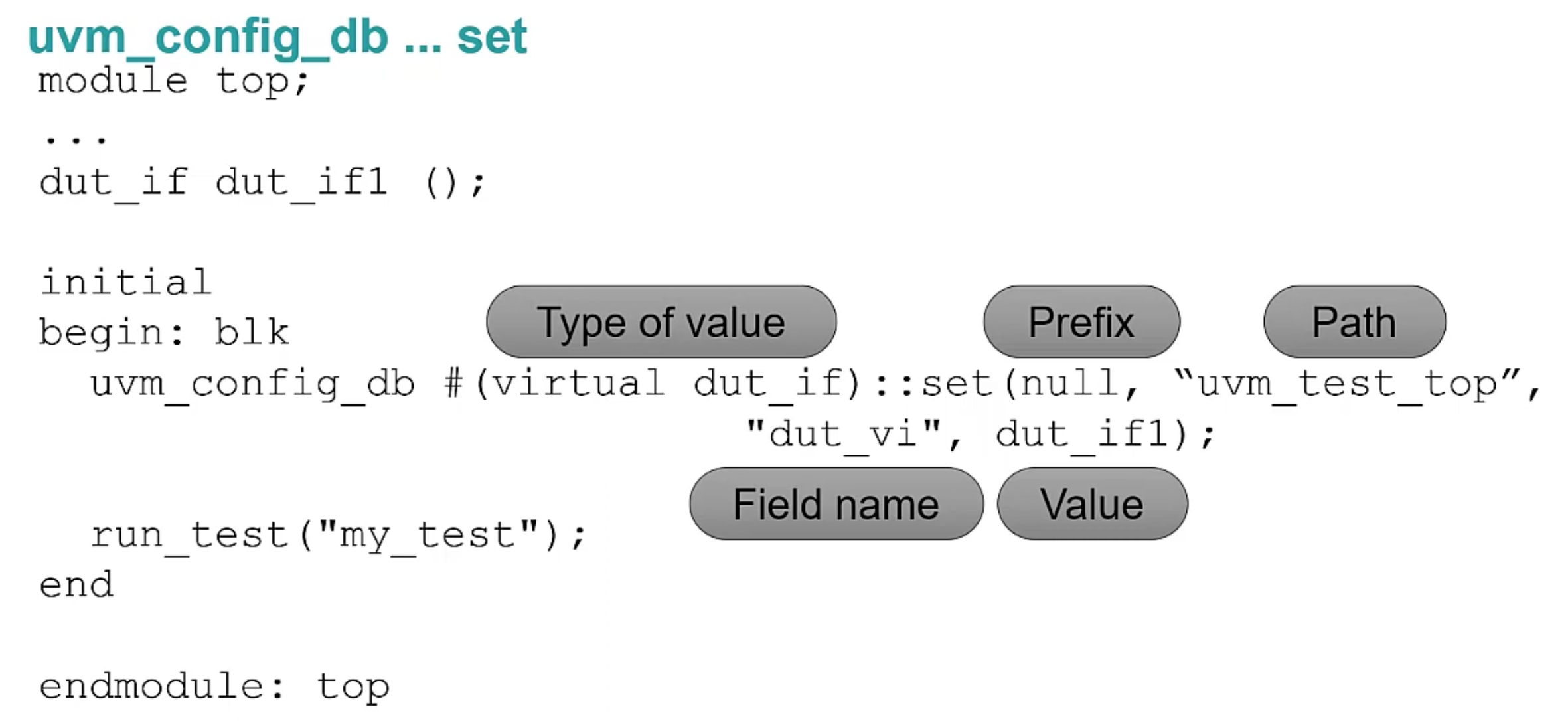

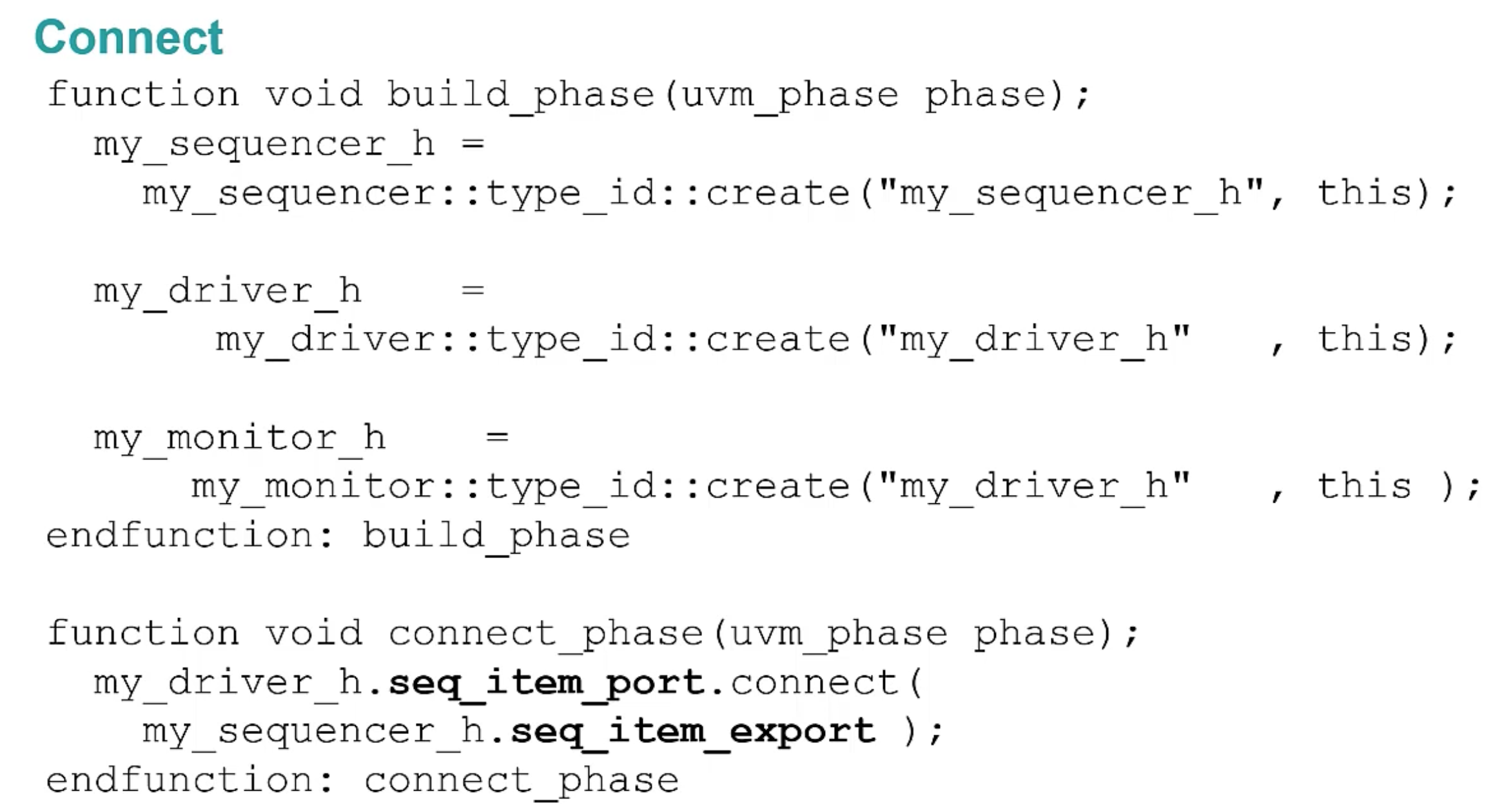

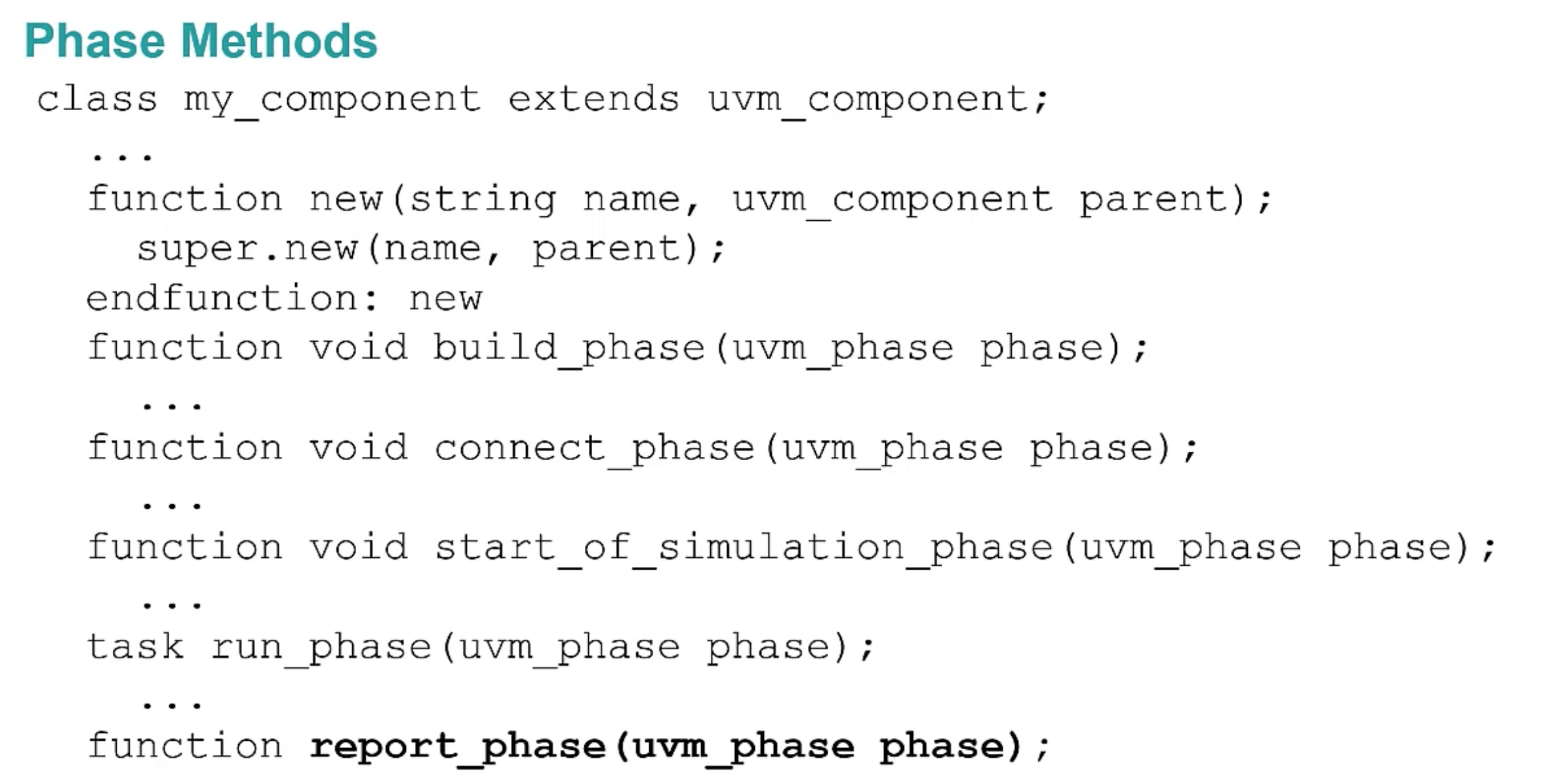

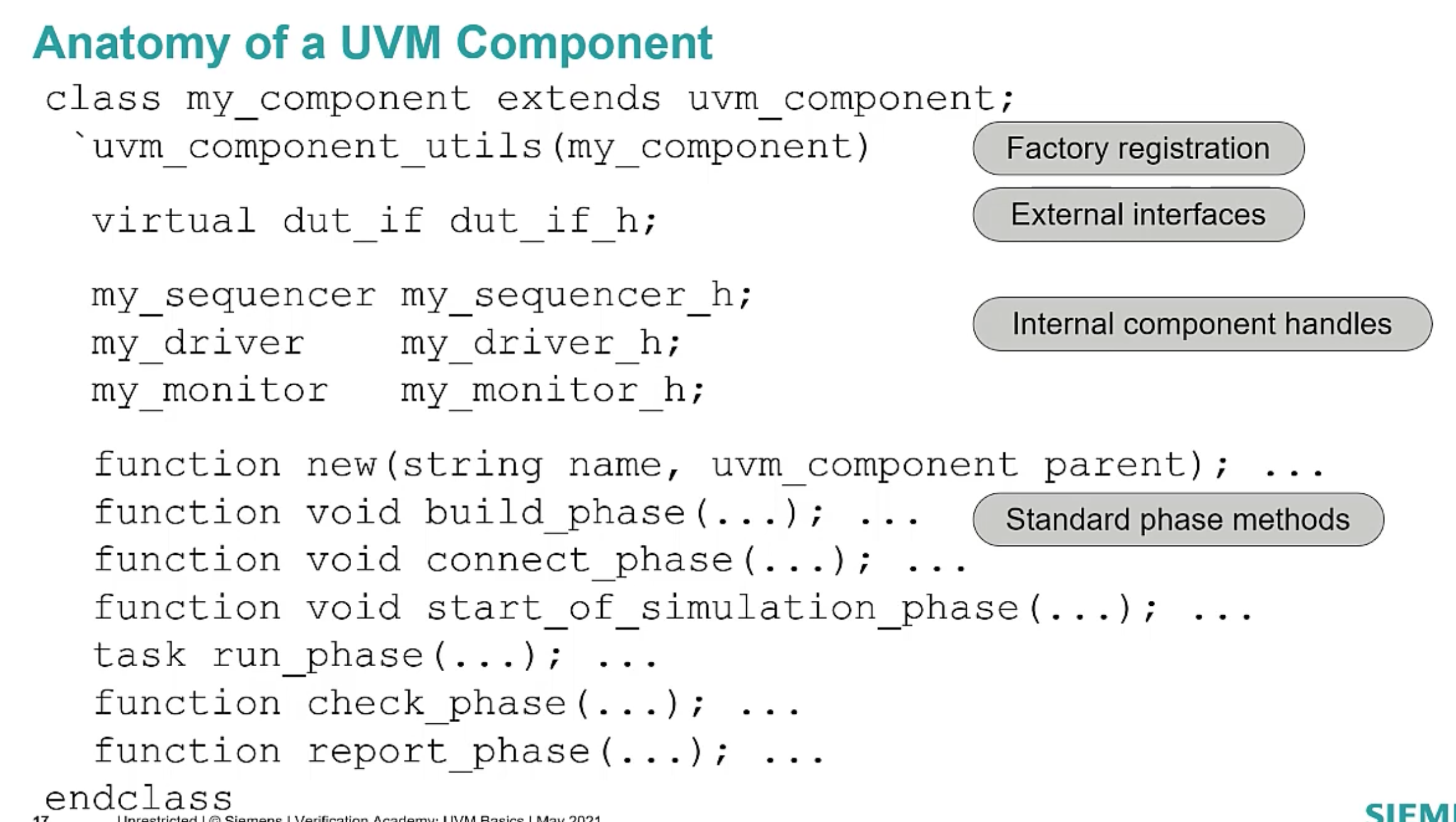

6. Connecting Components

phase Methods

보통 UVM 파일 구조

7. Transaction

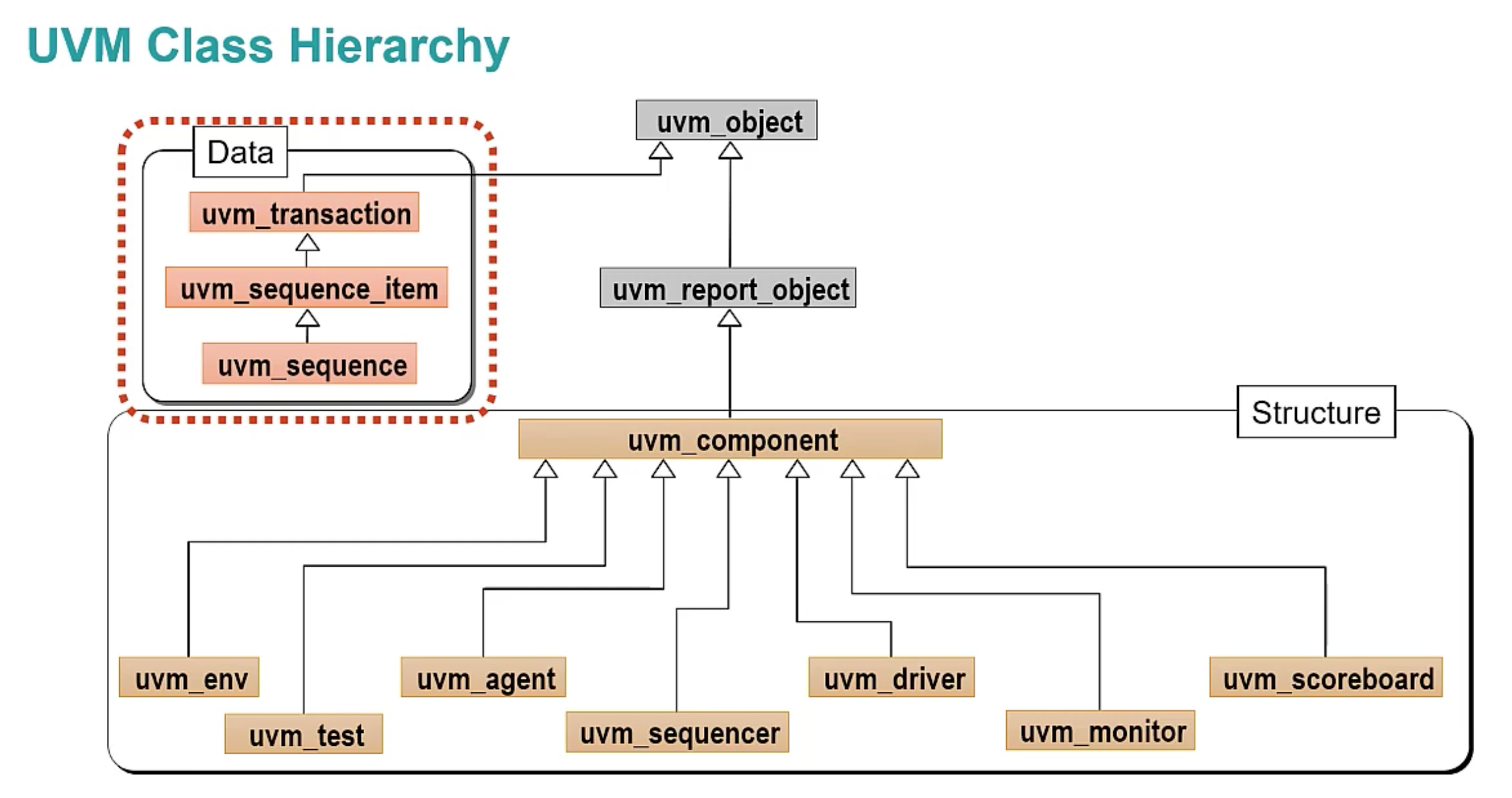

Data는 UVM component가 아니라 쓰고 없어지는 대본, 데이터 같은 것이다.

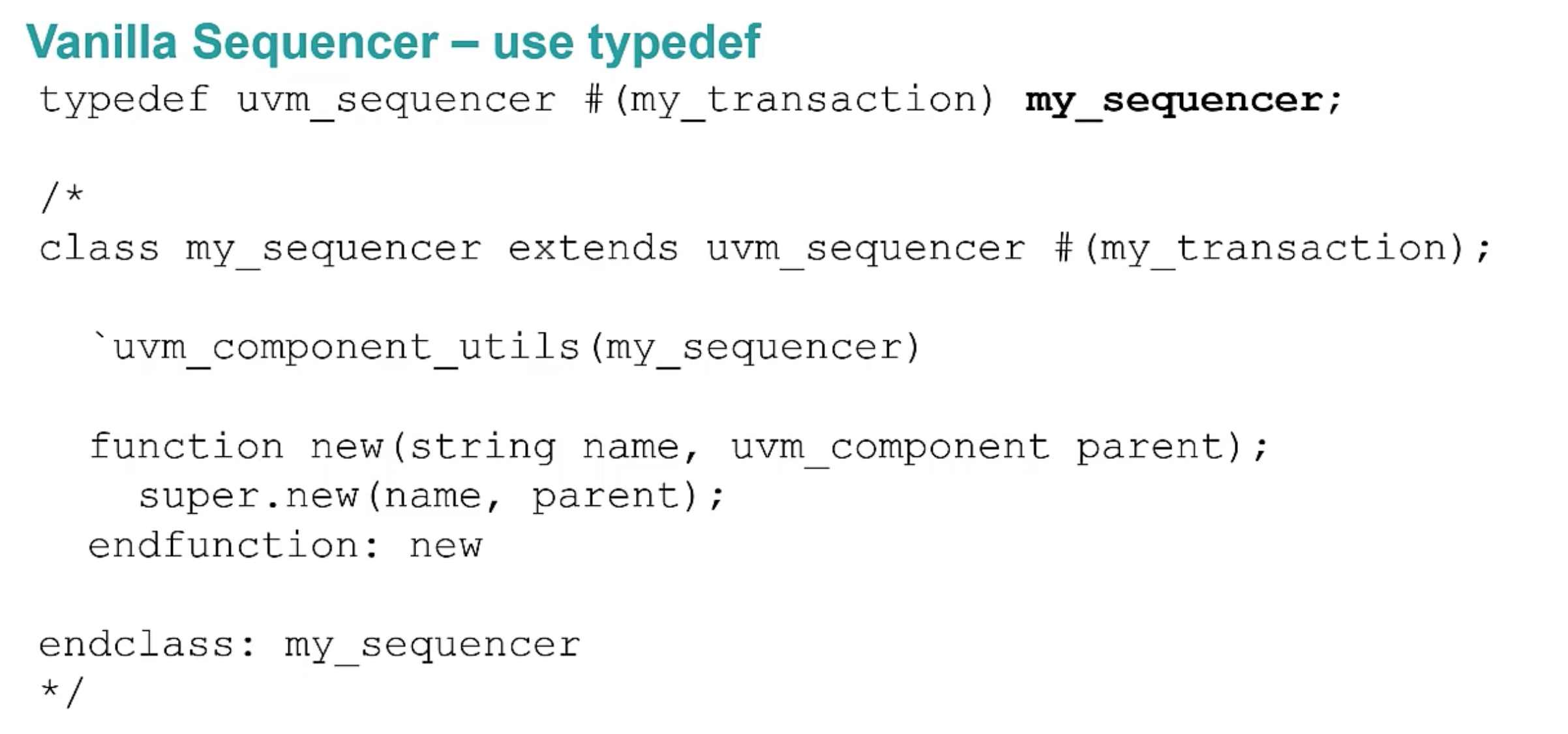

Sequencer (component)

Sequence (data)

class my_sequence extends uvm_sequence # (my_transaction);

uvm_object_utils (my_sequence)

function new (string name);

super. new (name);

endfunction: new

task body; //The behavior of the sequence

forever

begin

my_transaction tx;

//"Factory method" can be overridden in tests

tx = my_transaction::type_id::create("tx");

start_item(tx); //handshake

assert(tx.randomize()):

finish_item(tx);

end

endtask: body