UVM

1.UVM System verilog 문법

개념: 공장에서 택배 상자가 막 찍혀 나와서 메모리에 처음 생겨날 때(태어날 때), 무조건 가장 먼저 자동으로 실행되는 초기화 함수입니다. OOP에서는 이를 '생성자(Constructor)'라고 부릅니다.function new(string name = "adder_it

2.UVM Introduction

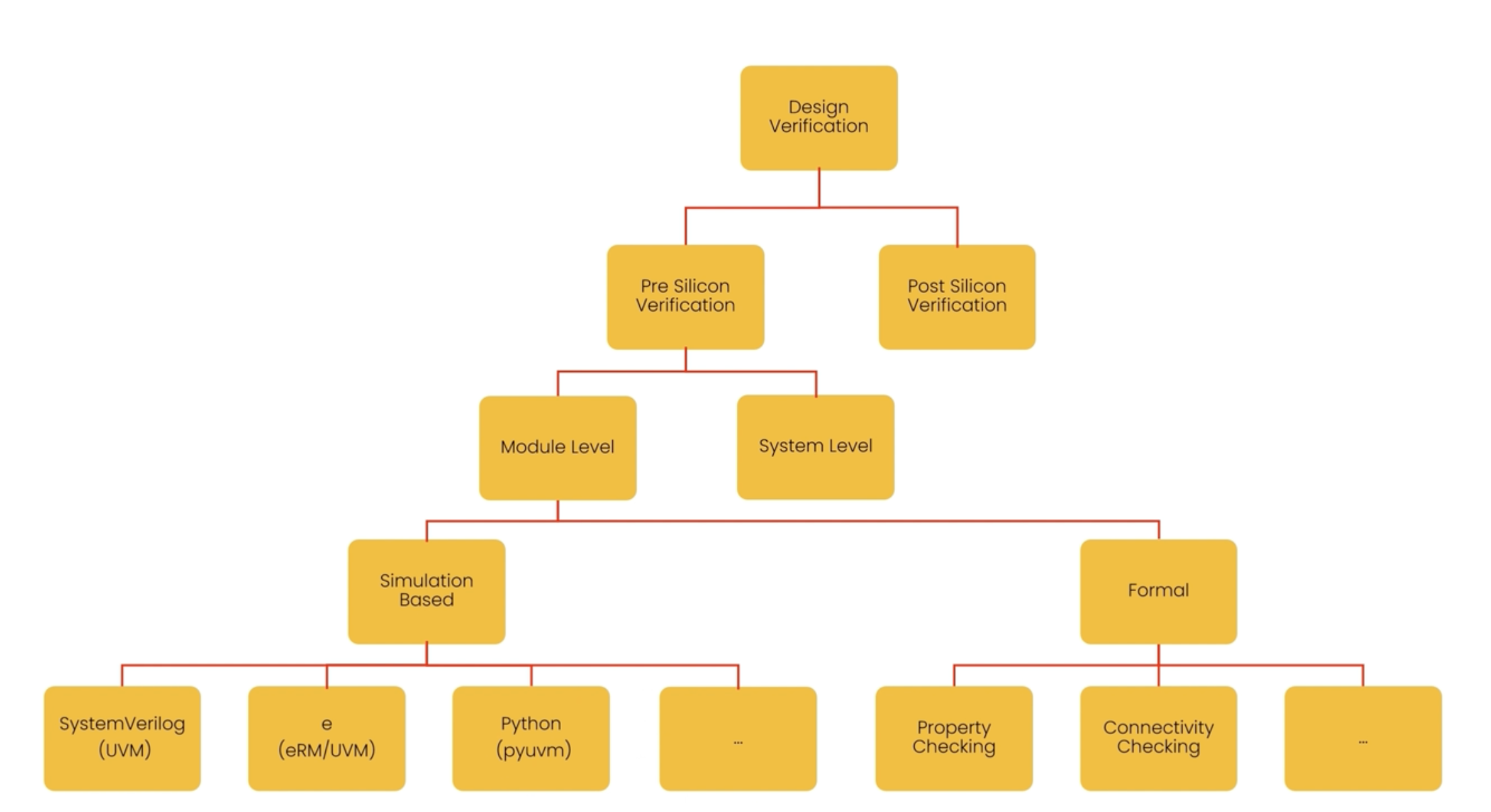

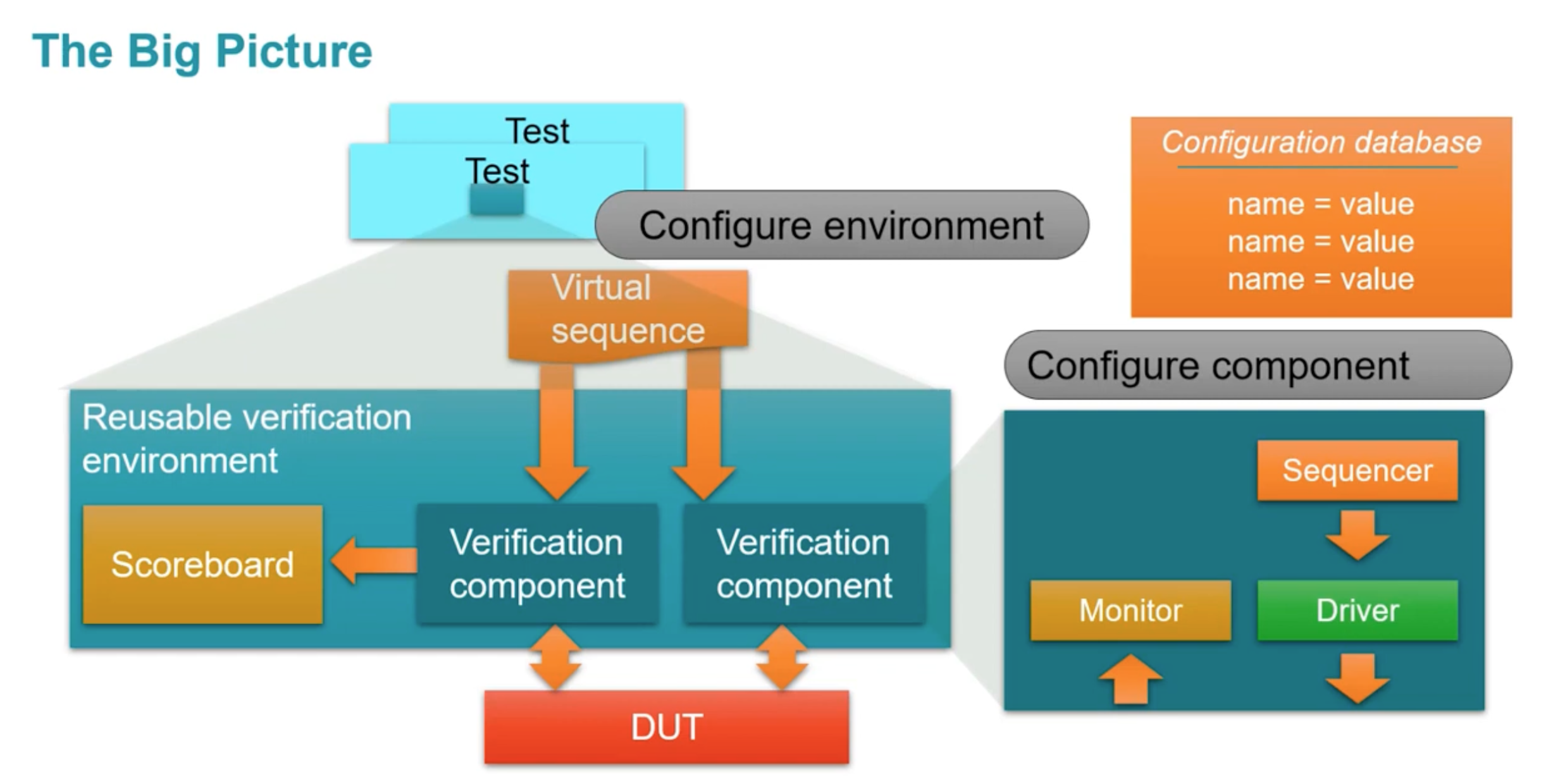

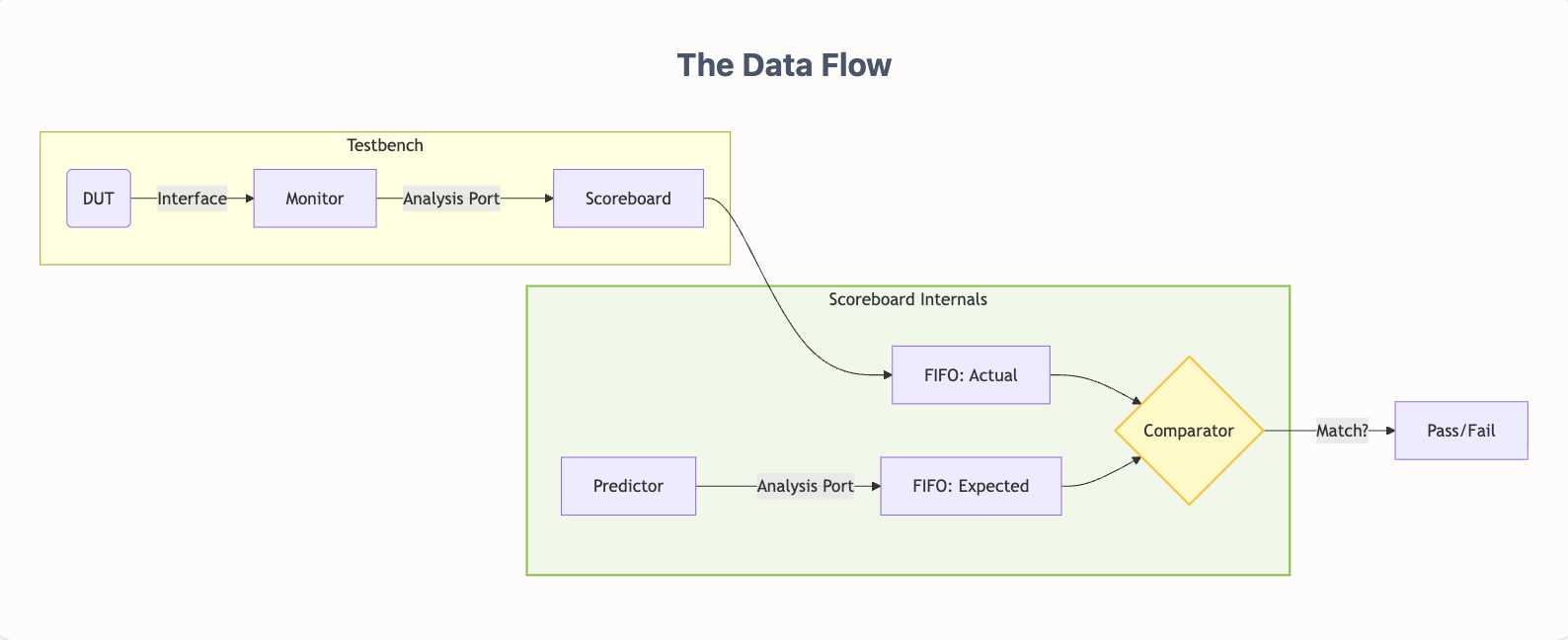

What is Design Verification하나는 Agent->DUT->Agent를 통과하고, (TEST)다른 하나는 Agent -> Model을 통과한다 (정답지)위 두 결과를 Scoreboard에서 같은지 다른지 확인한다Alignment데이터가 받고, 전송될

3.UVM Architecture

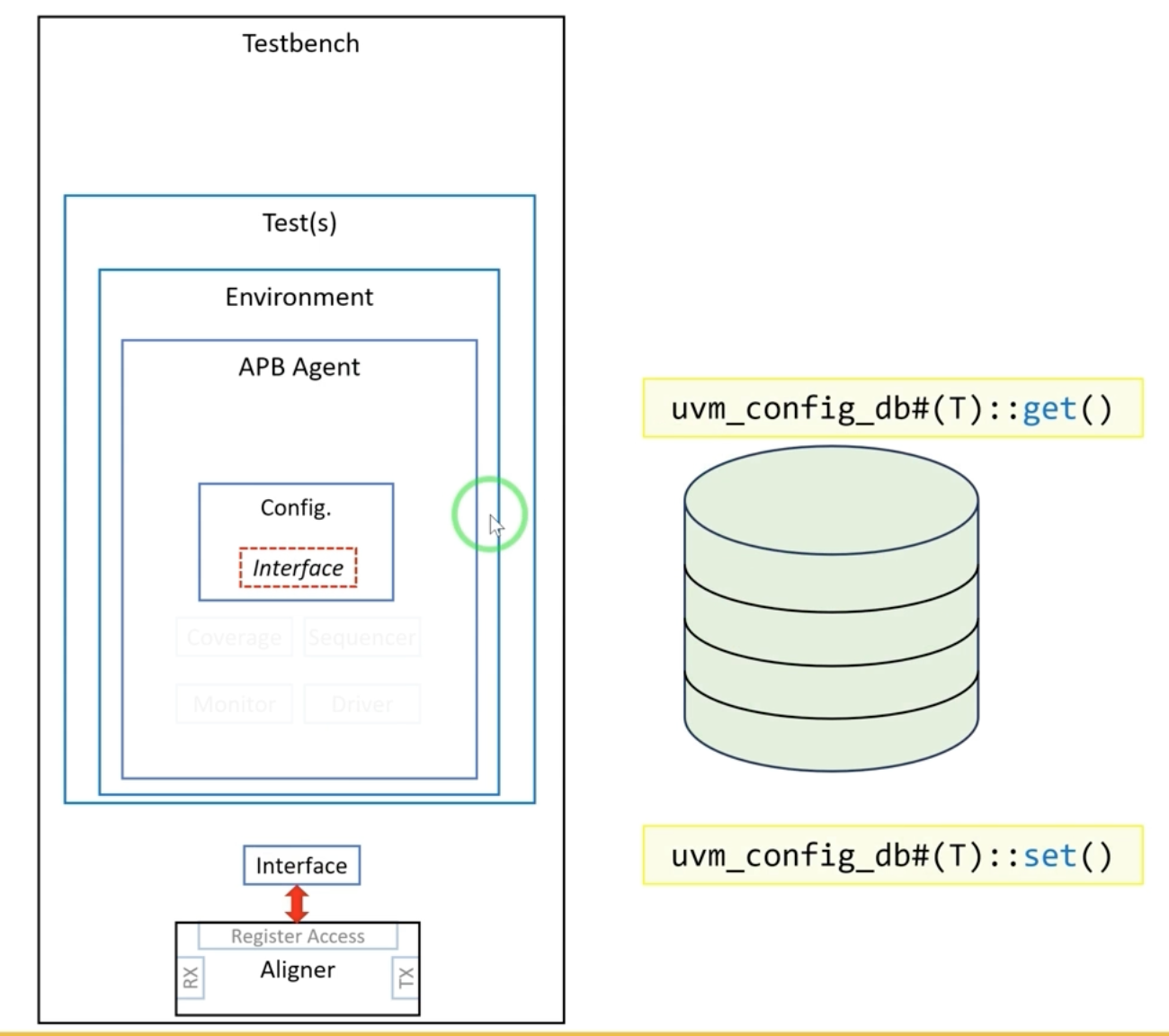

Agent는 DUT(Aligner)의 특정 인터페이스(RX, TX, Register) 하나에 1:1로 전담 마크하여 붙는 단위입니다. 강의에서는 APB Agent (레지스터 제어용)를 시작으로 다음과 같은 내부 부품들을 조립한다고 설명합니다.Interface : 소프트

4.Adder UVM Practice

대본 작성 adder_seq : "오늘은 A=5, B=10을 담은 택배 상자(adder_item)를 만들어야지!" 하고 무작위로 상자를 찍어내서 아래로 던집니다.하드웨어 구동adder_driver: 위에서 떨어진 택배 상자를 열어보니 A=5, B=10이 들어있습니

5.APB Agent / uvm_config_db

문제점: Agent는 메모리에 동적으로 생성되었다 지워지는 소프트웨어 객체(class)입니다. 반면, DUT의 핀과 연결되는 Interface는 시뮬레이션 시작부터 끝까지 고정된 물리적 하드웨어(module 내부에 선언됨)입니다. 따라서 class 안에서 interfa

6.UVM 1

UVM은 부품을 조립해서 거대한 기계를 만드는 과정입니다. 가장 작은 단위부터 최상위까지 3단계로 나뉩니다.Agent (에이전트): 특정 인터페이스(예: AXI4-Lite) 하나를 전담하는 통신 부서입니다.구성 요소: Sequencer (대본 전달), Driver (핀

7.UVM 2: Factory와 Configuration

객체 지향 프로그래밍(OOP)에서 객체를 만들 때 보통 new()라는 생성자(Constructor)를 씁니다. 하지만 UVM에서는 절대 new()를 쓰지 않고 create()를 씁니다. 그 이유가 바로 Factory 때문입니다.Factory의 존재 이유 (Why Fac

8.UVM basic template

seq_item_port.get_next_item(req): This is a blocking call. The driver sleeps here until a sequence provides a new transaction.seq_item_port.item_done(

9.TLM

TLM (Transaction Level Modeling) is how UVM components talk to each other. Instead of connecting wires, they call functions.Port: The "Requester". It

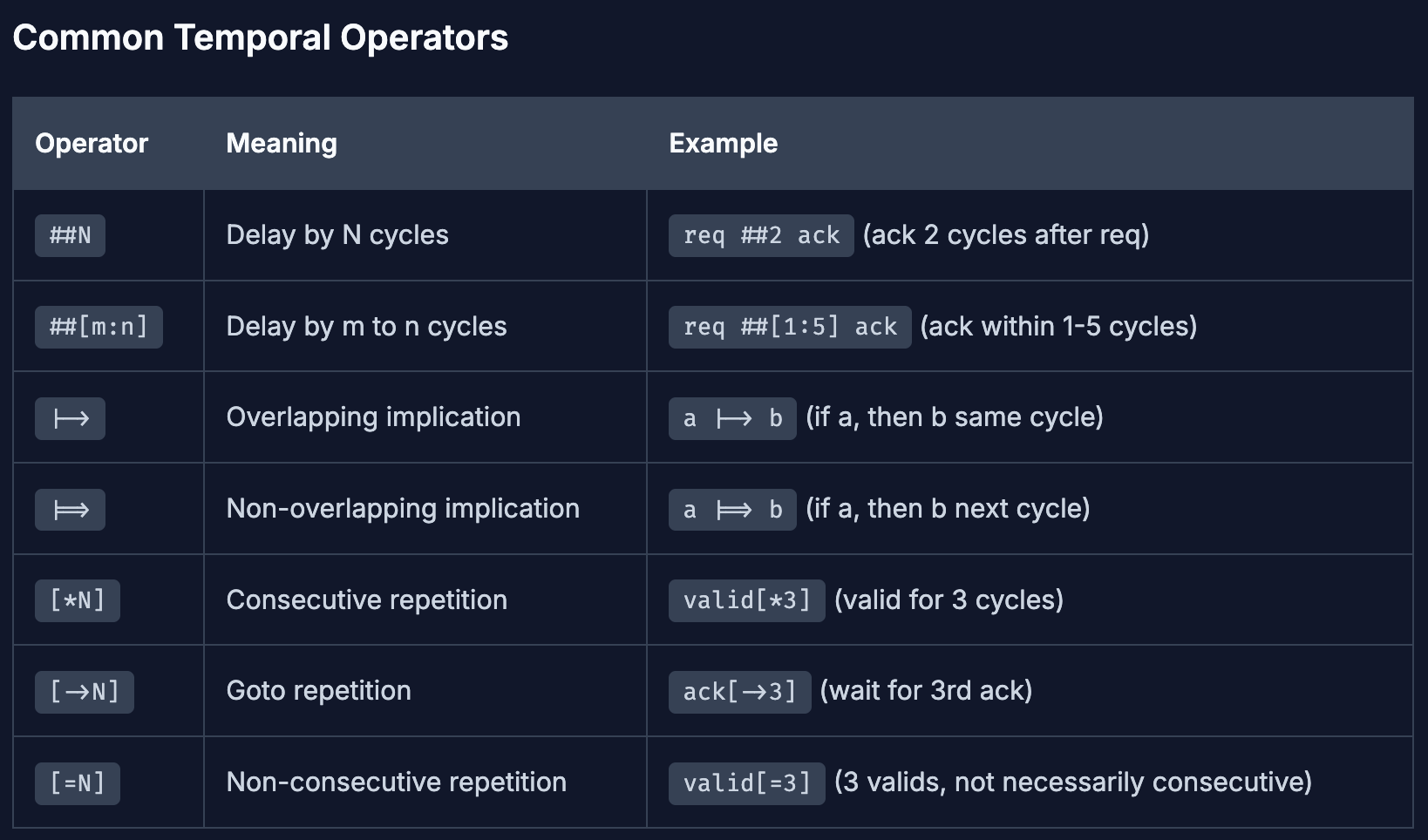

10.SVA

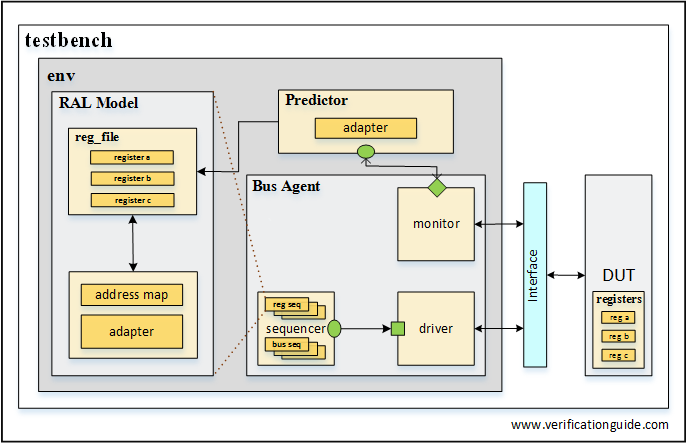

11.RAL

RAL(Register Abstraction Layer)RAL 없이는 요즘 나오는 수십억 게이트짜리 SoC(System on Chip)를 절대 검증할 수 없습니다.RAL이 없을 때 (과거의 노가다):엔지니어가 1000페이지짜리 스펙 문서를 뒤져가며 "아, UART 모듈

12.Virtual Sequence, Sequencer

단일 Sequencer는 바이올린 연주자 한 명과 같습니다. 자기 악기(AXI 트랜잭션)만 연주할 줄 압니다.하지만 실제 칩에는 AXI 버스, APB 버스, I2C 통신, Interrupt 신호 등 수십 개의 에이전트(Agent)가 동시에 돌아갑니다.중앙 통제 (Cen