연산증폭기

(Operation Amplifier)

- 직류 / 교류 신호에서 증폭기(Amplifier)의 역할을 하며, 버퍼, 전류-전압 변환기, 적분기, 미분기, 정류기, 아날로그 필터 발진기 등 다양한 선형(Linear) 또는 비선형(Non-linear) 회로에 사용되는 능동 소자를 의미합니다.

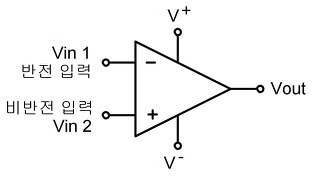

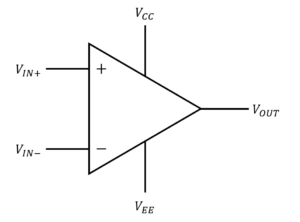

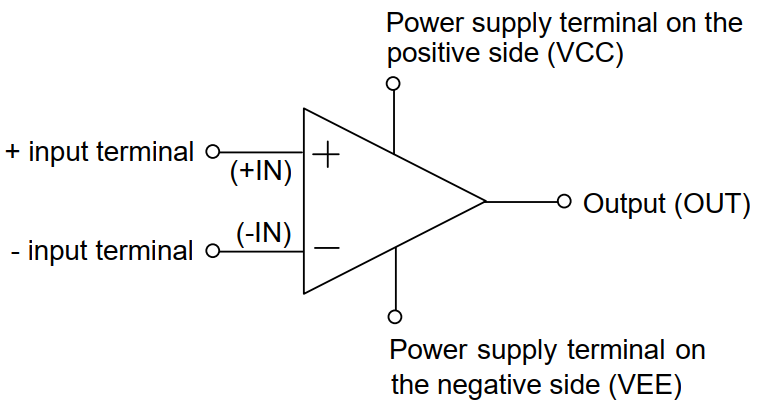

연산 증폭기의 입력 / 출력 단자

-

1) 반전(Inverting) 입력 단자

입력 신호와 출력 신호가 서로 반전되는 위상(Phase) -

2) 비반전(Noninverting) 입력 단자

입력 신호와 출력 신호가 서로 동일한 위상(Phase) -

3) 출력 단자

출력 신호가 나오게 되는 단자.

Vout = A⋅(V+−V−) -

4) 전원 단자

(+) 전원과 (-) 전원이 인가되는 단자

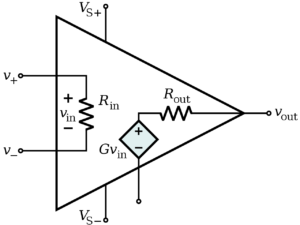

이상적인 OPAMP

-

Rin = ∞

Rout = 0Ω -

Rin으로 큰 전압을 가져오기 위해 Ideal opamp에서 Rin = ∞

Ideal opamp에서 이론상 입력단의 전류는 0이다. -

Vout에 전압을 온전히 보내기 위해 Ideal opamp에서 Rout = 0Ω 이다.

-

입력임피던스 Zin = ∞ ,

출력임피던스 Zout = 0,

전압이득 Av = ∞

오차 X, 내압 무한대

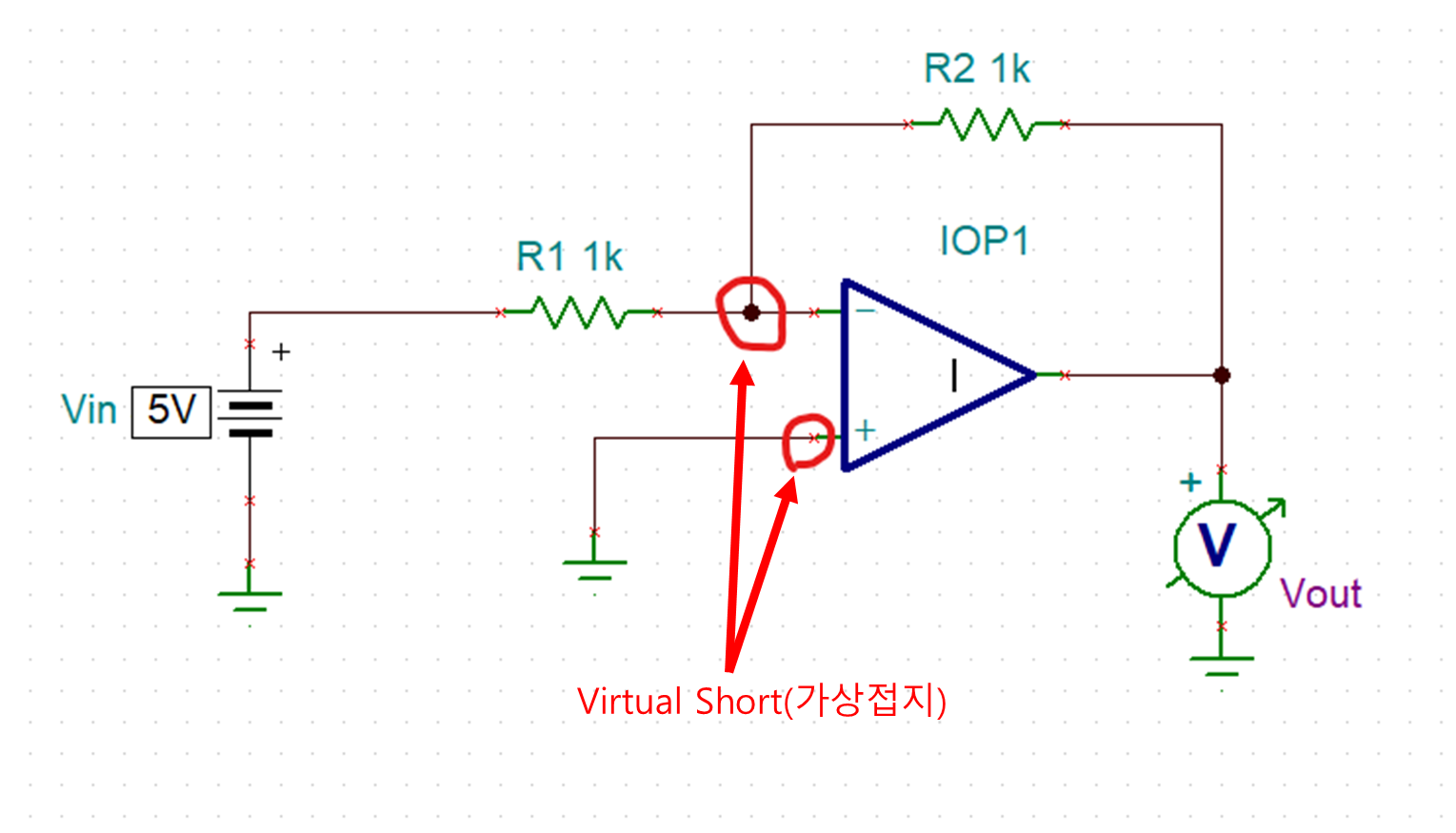

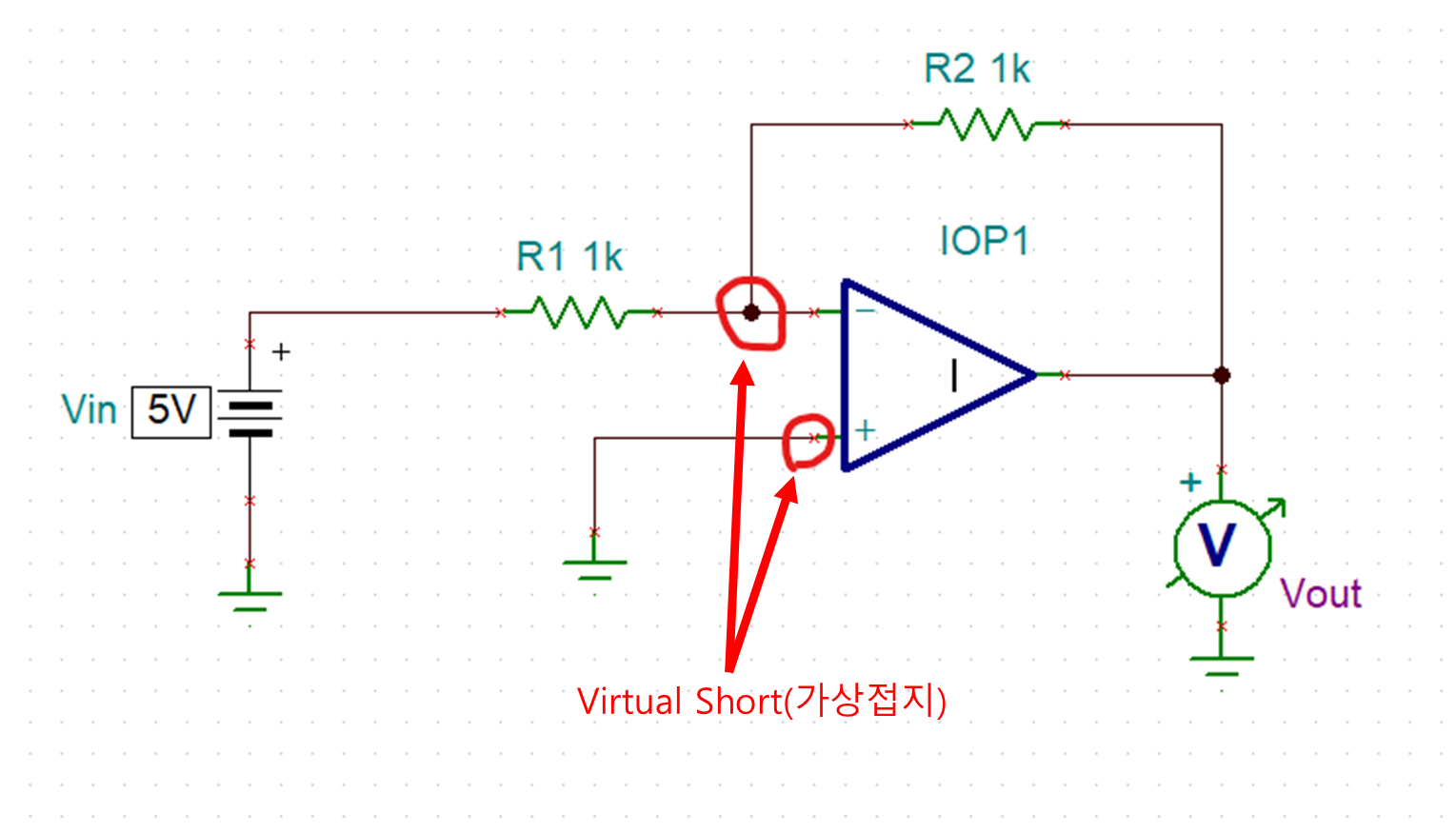

가상단락 :

- 두 입력단자 사이의 전압이 0에 가깝지만 입력 임피던스는 무한대에 가까워

전류 0, 전압이득 무한대

OP AMP에 음의 피드백이 존재할 경우, 두 입력 단자(+)와 (−)는 전압이 거의 같아진다.

하지만 실제로 물리적으로 연결된 것이 아니기 때문에 "가상" 단락이라 부른다.

가상접지 :

-

실제로 접지와 연결되지 않았지만, 전압이 0V인 점처럼 동작하는 노드를 의미

반전 증폭기 회로에서, OP AMP의 음의 피드백으로 인해 반전 입력단(−)의 전압이 실제 접지처럼 0V가 되지만, 실제로 GND에 연결된 것은 아닌 상태를 말함. -

전압 : 0V (접지처럼 보임)

전류 : 흐르지 않음 (입력 임피던스 무한대)

작동원리

비반전 입력이 GND에 연결되어 V+ = 0V

피드백이 존재하므로 V- = V+ = 0V → 접지된 것처럼 보임

하지만 실제 접지와는 연결 X → "가상" 접지

| 항목 | 가상 단락 (Virtual Short) | 가상 접지 (Virtual Ground) |

|---|---|---|

| 정의 | ||

| 위치 | OP AMP 두 입력 단자 사이 | OP AMP 반전 입력 단자 (특정 구성에서) |

| 전류 | 흐르지 않음 | 흐르지 않음 |

| 전압 | 거의 동일 | 거의 0V (접지처럼 보임) |

| 조건 | 음의 피드백 존재, 포화 X | 비반전 입력이 GND일 때 |

| 사용 회로 | 비반전, 반전, 차동 증폭기 등 | 반전 증폭기, 서밍 증폭기 등 |

증폭기 종류

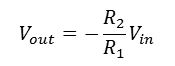

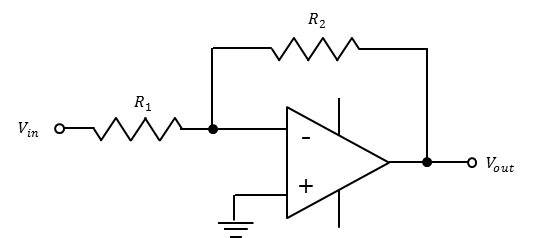

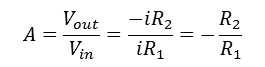

반전 증폭기

(Inverting Amplifier)

- 입력 단자는 GND에 연결되어 있기 때문에 - 입력 단자는 가상 접지로 간주

Vin=IR1, Vout=-IR2

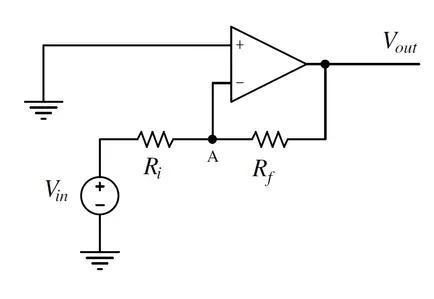

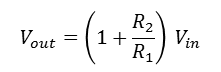

비반전 증폭기

(Non-inverting Amplifier)

In (i-) = 0

점 찍힌 부분의 전압 Vin -> Vin / R1 = (Vout - Vin) / R2

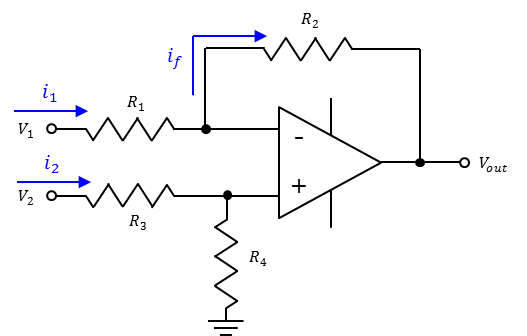

차동 증폭기

(Differential Amplifier)

- 두 입력전압의 차이에 해당하는 전압을 증폭하는 회로

✅ 특징:

반전(-) 입력과 비반전(+) 입력이 모두 신호 입력으로 사용됨.

입력으로 들어오는 두 신호(V+와 V-)의 차이를 증폭.

출력이 다른 신호처리 회로로 전달됨.

센서 신호 증폭, 노이즈 제거, 신호 비교 등에 사용.

✅ 구별 방법:

OPAMP의 두 개의 입력 단자(+,-)가 모두 신호를 받으면 차동 증폭기.

출력이 직접적인 전압 제어 루프에 연결되지 않음.

전원 제어 회로에서 사용되지 않음 (센서 신호 증폭, 신호 처리에 사용됨).

수식

Vout = A(V+ - V-)

A : gain, V+ : +입력전압, V- : -입력전압

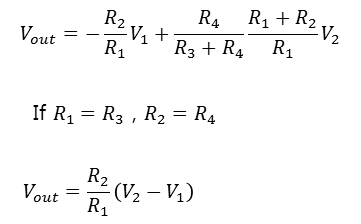

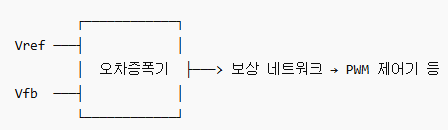

오차 증폭기

(Error Amplifier)

-

'+' 입력 : 기준 전압(Vref)

'+' 입력 : 기준 전압(Vref)

'–' 입력 : 피드백 전압(Vfb)

출력 : Vout = A × (Vref – Vfb) -

Vfb < Vref → 출력 증가 → 출력 전압 상승 유도

Vfb > Vref → 출력 감소 → 출력 전압 하강 유도

Vfb = Vref → 출력 안정 상태 (루프 정상)

오차증폭기(Error Amplifier) 는 목표값(Reference)과 실제 측정값(Feedback) 간의 차이(오차) 를 증폭하여 제어 신호로 전환하는 회로.

오차 증폭기의 역할은 입력 신호의 차이( VERR = VREF − VFB )를 증폭하여 출력 신호로 제공하고, 피드백 루프를 통해 시스템의 출력이 목표값(VREF)에 도달하도록 제어하는 것

(-) 단자 전압이 클 때: 출력 전압을 감소시켜 피드백 전압을 낮춥니다.

(+) 단자 전압이 클 때: 출력 전압을 증가시켜 피드백 전압을 높입니다.

입력 신호 비교

-

오차 증폭기는 두 입력 신호를 비교하여 차이를 계산.

하나의 입력은 기준 전압(Reference Voltage),

다른 하나는 출력에서 피드백된 전압(Feedback Voltage).

두 신호 간의 차이를 오차(Error) -

계산된 오차를 증폭하여 출력 신호로 제공합니다.

증폭된 오차 신호는 시스템의 제어 루프에서 사용되어 출력 상태를 조정합니다.

제어 신호 생성

-

증폭된 오차 신호는 주로 PWM(Pulse Width Modulation) 컨트롤러, 스위칭 소자, 또는 다른 제어 장치로 전달되어 출력 상태를 안정화하는 데 사용

-

OPAMP의 한쪽 입력이 기준 전압

다른 입력이 출력에서 피드백 신호를 받으면 오차 증폭기.

출력이 전압 조절 루프에 연결되어 출력 전압을 조절하는 역할.

차동 증폭기와 오차 증폭기

🔹 차동 증폭기 = 두 입력의 차이를 증폭하는 일반적인 증폭기.

🔹 오차 증폭기 = 전압 피드백을 받아 전원 공급을 조절하는 증폭기.

🔹 기준 전압과 피드백 입력을 비교하고 출력이 전압 조절 역할을 하면 오차 증폭기.

🔹 출력이 피드백 없이 증폭 신호로만 사용되면 차동 증폭기.

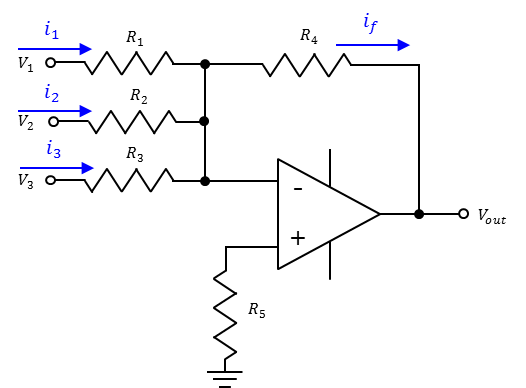

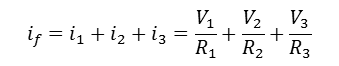

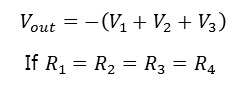

반전 가산기

(Inverting Summing Amplifier)

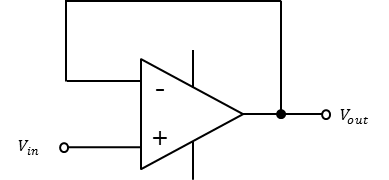

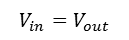

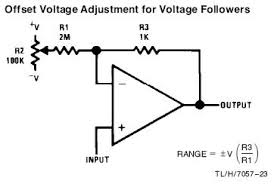

전압 팔로워 (버퍼)

(Voltage Followers)

전압 팔로워는 OPAMP 회로에서 출력을 입력에 직접 피드백하는 회로

회로 구성:

- 비반전 입력: OPAMP의 비반전 입력(+)에 신호를 입력하고, 출력을 비반전 입력(+)에 직접 연결합니다. 이때, 반전 입력(-)은 연결되지 않으며, 이 회로는 입력 전압과 출력 전압이 동일하게 됩니다.

버퍼라고 부르기도 함, 전압이득이 1인 증폭기로 입력전압 = 출력전압

높은 입력 임피던스와 낮은 출력 임피던스를 가져 부하사이의 완충단으로 사용 (신호 전달 시 손실을 최소화)

버퍼를 사용하면 버퍼 이전의 모든 회로의 임피던스를 무시할 수 있음

ex) 먼거리에서 입력 출력에 온전히 전달

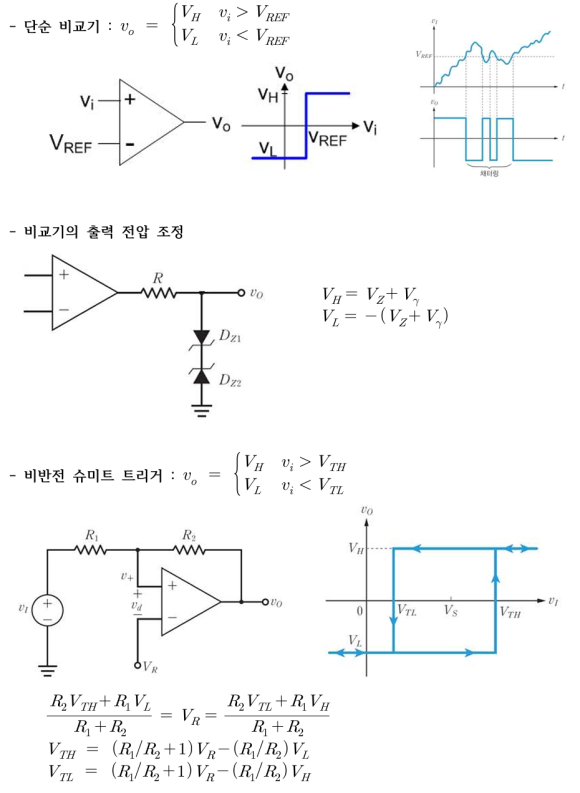

비교기

Feedback 없는 연산증폭기 회로

Vin단자에 따라 Vout값 변동 (VCC or VEE)

Vin+ > Vin- 면 VCC출력

Vin+ < Vin- 면 VEE출력

연산증폭기의 출력은 연산증폭기의 Power supply 전압을 초과할 수 없음.

-

V+가 V-보다 조금이라도 더 크다면 V+−V-는 무한대배만큼 증폭, 출력값은 +Bias Voltage Vcc로 Saturation

-

V-가−V+보다 크다면 출력값은 -Bias Voltage VEE로 Saturation

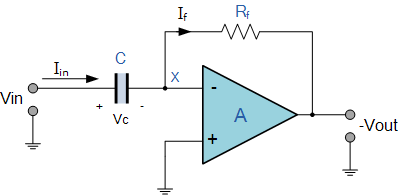

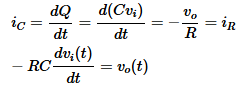

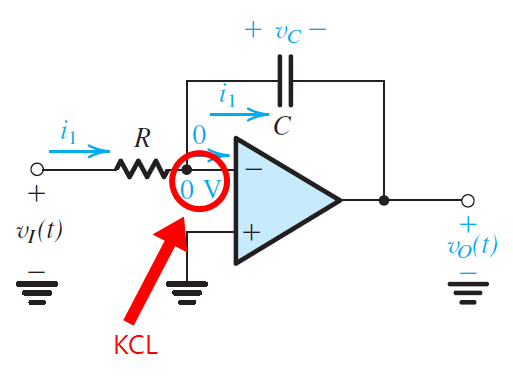

미분기와 적분기

미분기

적분기

- 적분기 -1/sCR

미분기 -sCR

적분기에서 고주파일수록 이득 감소, 미분기에서 저주파일수록 이득 감소

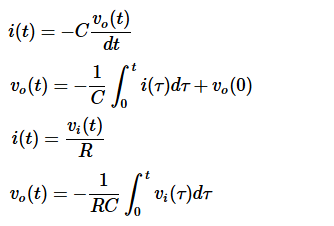

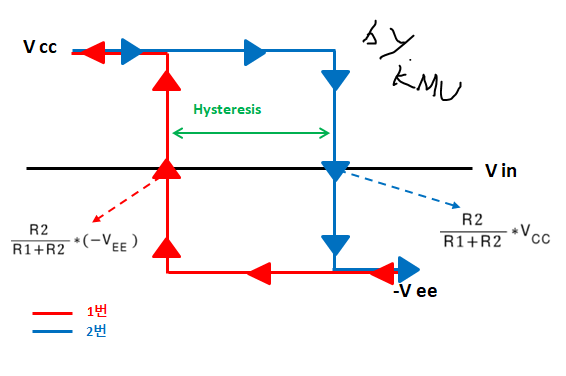

슈미트 트리거

: 비교기의 일종으로 High와 Low 출력 만듬

- 활용목적

정현파를 구형파로 변환

신호 노이즈 제거

신호 Edge 명확히 함

Noise 제거, 안정적인 Clock 신호, 회로 입출력 속도 증대에 주로 사용

-

히스테리시스 곡선

출력이 현재 상태에 의존하는 특성

H->L 전압과 L->H 동작 전압이 다름 -

입력진폭이 일정 값(Vt) 넘으면 급격히 작동해 일정한 출력 얻음

특정값 이하면 즉시 복구

입력 교류파형 특정 전압레벨 이상 or 이하면 출력이 논리전압레벨 '0' 또는 '1' 로 변함

구현회로

UTP (Upper Triggering Point)

: Low 상태에서 전위 상승할 때, High로 인식되는 기준 전압

LTP (Lower Triggering Point)

: High 상태에서 전위 하강할 때, Low로 인식되는 기준 전압

히스테리시스 이용 검출 회로 (Comparator with Hysteresis)

SUMMARY

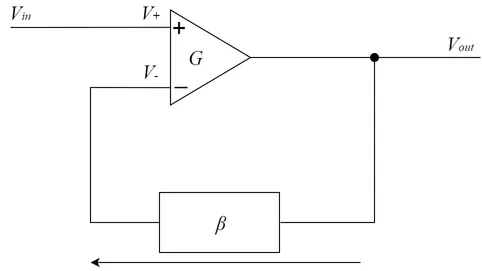

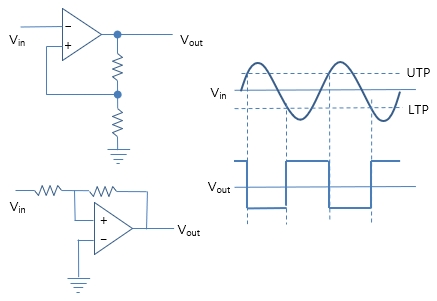

OP-AMP 피드백 적용 방식 (폐쇄 루프 회로)

(1) 기본 피드백 루프

이 회로는 반전 피드백(Negative Feedback) 방식을 사용하여 안정적인 전압을 유지합니다.

- 비반전 입력(+) : 기준 전압이 입력됨.

반전 입력(-) (피드백 경로) : OP-AMP의 출력 전압 중 일부가 저항 네트워크를 통해 반전 입력으로 되돌아옴.

🔹 출력 조절 원리

OP-AMP는 입력 차이를 최소화하려고 작동함 → 자동으로 목표 전압에 맞춰 출력 조절.

(2) 회로에서의 피드백 역할

-

OP-AMP의 출력 전압이 너무 높으면, 피드백 루프가 이를 감지하여 출력 신호를 낮춤 → 전압 하강.

-

OP-AMP의 출력 전압이 너무 낮으면, 피드백 루프가 이를 감지하여 출력 신호를 높임 → 전압 상승.

이를 통해 출력 전압이 설정된 목표값을 초과하거나 부족하지 않도록 유지.

피드백 시스템의 실제 회로 동작

🔹 정상적인 동작 시

DAC가 2V를 출력하면 OP-AMP 피드백을 통해 출력 전압도 2V가 되도록 자동 조정됨.

🔹 출력 전압이 목표보다 낮아졌을 때 (예: 1.8V)

OP-AMP는 비반전 입력(+)과 반전 입력(-)을 비교.

OP-AMP 출력이 증가하여 MOSFET이 더 도통됨.

결과적으로 캐소드 출력 전압이 증가하여 목표값(2V)로 복귀.

🔹 출력 전압이 목표보다 높아졌을 때 (예: 2.2V)

OP-AMP는 출력이 목표보다 높음을 감지.

OP-AMP 출력이 감소하여 MOSFET이 덜 도통.

캐소드 출력 전압이 감소하여 목표값(2V)로 복귀.

Ref

https://twojun-space.tistory.com/83

https://m.blog.naver.com/lagrange0115/220700508042

https://eunkyovely.tistory.com/70

https://tech-factory.tistory.com/entry/%ED%9A%8C%EB%A1%9C%EC%9D%B4%EB%A1%A0-OPAMP%EC%97%B0%EC%82%B0%EC%A6%9D%ED%8F%AD%EA%B8%B0-%ED%95%B4%EC%84%9D

https://2n3904blog.com/low-noise-high-psrr-ldo-error-amplifier/

https://mathphysics.tistory.com/445

Ref

https://m.blog.naver.com/sedi1017/222962875993

https://johnnyjay.tistory.com/53

http://www.ktword.co.kr/test/view/view.php?no=4566

https://blog.naver.com/PostView.naver?blogId=blslrtm&logNo=221530471927

https://blog.naver.com/lymcall/222985573825