NPU의 연산부는 convolution, Relu, maxlooling을 수행할 수 있어야한다. 이전 포스팅에서 convolution을 다루는 부분을 설명했으니 다음은 Relu와 maxpooling을 수행하는 모듈에 대해 설명해보자.

두 모듈은 convolution을 수행하는 모듈에 비해 매우 간단하다.

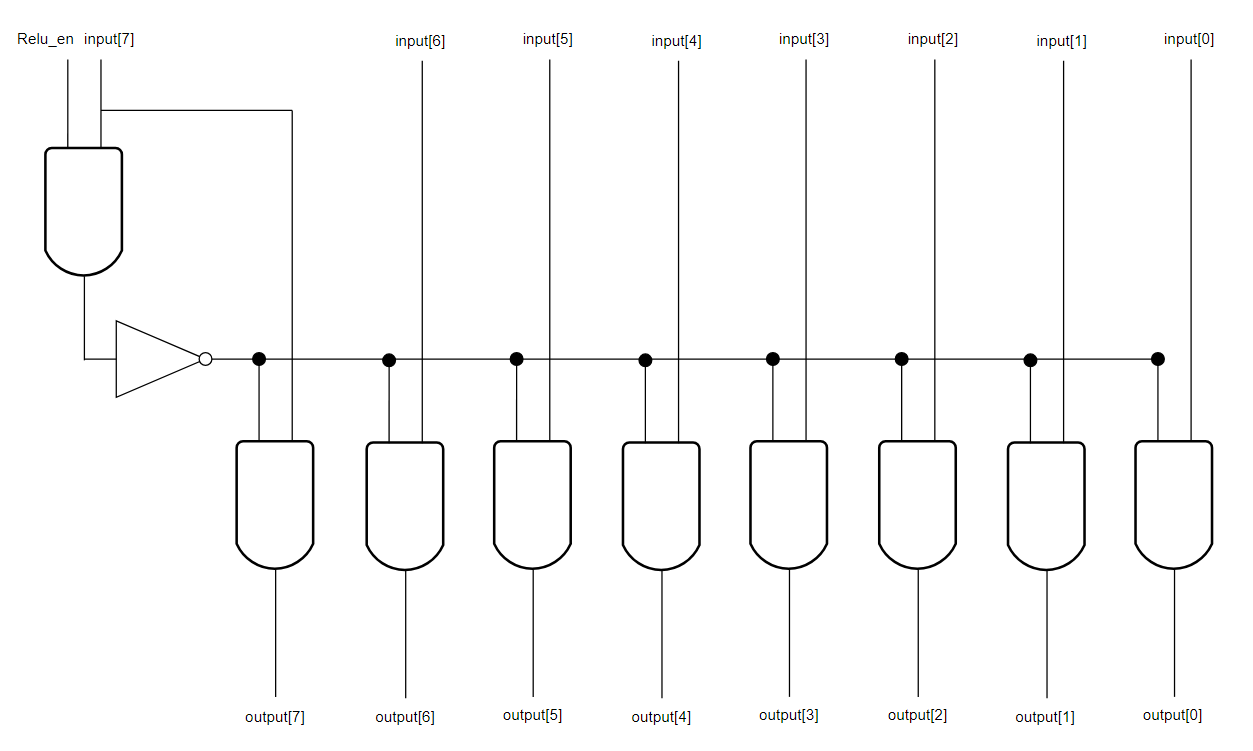

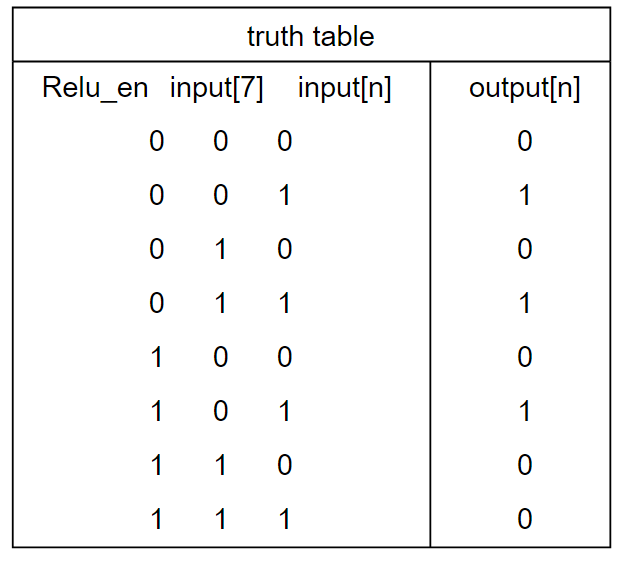

Relu 모듈

간단하게 Relu_en과 input[7]이 둘 다 1인 경우에만 무조건 0을 출력하고 그외의 경우에는 input[n]이 그대로 output[n]으로 출력되게 하면 된다.

Relu_en은 Relu 기능을 사용할지 말지를 결정하는 신호이다.

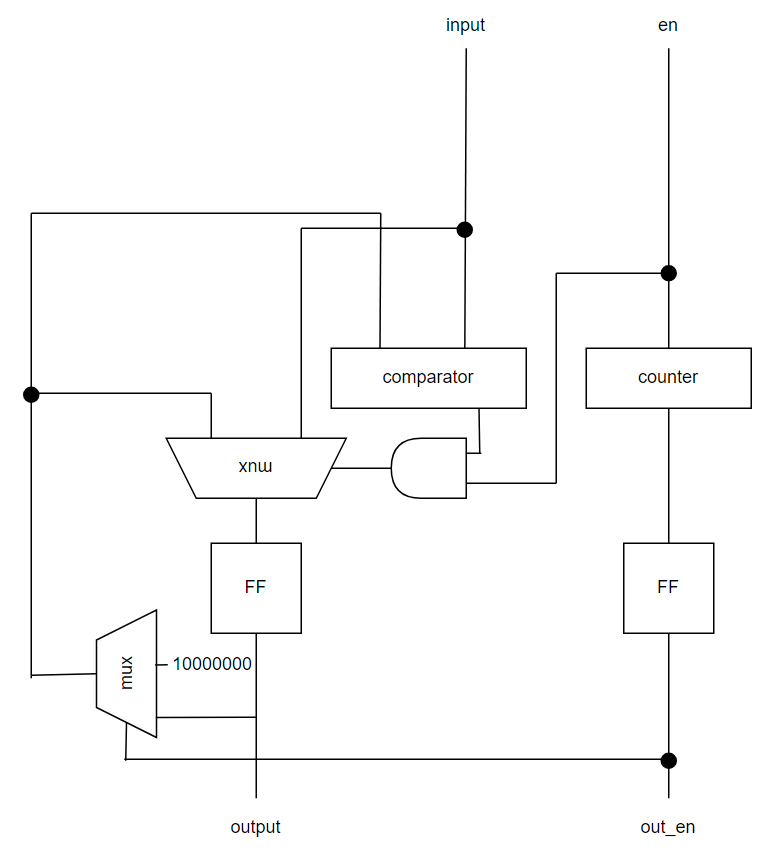

maxpooling 모듈

아깝게도 지원하는 maxpooling 2*2, stride 2 뿐이다. 대부분의 신경망에서 이것만 사용하고 그 외의 maxpooling을 지원하기 위해선 여러가지 모듈을 추가해야하기에 이것만 지원하도록 설계했다.

counter의 비트수를 늘리면 3*3, stride 3이나 4*4, stride 4 등도 가능하겠으나 이를 사용하는 신경망이 거의 없을 것으로 예상하기에 하지 않았다.

maxpooling 모듈 역시 매우 간단한 구조다. en이 1일 때 input 값이 FF에 저장된 값보다 크면 FF의 값이 새로운 값으로 갱신된다.

또한 en 신호가 들어온 횟수마다 count를 1씩 증가시켜 4번 들어올 때마다 out_en 1을 출력한다.

결과적으로 en이 1일 때 들어온 값이 4개 일때마다 out_en이 1로 출력되고 비교기에 최저값을 보내 input이 그대로 FF에 저장되게 했다.

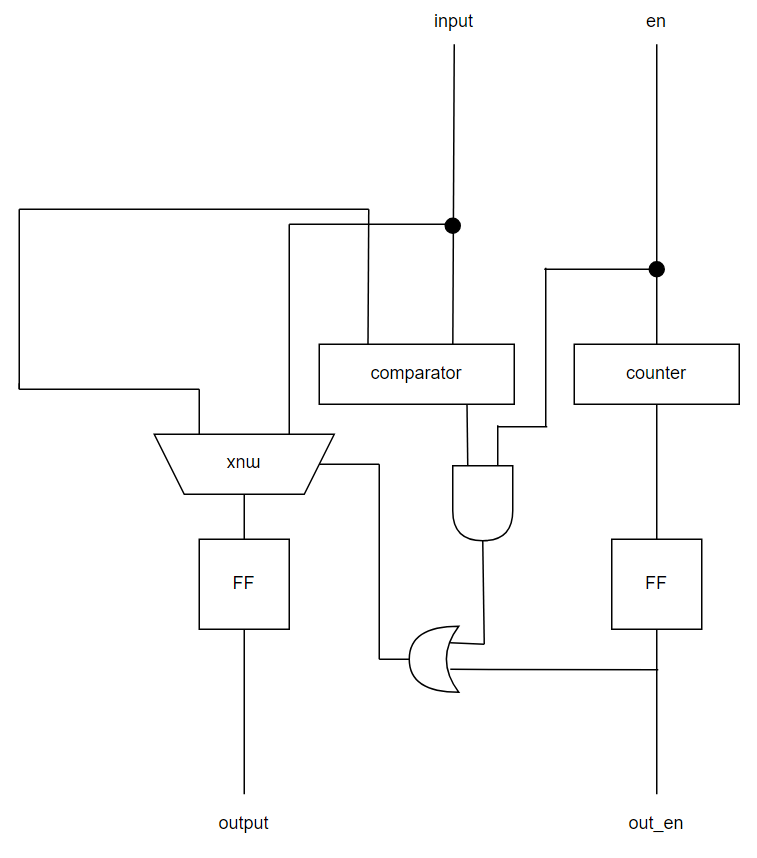

사실 면적을 고려할 경우

이 구조가 훨씬 낫다. 8비트 mux보다 or gate가 차지하는 면적이 훨씬 작기 때문이다.

하지만 이 경우 out_en이 1로 출력되는 사이클에 en=0인 경우 문제가 생길 수 있기에 부득이하게 mux가 있는 구조를 선택했다. 다만 좀 더 궁리를 한다면 면적을 줄일 수 있을 것으로 보인다.

이것으로 연산부의 하위 모듈들에 대한 설명이 모두 끝났다. 다음에는 가독성을 위해 생략된 부분까지 전부 포함된 연산부의 전체 아키텍처를 설명할 예정이다.