Gate Delay / Timing Diagram

- 논리 회로의 입력이 바뀌더라도 출력이 바로 바뀌진 않는다.

- Transister / Switching element 들은 바뀐 입력에 반응하는데 시간이 걸린다.

- 거기에 걸리는 시간을 Gate Delay라 부른다.

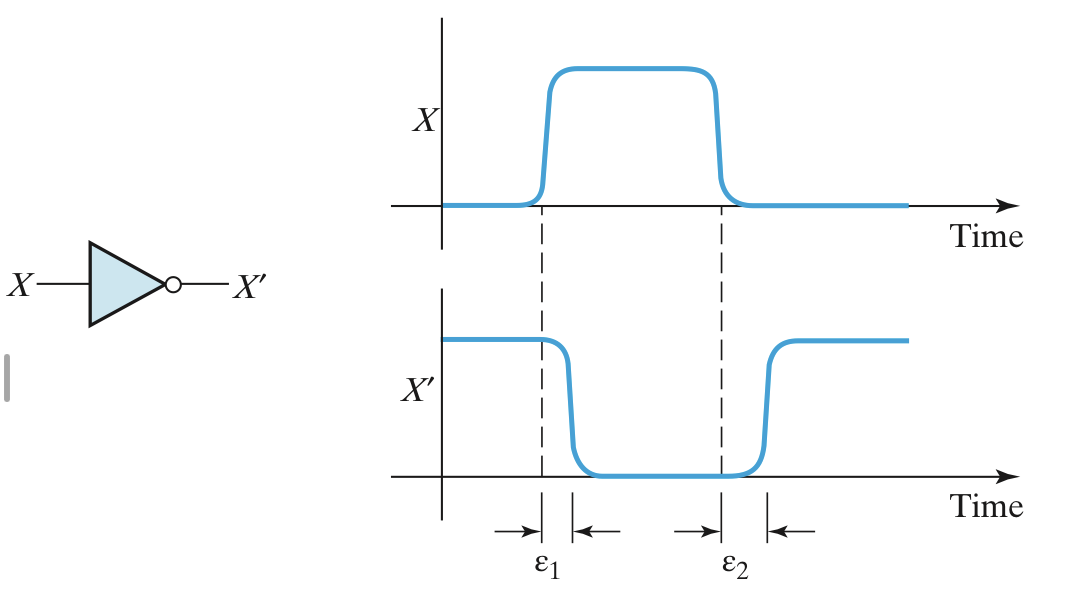

NOT Gate에 대한 Timing Diagram과 측정되는 Gate Delay

- 순차회로의 표현에 많이 사용한다.

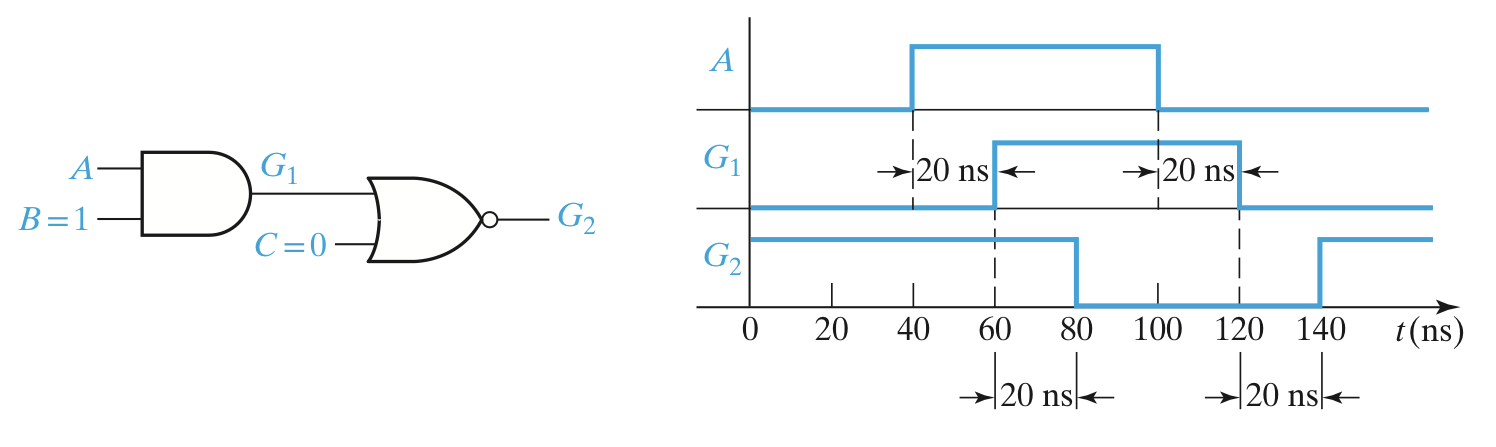

여러 게이트의 Timing Diagram

각각의 Gate Delay는 20ns로 측정된다

신호가 시작하는 지점 / 끝나는 지점에 둘 다 Delay가 관측된다는 사실을 기억해야 한다.

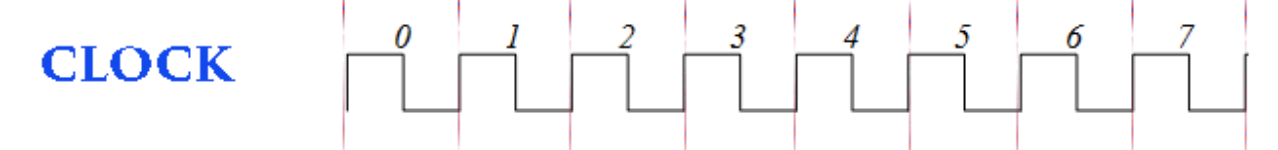

CLOCK

- 1hz : 1초에 1번 clock

- 10hz : 1초에 10번 clock

Hazard in Combinational Circuit

- 원하지 않은 잡음으로 인한 펄스

Static hazard

- 신호가 0이거나 1인 상황에서 갑자기 pulse가 생기는 것.

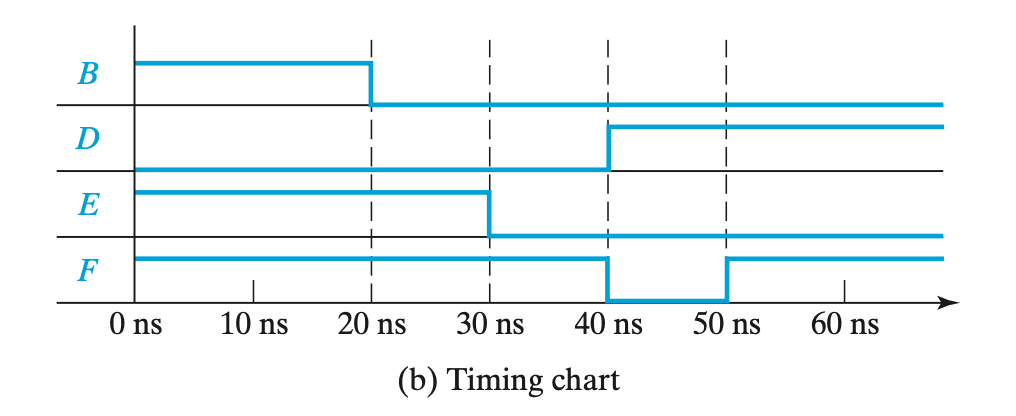

Static 1 Hazard 의 예시

- 의 경우 그래프를 그리면 아래와 같다.

- input은 전부 1이 들어가고 있다고 가정한다.

- 위의 Timing Diabram을 그리면 다음과 같다

- B의 Input만을 갑자기 0으로 바꾼 경우이다.

- F의 값은 계속 1을 유지해야 정상이나, 딜레이로 인하여 잠시 0으로 내려앉는 부분이 생긴다. >> Hazard가 발생한다, 비정상적 반응

- D 출력은 NOT Gate / AND Gate 딜레이, 즉 2개의 Delay가 적용되기 때문에 생기는 일이다.

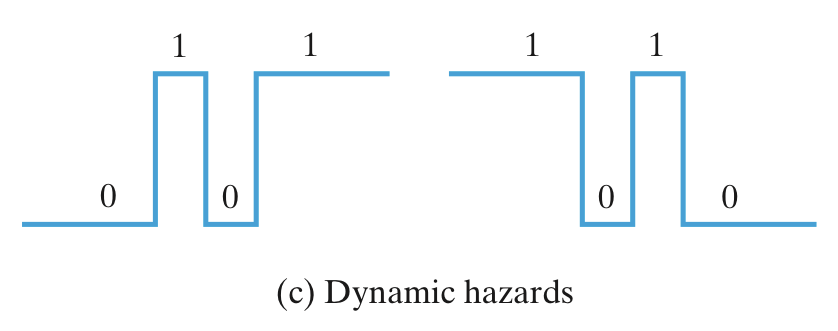

Dynamic hazard

- 값이 변하는 상황에 순간적으로 pulse가 생기는 것.

- 이 또한 Gate Delay의 차이로 인해 비 정상적 상태가 생기는 것이다.

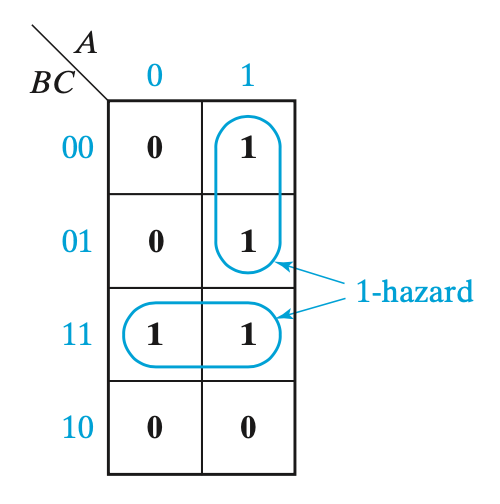

Karnaugh map

- prime implicant 내부에서 입력값이 바뀐다면 hazard가 생기지 않는다.

- EX . A = 1 B = 1 C = 1 >> A = 0 B = 1 C = 1

- 겹치지 않는 prime implicant로 입력값이 바뀐다면 hazard가 생긴다.

- EX . A = 1 B = 1 C = 1 >> A = 1 B = 0 C = 1

- EX . A = 1 B = 1 C = 1 >> A = 1 B = 0 C = 1

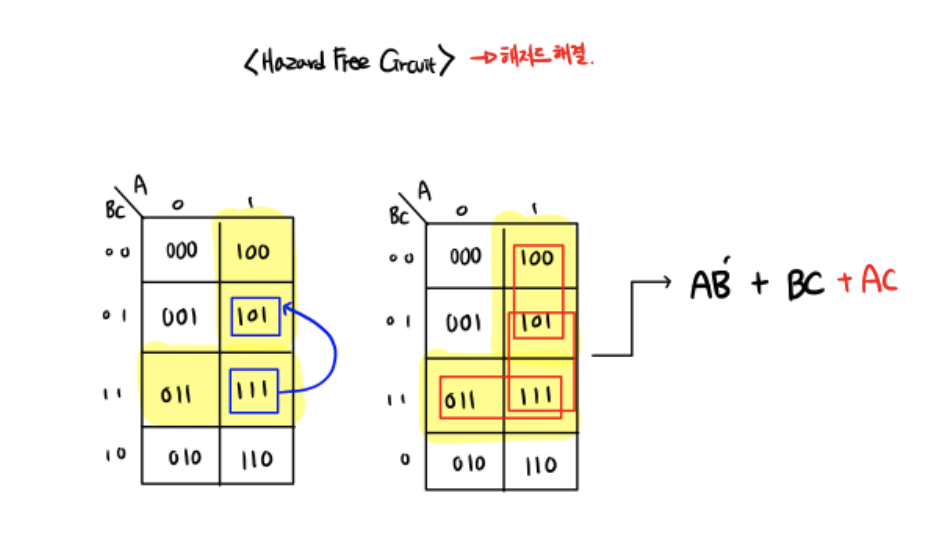

- 두 Prime implicant를 이어주는 term을 하나 더 추가시 hazard-free 가 된다.

- 여기서 추가한것은 Term 이다.

카르노 맵을 통해 maxterm을 구하더라도 동일한 법칙이 적용된다!

영향

- 정상적인 결과값을 언제 받을수 있을지에 영향을 끼친다.