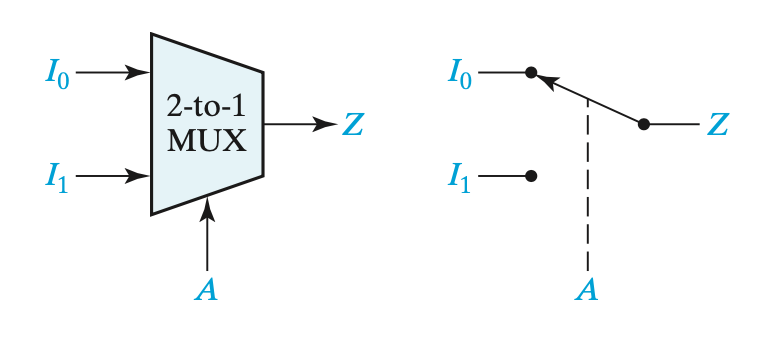

Multiplexer

- 멀티플렉서는 여러 데이터 입력을 선택해 출력과 연결해 준다.

- 값에 따라 둘중 하나를 output에 연결한다.

- A는 Control Input이라 부른다.

- 최대 개의 입력에 대해 개의 Control Input이 필요하다.

- 개 입력에 개의 출력 : multiplexer

- 여러 입력중 하나를 선택해야할때 사용한다.

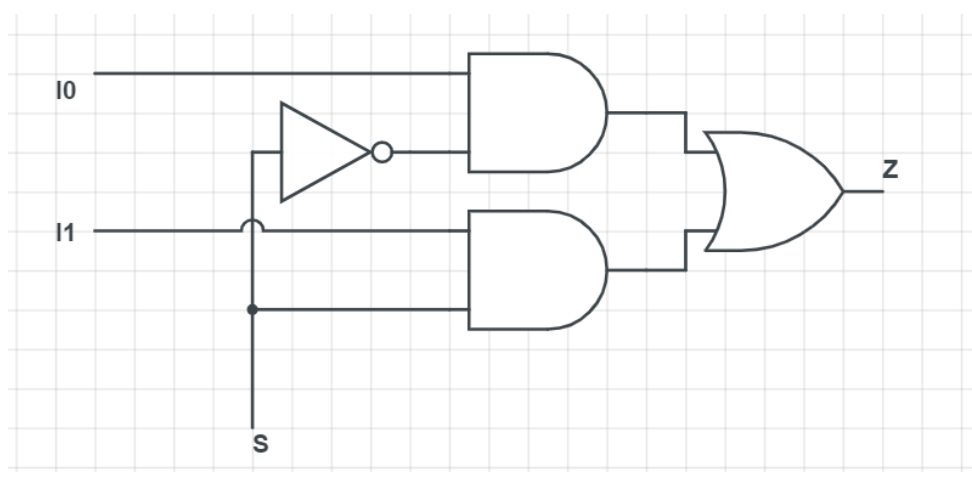

2 X 1 Multiplexer의 Logic gate

_s : Control input, 0일때 I0, 1일때 I1이 선택된다._

_s : Control input, 0일때 I0, 1일때 I1이 선택된다._

Logical Expression

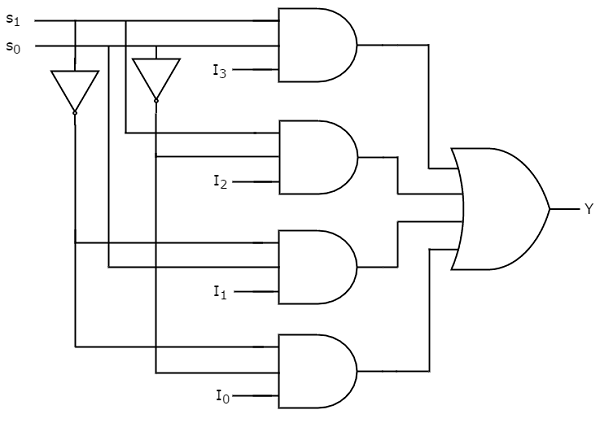

4 X 1 Multiplexer Logic gate

응용

- 8 to 1 MUX 를 2 to 1 MUX와 4 to 1 MUX 로 구현 가능하다.

8 to 4 Multiplexer

- 1개의 Control input이 필요하다.

- 4개의 2 to 1 Multiplexer로 구현할수 있다.

En 입력

- MUX의 동작상태를 정하기 위해 Enable bit을 사용할수 있다

- En : 0 >> MUX 작동 안함

- En : 1 >> MUX 작동 함

Active High, Active Low

- Active High : 1일때 동작하는 회로

- Active Low : 0일때 동작하는 회로

EX. Active High인 Reset 입력 >> 1이 들어오면 reset 기능이 활성화 된다.

MUX를 이용해 회로 구성하기

- A, B, C, D의 입력을 받는 회로에 대해

- A, B의 조합과 C, D를 선택선으로 사용해 구성 가능하다.

- Karnaugh map을 Row로 묶어 A, B의 조합을 Input으로, C, D를 Control Input으로 사용해 구현한것이다.

- Karnaugh map을 Column로 묶어 C, D의 조합을 Input으로, A, B를 Control Input으로 사용해 구현한 할 수도 있을것이다.

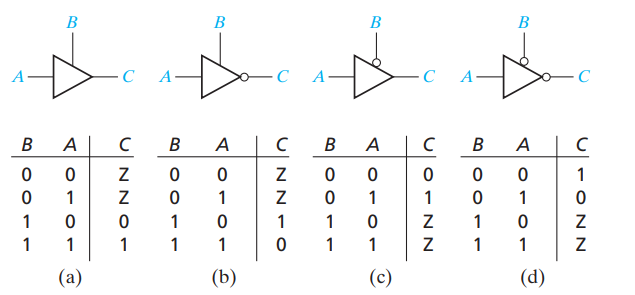

Three State Buffer

- 버퍼 : 잠시 값을 저장했다 어느정도 딜레이 이후 보내주는 회로

- 들어오는 신호를 증폭시키기 위해 사용한다.

A : 입력, B : 제어선, C : 출력

작동

- B가 1이면 A 신호가 그대로 전달된다.

- B가 0이면 A 신호가 전달되지 않는다

- High Impedence / 개방회로

- Z : High impedence 상태 - 높은 저항으로 인해 전류가 흐르지 않는다.

- (c)와 (d)는 b에 NOT Gate 가 있어 거꾸로 작동한다.

- 버스와 같은 선로에서 다른 장치들이 사용 중일때 사용하지 않는 장치들의 버스와의 연결을 끊을때 주로 사용한다.

Decoder / Encoder

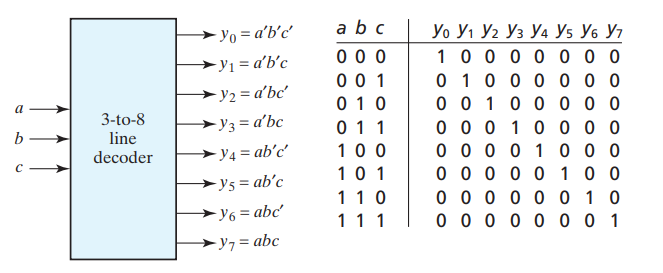

Decoder

- 비트의 입력에 대해 비트의 출력이 나온다.

minterm을 구하는 간단한 3 to 8 Line Decoder

- 각각의 output의 minterm 쌍의 역할을 하게 된다!

- minterm 으로 이루어진 SOP expression의 logic gate를 쉽게 구현할수 있다.

- 이 외에도 주소 지정, 특정 회로만 동작하도록 지정 하는 등의 동작을 구현할수 있다.

아래는 중간고사 범위에는 포함되지 않습니다!

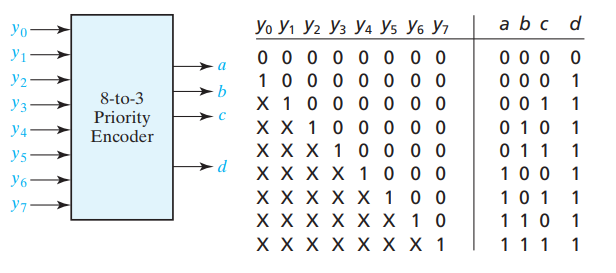

Encoder

- 비트의 입력에 대해 비트의 출력이 나온다.

8 to 3 Line Encoder

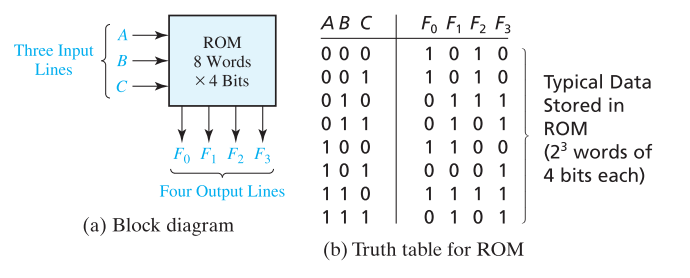

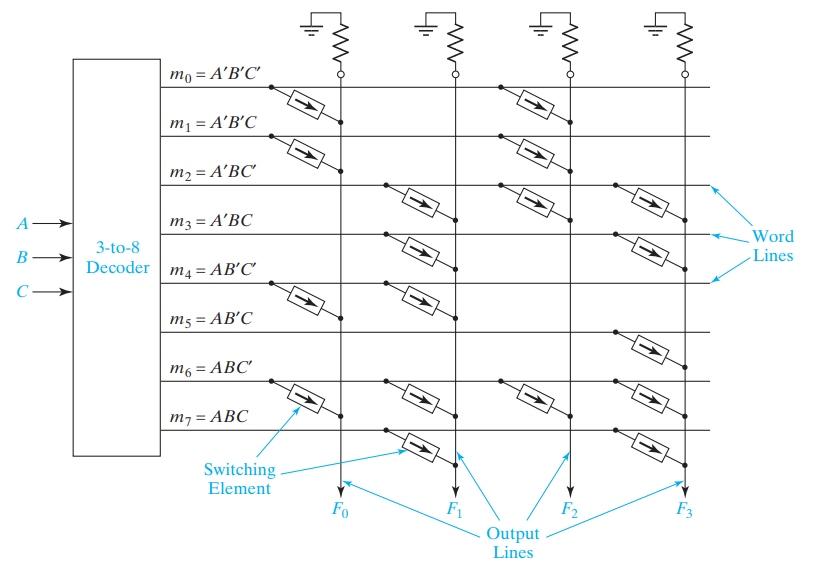

Read-Only Memories

- n개의 입력을 받아 bit의 정보를 저장할수 있다.

- 받는 입력은 일종의 "주소" 역할을 한다.

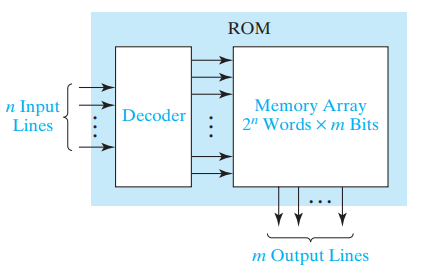

- 받은 주소는 디코더를 통해 1개의 Line을 선택하는데 사용된다.

개략적인 모습

4비트의 정보를 총 2^3개 저장하고 있다

실제 모습

- 먼저 n to 2^n Line decoder를 거쳐 메모리 배열에서 가져올 Line을 찾는다.

- 우회로를 거쳐 Output으로 나갈 경우, 값이 1이 되며.

- 우회로를 거치지 않을 경우 윗쪽의 GND로 빠져 나가 값이 0이 된다.