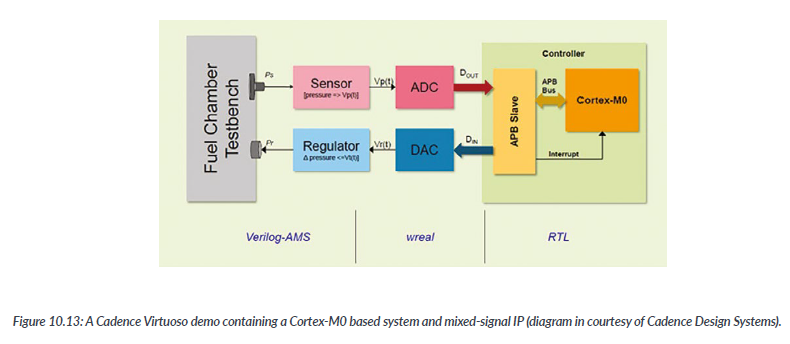

10.3.5 Connecting ADC and DAC IPs into a Cortex-M system.

In instances where you license ADC or DAC IPs, these components usually procide simple digital interfaces. To connect them t oa Cortex-M system, the typical integartion task includes the following step :

- Addding an APB bus wrapper for various data and control registers(please note that, potentially, additional level shifters migh be needed in the bus wrapper design).

Adding interrupt handling logic(and registers) to handle completion of conversion or error cases

Creation of software driver code and create test codes for system-level simulations.

To help system-level verification, a number of EDA tool vendors offer solutions for mixed-signal verification, including simulators that can handle verilog. For example, cadence virtuisi can handle co - simulation of RTL, Verilog - AMS, and wreal :

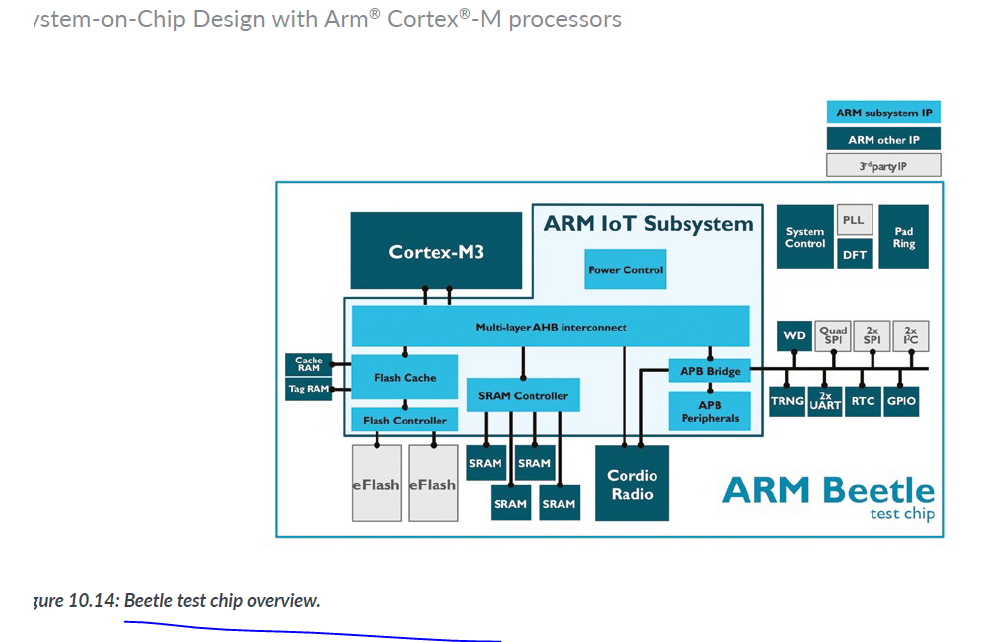

10.4.1 Beetle test chip overview

A represntative pakage for low-cost IoT endpoints;

Suitable for Buletooth wireless designs

Additional pins for multiple voltage supply - since we did not integrate and on-chip DC-DC votage converter, we need to allocate multiple voltage supply pins for the different voltage levels used by different parts of the chips.

The Cordio IP requires a number of dedicated pins for power, oscillators, and of course antenna and RF interface.

Since we would like to enable all debug features to be used at any time, we did not multiplex debug pins with functional pins.

Severl pins are required to control test modes that expose internal signals for testing.

On the upside, the limited pin situation is not such a problem as it may first seem becuase :

The bottom side of the chip provides a large ground connection, so we do not need to have many ground pins; and,

10.4.2 Beetle test chip challenges

Embedded flash;

A built-in wireless interface

A TSMC 55ULP process node;

The CoreLink SDK-100 IoT subsystem.

The success of the chip was a really rewarindg experience for the project team and everyone involved in the Beetle.