10.1 Clock system design

10.1.1 Clock system design overview

All processor systems need clock signals to operate.

For the majority of microcontroller systems, the clock signals are generated by the following means;

Internal crystal oscillators with external crystals, or

Internal oscilators(e.g., R-C oscillators), or

Inthernal Phase-Locked Loop(PLL).

When designing clock systems, several factors are typically considered:

Accuracy - Many peripherals and external communication interfaces require fairly high accuracy for the clock frequency. For external crystals, the accuracy is often expressed as PPM(Part Per milion), and commercial products usually require 40ppm or better accuracy for the crystal oscillators internal R-C oscilators typically are not accurate( some can have up to 20% error).

Duty cycle - Typically, the clock sources should provide a square wave with a 50% duty cycle. For Cortex-M based systems, since all register in the processor and the bus system trigger at the system clock's rising edge, a small inaccuracy in the duty cycle is unlikely to cause any problems.

However, when dealing with an interface with DDR(double data rage) operations, accuracy in clock duty cycle can be very important.

Low-power- A crystal oscillator running at a high clock speed can consume a lot of power. So if high clock speed are required, a slower crystal oscilator is often used to generate a reference clock and a PLL to generate a high grequency clock out of it. When the system does not need the high clock speed, the PLL can be turned off to save power. Another common requirement for low-power systems is to provide an ultra-low-power clock source for Real Time Clock and a periodic interrupt source for RTOS. it is therefore relatively common for microcontrollers to have a crystal oscillator for the system clock and a 32kHz crytal oscillator for the RTC clock.

저전력: 고 클록 속도에서 동작하는 크리스탈 오실레이터는 많은 전력을 소비할 수 있습니다. 따라서 높은 클록 속도가 필요한 경우, 보통 느린 크리스탈 오실레이터를 사용하여 참조 클록을 생성하고, 이를 기반으로 PLL을 사용하여 고주파 클록을 생성합니다. 시스템에서 높은 클록 속도가 필요하지 않은 경우, 전력을 절약하기 위해 PLL을 비활성화할 수 있습니다.

저전력 시스템의 다른 일반적인 요구 사항은 실시간 시계 (RTC)에 대한 초 저전력 클록 소스와 실시간 운영 체제 (RTOS)에 대한 주기적 인터럽트 소스를 제공하는 것입니다. 따라서 마이크로컨트롤러에서는 시스템 클록을 위한 크리스탈 오실레이터와 RTC 클록을 위한 32kHz 크리스탈 오실레이터가 함께 사용되는 것이 비교적 일반적입니다.

Clock distribution inside the chip - In chapter 9, we mentined the topic of clock tree synthesis during clock design flow. In many system designs, we need to make a clock edge that arrives at different parts of the processor system at the smae time. Clock tree balancing during clock tree synthesis is required to achieve this goal. In addtional delays caused by clock signal propagration delay, clock tree balancing must also take account of additional delays cause by clock gating cells, and, potentially, additional clock skew and clock jitters. What is more, if all this wasn't enough to make your design flow complicated, the clock tree can use up a considerable amount of power consumption.

칩 내부의 클록 배포 - 9장에서 클록 설계 과정 중 클록 트리 합성에 대해 언급했습니다. 많은 시스템 설계에서는 프로세서 시스템의 다양한 부분에 동시에 도달하는 클록 엣지를 만들어야 합니다. 클록 트리 합성 중 클록 트리 밸런싱은 이 목표를 달성하기 위해 필요합니다. 클록 신호 전파 지연 외에도, 클록 트리 밸런싱은 클록 게이팅 셀에 의한 추가적인 지연 및 잠재적으로 추가되는 클록 스쿠 및 클록 지터(불확실성)를 고려해야 합니다. 게다가, 모든 이러한 요소들이 설계 흐름을 복잡하게 만드는 데 충분하지 않다면, 클록 트리는 상당한 전력 소비를 필요로 합니다!In some cases, application-specific IC designs can have additional clock source requirements For example, chip designs with USB interfaces might require accurate 12MHz or 48MHz clock sources.

10.1.2 Clock switching

When there are multiple clock sources in the system, one of the design challenges is to handle the switch over from one clock source to another. In a microcontroller application, you might have multiple scenarios in which different clock sources are used - for example :

When the processor system is running background code, the processor's clock may be driven from the crystal oscillator.

when the processor system receives a certain processing workload, it needs higher performance and therefore switched from the crystal oscillator's clock to a PLL-generated high-frequency clock.

When there is nothing to process, the processor enters sleep mode during which only the RTC is running(PLL and other oscillator turned off to minimize power consumption). The processor system might in this state need to use the RTC clock to wake up the memory controllers after an interrupt request is received.

시스템에 처리할 작업이 없을 때 프로세서는 슬립 모드로 전환되며, 이 동안에는 RTC만 동작합니다 (전력 소비를 최소화하기 위해 PLL 및 다른 오실레이터가 꺼짐). 프로세서 시스템은 이 상태에서 인터럽트 요청을 수신한 후에 메모리 컨트롤러를 깨워야 할 수 있으며, 이를 위해 RTC 클록을 사용해야 할 수 있습니다.As a result, the clock system design needs to suppport switching over from one clock source to another, - and this process needs yo be glitch-less . If a clock glitch enters the processor system, some of the registers can be affected by mestastability issues and enther an undefined state, and the system will not be able to resume mormal operations.

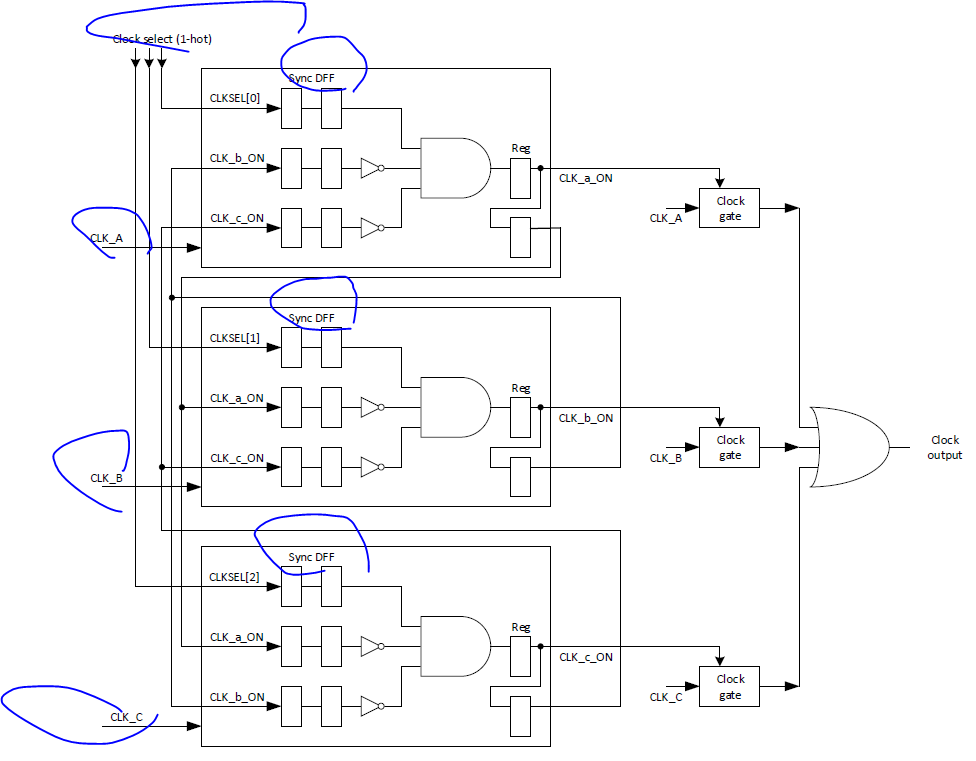

One way to provide glitch-free clock switching is to implement a clock switching FSM in each of the clock domains and to enable their clock output only if non of the other clock output FSMs are outputting.

결과적으로, 클록 시스템 설계는 한 클록 소스에서 다른 클록 소스로의 전환을 지원해야 하며, 이 과정은 글리치가 없어야 합니다. 만약 클록 글리치가 프로세서 시스템으로 진입한다면, 일부 레지스터는 메타스터빌리티 문제로 영향을 받아 정의되지 않은 상태로 진입하게 되며, 시스템은 정상적인 동작을 재개할 수 없게 될 것입니다.

글리치 없는 클록 스위칭을 제공하기 위한 한 가지 방법은 각 클록 도메인에 클록 스위칭 FSM을 구현하고, 다른 클록 출력 FSM 중 어떤 FSM도 출력하지 않을 때에만 해당 클록 출력을 활성화하는 것입니다

The clock gating cells and the OR gate that merge clock sources need to be instantiated and cannot be generated by synthesis. This prevents the synthesis process from reordering logic gates that can result in glitchs. The reset values of the flip-flop might need to be customized if you wnat to allow the system to be started up with the clock running.

클록 게이팅 셀과 클록 소스를 병합하는 OR 게이트는 인스턴스화되어야 하며, 합성 과정에서 생성되지 않습니다. 이는 합성 과정에서 로직 게이트의 재배치로 인해 글리치가 발생할 수 있는 것을 방지합니다. 또한, 플립플롭의 리셋 값은 클록이 실행되는 상태에서 시스템을 시작할 수 있도록 하려면 사용자 정의해야 할 수도 있습니다.10.1.3 Low-power considerations

Crystal oscillators and PLL hardware are often delivered to chip desingers as hard macros and simulation models. To enable low power optimizations at the application level, many of these designs include power control interfaces that allow the oscillator of the PLL to be powered down when they are not being used.

A problem with powering down oscillators and clock sources during sleep is that, in manyt cases, we still need to have a clock source for various power management hardware, which requires clocks(they might have internal state machines to power up memories). Therefore, chip designers must ensure that either one of the active clock source is kept active, or that the oscillator's control is designed so that after a wake-up event is triggered, an oscillator could start automatically to support the power-up sequence.

Becareful about the wake-up time required for the oscilator and PLL, including the effect of various operating temperatures and voltages. Typically, a finite state machine is needed to ensure that the clock singal to the processor system is gated off until it is fully stabilized. This is why the 32kHz clock is usually left running during sleep mode so that the FSM can rely on this clock to operate.

저전력 모드에서의 클록: 저전력 모드에서는 일부 하드웨어가 작동하기 위해 클록 소스가 필요한 경우가 있습니다. 이를 위해 최소한 하나의 활성 클록 소스를 유지하거나, 깨어남 이벤트 후 오실레이터가 자동으로 시작되도록 설계되어야 합니다.

클록 신호 안정화: 클록 신호가 완전히 안정될 때까지 클록 신호를 차단하기 위해 유한 상태 기계(FSM)를 사용하는 것이 일반적입니다. 이를 위해 32kHz 클록이 수면 모드에서 계속 동작되도록 설정하는 것이 보통입니다.10.1.4 DFT considerations

An important aspect of clock system design is Design for Testing(DFT). During scan tests, clock signals need to be controllable from the ATE, and that means internal clock switches, clock gates, and internal clock source such as PLL have to be bypassed. Some of the PLL designs also have scan chains that need to be hooked up and might have additional scan mode control signals.

In addition, some PLL designs provide test mode that can help chip designers to analyze the performance of the PLL in the implemented chips. To use such features, you might need to implement test modes that allow certain PLL signals to be observable at the top level of the chip.

10.1.4 DFT (Design for Testing) 고려 사항

클록 시스템 설계의 중요한 측면은 테스트를 위한 설계 (DFT, Design for Testing)입니다. 스캔 테스트 중에는 클록 신호를 ATE (Automatic Test Equipment)에서 제어할 수 있어야 하며, 이는 내부 클록 스위치, 클록 게이트, PLL과 같은 내부 클록 소스를 우회해야 함을 의미합니다. 일부 PLL 설계에는 스캔 체인이 포함되어 있어 연결되어야 할 수 있으며, 추가적인 스캔 모드 제어 신호가 있을 수도 있습니다.

또한, 일부 PLL 설계는 구현된 칩에서 PLL의 성능을 분석하는 데 도움이 되는 테스트 모드를 제공할 수 있습니다. 이러한 기능을 사용하려면 일부 PLL 신호를 칩의 상위 레벨에서 관찰할 수 있도록 특정 PLL 신호를 관찰 가능하도록 하는 테스트 모드를 구현해야 할 수 있습니다.10.2 Multiple power domains and power gating

In low power system designs, we often define multiple power domains in a chip and allow some to be powered down when they are not needed. This technique is calles power gating.

Unlike clock gating(which simply reduces dynamic leakage), power gating also removes static leakage currents. However, as system states may be lost by removing power, there are trade-offs to be made - it may take time to save and recover the necessary state information and remove and restore power. A special form of power gating called State Retention Power Gating is availble, but SRPG flip flops are larger than standard flip-flops, have a slightly higher dynamic current, and need an addtional power rail to support retention.

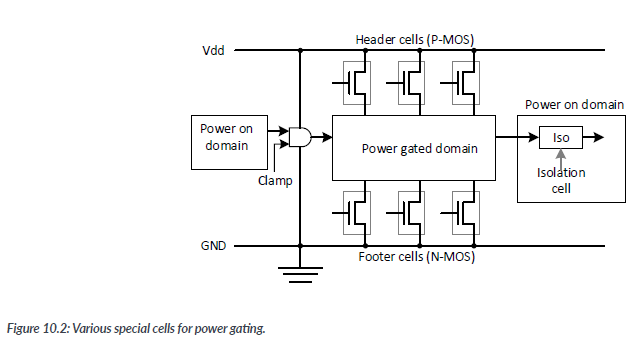

To handle power gating and state retention power gating, we need special physical IP for power gating:

Header cells;

Footer cells;

Isolation cells;

State retention flip-flops(registers)(for SRPG only).

10.2 다중 전원 도메인 및 전원 게이팅

저전력 시스템 설계에서는 칩 내에서 여러 전원 도메인을 정의하고 필요하지 않을 때 일부 도메인의 전원을 차단할 수 있습니다. 이 기술을 전원 게이팅(power gating)이라고 합니다.

전원 게이팅은 동적 누설 전류를 감소시키는 클록 게이팅과는 달리 정적 누설 전류를 제거합니다. 그러나 전원을 차단함으로써 시스템 상태가 손실될 수 있으므로 일정한 트레이드오프가 있습니다. 필요한 상태 정보를 저장하고 복구하며 전원을 차단하고 복원하는 데 시간이 소요될 수 있습니다. State Retention Power Gating (SRPG)라고 불리는 특수한 전원 게이팅 형태도 있지만, SRPG 플립플롭은 표준 플립플롭보다 크기가 크며, 약간 더 높은 동적 전류를 필요로하며, 보유를 지원하기 위해 추가적인 전원 레일이 필요합니다.Footer cells and footer cells - On chip power gating typically involves inserting large, high - Vt(thresgold voltage), low-leakage PMOS(on supply connection side) and /or NMOS(on ground conncetion)sleep transistors into the chip's power network. this means that the devie's power network consists of :

A power network that is permanently turned on( connected to an external supply), and

A number of power islands, to which the power supply may be turned off

Isolation cells - Isolation cells are special cells that isolate a power gated block from other parts of the design which remain powerd up. These are required to prevent(1) short-circuit currents and (2) the inputs of other blocks from floating.

In some cases, when multiple power domains are used, it is possible to have different voltage levels, and in these situations, level shifters are also needed.

To support power gating design, Arm physical IP products have Power mManagement Kits that contain a range of these special components for multiple power domain designs. Different processnodes need different PMKs libraries.

The inclusiong of such power gates brings a range of complexity to the physical design :

IR-drop - The voltage supplied to individual fuinctional blocks will be lower than that provided to the chip, due to losses within the on-chip power distribution network. Power gate trnasistors need to be large in order to reduece the IR drop. In many cases, a number of header cells and footer cells are required to avoid this.

In-rush current - if a voltage island is large and all the header and footer cells are turning on simultaneoutsly, it causes a large 'in-rush currnet' that can result in problems to the integrity of the device' power grid. In order to prevent this problem , the header and footer cells often have buffered control output to allow power switching sequences to be chanined. This makes the time needed for swiching on a powe rdomina longer but can prenet large 'in-rush current' that can cause physical damage to the chip.

인러시 전류(In-rush current)는 전원 도메인이 켜질 때 초기에 발생하는 높은 전류 서지를 의미합니다. 특히 전압 섬이 크고 헤더 셀과 풋터 셀이 동시에 활성화되는 경우에 이러한 현상이 발생할 수 있습니다. 이러한 갑작스러운 전류 증가는 장치의 전원 그리드의 무결성에 문제를 일으킬 수 있으며 칩에 물리적 손상을 초래할 수 있습니다.

이러한 인러시 전류 문제를 방지하기 위해 헤더 셀과 풋터 셀에는 보퍼링된 제어 출력이 포함될 수 있습니다.헤더 셀(Header cell)과 풋터 셀(Footer cell)은 전력 관리 기술인 전원 게이팅(Power Gating)에서 사용되는 구성 요소입니다.

헤더 셀(Header cell): 헤더 셀은 전원 도메인의 시작 부분에 위치하여 전원을 제공하는 역할을 합니다. 전원이 필요한 도메인을 활성화하고 도메인 내의 회로나 블록에 전원을 공급합니다.

풋터 셀(Footer cell): 풋터 셀은 전원 도메인의 끝 부분에 위치하여 전원을 차단하는 역할을 합니다. 전원이 필요하지 않은 도메인을 비활성화하고 도메인 내의 회로나 블록의 전원 공급을 차단합니다.

헤더 셀과 풋터 셀은 전력 게이팅을 통해 전력 소비를 관리하는데 사용됩니다. 전력이 필요한 도메인을 활성화하거나 비활성화함으로써 도메인 간의 전력 소비를 효율적으로 조절할 수 있습니다. 이를 통해 전력 소비를 최소화하고 저전력 시스템의 에너지 효율성을 향상시킬 수 있습니다.Power gating control skew rate - Another potential issue is that power gates themsevles can have leakage current, especially if the gating control signal is not well buffered and not reaching optimal voltage. Therefore, the timing of the power gate operation needs to be carefully considered to ensure that the slew rate of the power gate control signal is not too large.

슬루율은 전원 게이트 제어 신호가 전압이 변경되는 속도를 나타내며, 큰 슬루율은 전력 게이트가 불안정하게 동작하거나 누설 전류가 증가할 수 있는 원인이 될 수 있습니다. 따라서 전원 게이트 동작의 타이밍은 전력 게이트 제어 신호의 슬루율을 적절히 제어하여 안정성을 보장해야 합니다.

전력 게이트 제어 신호의 슬루율을 제어하기 위해서는 적절한 버퍼링 및 적절한 전압 레벨 조절이 필요합니다. 제어 신호의 슬루율을 줄이기 위해 인가된 전력 게이트 동작의 순간을 조절하여 전압이 불안정하게 변화하지 않도록 해야 합니다.Power gating also has cost implications in terms of die area and silicon routing. it requires specialist EDA tools and may make timing closure more difficult.

As explained in Chapter 6, there are a number of schemes to preserve the state of a block before it is shut down. While state retnetion power gating enables the state in the processor system to be retained during sleep, iw won't be useful if the states in peripherals and other system components are lost during sleep. So if state retention power gating is used, the components in the system that need to be powered down during sleep mode shold also have sate rention power gating(SRPG) implemented to ensure that software can make the most out of SRPG capability.

상태 보존 전력 게이팅(State Retention Power Gating, SRPG)은 프로세서 시스템의 상태를 수면 중에 보존할 수 있게 합니다. 그러나 상태 보존 전력 게이팅은 주변 장치와 다른 시스템 구성 요소의 상태가 수면 중에 손실되는 경우에는 유용하지 않을 것입니다. 따라서 상태 보존 전력 게이팅을 사용하는 경우, 수면 모드에서 전원을 차단해야 하는 시스템 구성 요소는 상태 보존 전력 게이팅(SRPG)을 구현하여 소프트웨어가 SRPG 기능을 최대한 활용할 수 있도록 해야 합니다.An alternatvie methos is to store the status of the parts of the applications that need to be preserved to a state retention RAM, before removing power. When power is restored, the software need to resotre the application ' state. The state that needs saving might include the processor's registers and peripheral configurations.

Of course, it is also possible to power down and simply restart the system when it is needed.

10.3 Arm processor in a mixed-signal world

10.3.1 Convergence of microcontrollers and mixed-signal designs

Traditionally, many microcontrollers are mostly digital in design with a few analog components, like ADCs and DACs.

PLLs and Oscillators;

ADCs;

DACs;

Voltage references;

Brwon-out detector;

Analog comparators;

LCD driver;

Touch sensor/CAP sense;

Wireless interface;

At the same time, analog components are getting mor intelligent. For example, traditional sensor ICs integrate mroe and more digitial logic including, processors and are becoming "smart" sensors. This can bring many advantages by enabling:

Better calibration;

Fault Detection and report to devices connected to it;

Better power management.

Since the Cortex-M processors are small, energy-efficient, and easy to use, they are widely used in microcontrollers and smart analog IC designs.

With Various sleep mode features and intelligency in software control, a range of mixed-signal designs can reach better levels of energy efficiency and, at the same time, provide more features than before.

When dealing with mixed-signal designs, additional complexities are added to the projects ; for example:

Design flow of analog components can be very different from digital. In some cases, Verilog-AMS can be used , and in others, some analog components are designed with manula chip layout. There is often a need for system-levle mixed-signal simulation and verification.

In some cases, CMOS manufacturing technology is not suitalbe for certain analog applications(e.g., power electronics, radio frequency circuits). /In many cases, BiCMOS is used for mixed-signal designs that combine CMOS, and bipolar transistor technologies on the same silicon die.

Many analog components need separated power domains(separated from the digital logic).

Additional considerations in a chip's power rail design and floor-planning are needed to reduce noise to sensitive analog componens. For exmaple, layout implementation techniques such as guard rings and well isolation are common techniques that can be used to prevent switching noise from a digital circuit reaching an analog circuit throught silicon suvstrate copling.

일부 경우, CMOS 제조 기술은 특정 아날로그 응용 분야(예: 전력 전자, 무선통신 회로)에 적합하지 않을 수 있습니다. 많은 경우, CMOS 및 양극성 트랜지스터 기술을 동일한 실리콘 다이에 결합하는 혼합 신호(mixed-signal) 설계에는 BiCMOS가 사용됩니다.

많은 아날로그 구성 요소는 디지털 로직과 분리된 전원 도메인이 필요합니다. 민감한 아날로그 구성 요소로의 노이즈를 줄이기 위해 칩의 전원 레일 디자인과 플로어 플래닝에 추가적인 고려 사항이 필요합니다. 10.3.2 Analog to digital conversions

There are many types of ADC available on the market. Depending on the application, there can be different slelction criteria for what type of ADC to choose. For example:

Conversion speed and sampling rate - When dealing with an input signal that a frequency range of X Hz, the minimum sampling rate needed is 2X Hz. And in may cases, even 2X Hz is not enough for quality and reliability reasons. For examplem imagine that a 4kHz sine we is sampled at 8 kHz: there is a chance that we will sample the input signal at 0 level all the time. Therefore, it is often necessary to have the sample rate more than 4 times that of the input singals. Plase note that the input bandwidth of an ADC can be much lower than half of sampling rate.

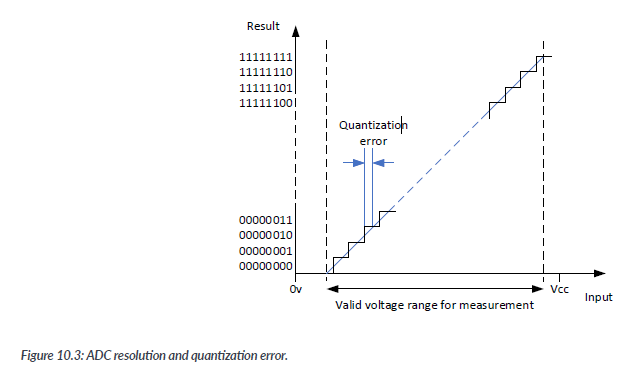

변환 속도와 샘플링 속도: 주파수 범위가 X Hz인 입력 신호를 처리할 때, 필요한 최소 샘플링 속도는 2X Hz입니다. 그리고 많은 경우에는 품질과 신뢰성을 위해 2X Hz만으로는 충분하지 않을 수 있습니다. 예를 들어, 4 kHz 사인파를 8 kHz로 샘플링한다고 가정해보면, 입력 신호를 항상 0 수준으로 샘플링할 수 있는 가능성이 있습니다. 따라서 입력 신호의 4배 이상의 샘플링 속도가 필요한 경우가 많습니다. 또한, ADC의 입력 대역폭은 샘플링 속도의 절반보다 훨씬 작을 수 있습니다.Resolution - This is expressed as the number of bits in the conversion results. For an on-chip ADC, Typical resolutions range from 8bit to 14bit the difference between the real value and the measured value is often referred to as the quantization error and is 1/2 of the LSB of the ADC in ideal cases, as shown in the diagram below:

Resolution - 이는 변환 결과에서 비트 수로 표현됩니다. 칩 내부 ADC의 일반적인 해상도는 8비트에서 14비트까지 범위가 있습니다. 실제 값과 측정 값 사이의 차이는 일반적으로 양자화 오차(quantization error)라고 불리며, 이는 이상적인 경우 ADC의 최소 유효 비트(LSB)의 1/2입니다. 아래의 다이어그램에서 확인할 수 있습니다.

Please Note that many on-chip ADCs have a measurement range less than the supply voltage range.

Singal to noise(SNR) rantio- this is often caculated using the number of bits in the results,by assuming the noise level is +/- LSB. SNR is often expressed in decibels, i.e.

SNRdb = 10log10(Psignal/Pnoise)

Givent that the ADC results are in the form of voltage values, we need to convert the formula by squaring the input values(or 2x after log10), thus :

Assuming that the ADC is 8-bit, the SNR calculation can be formulated as shown:

In some cases, you can use oversamplign and filtering techniques to reduce noise. But even if the ADC noise level is low, in many cases, noises from other parts of the integrated circuit and on the circuit board, could reduce the signal to noise ratio.

Suitability for the target process node - One of the challenges for mixed signal design is that analog circuit design does not scale well to small transistor geometries.

Area and power - Silicon area an the type of ADC directly contribute to cost and power. Based on the project requirements, some of the ADC types might not be suitable for these reasons.

Operating conditions - if you are designing a chip for industrial( or even automotive) applications, you will need to pay attintion to the operating temperature range of ALL the components that you use for the desing. some of the ADC and DAC might not work at high temperature.

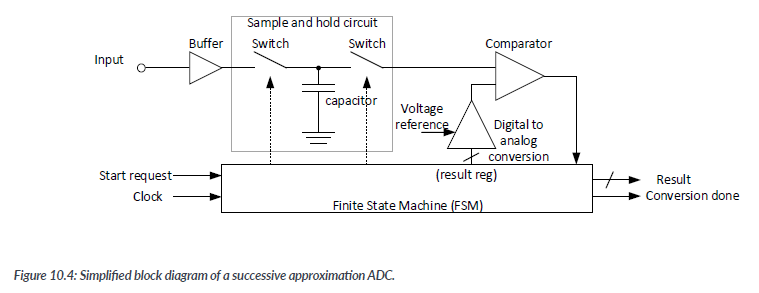

Amongst various types of ADC, sucessive approximation ADCs are very popular in microcontrollers.

Successive appriximation contains several pars, as hown in the diagram below:

With a 14-bit ADC, the FSM iterates the operation loop 14times. While it is not the fastest typeof ADC, the conversion speed is acceptable for most applications and delivers relatively high accuracy.

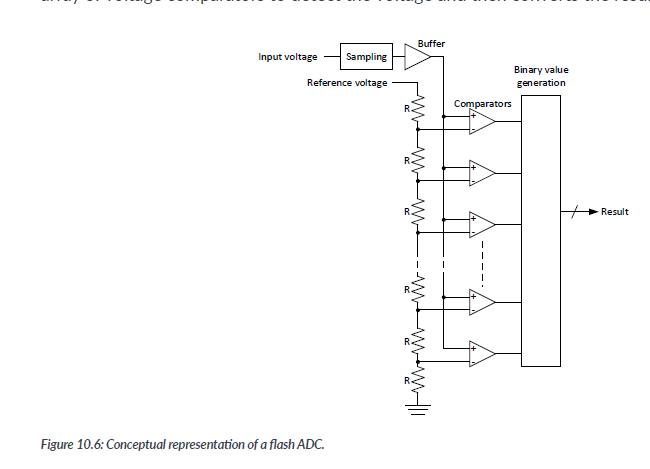

For designs that require very fast conversion speed, a flash ADC can be used. A flash ADC uses an array of voltage comparators to detect the voltage and then converts the results to binary values.

In ASIC designm the resistor network is likely to be replaced by switching capacitor networks as the implementation of resistos in ICs can be challenging in terms of accuracy.

IC에서 저항기를 정확하게 구현하는 것은 도전적인 과제일 수 있으므로, 스위칭 캐패시터 네트워크는 ADC의 정확도 측면에서 원하는 기능과 정확도를 달성하는 대안적인 솔루션을 제공합니다.Due to their nature, flash ADCs are usually larger in silicon area, power-hungry, and can offer only limited resolution. They are commonly used for video signal processing because other ADC methos cannot reach the required speed, and 8 bit is sufficient for video processing needs

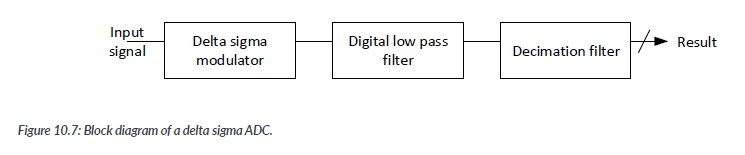

For audio processing, a delta-signal ADC could be used. Delta-sigma ADCs contains several stages;

namely;

A delta sigma modulator;

Digital low pass filter;

Decimation filter.

For audio processing, a delta-sigma ADC could be used. Delta-sigma ADCs contains several stages;

namely:

A delta sigma modulator;

Digital low pass filter;

Decimation filter.

The delta-signma modulator runs at severals MHz and can generate a bitstream with a feedback loop. the 1-bit DAC in the feedack is simply a switch that switches between +Vref and -Vref based on the result of the 1-bit ADC input. The differential amplifier compares the input signal with the 1-bit ADC, adn the integrator works as a low pass filter of the result.

with a delta-sigma ADC, the output is based on the density of ones in the output stream. Due to its nature that high-frequency input will suffer higher quantization errors. For audio processing.this is less of an issus as the human ear is less sensitive to higher frequency sounds, so we can apply a low pass filter to suppress quantization noises.

since the output is in the form of a bit stream, the application code cannot use this result directly. With a decimation filter, we can convert the bitstram information into multi bit binary values at a lower sampling rate.

The unusable bandwidth of a delta-signa ADC is a bit lower than the other ADCs mentioned previously.

In addition, delta-sigma ADCs are designed to be used with periodic sampling, whereas successive approximation and flash ADC can be turned on and off at any time to skip sample when it is not needed or perform conversions on an ad-hoc basis.

For applications where the sampling rate is very low, for example, in smart sensors when measurement might be needed only for a few times a second, or even a sample every hour, we can use a slowe ADC liket a dual slop ADC.

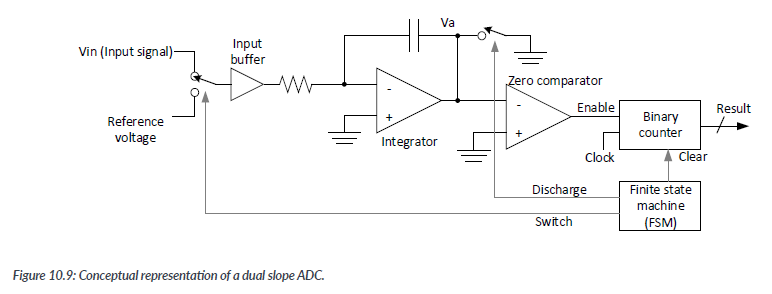

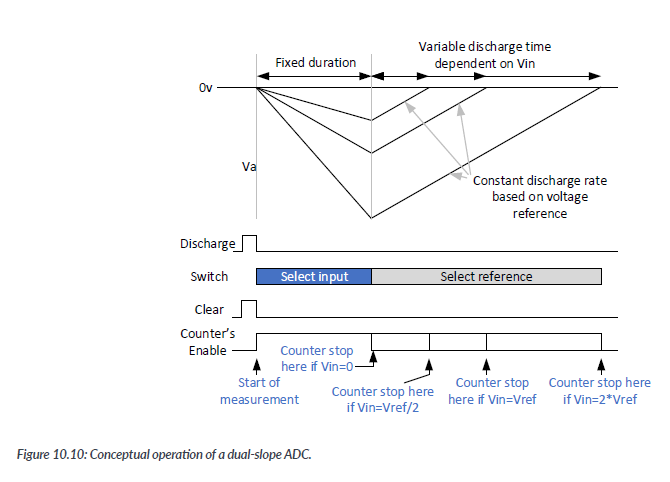

델타-시그마 ADC의 출력이 비트스트림 형태로 되어 있기 때문에 애플리케이션 코드에서 이 결과를 직접적으로 사용할 수는 없습니다. 디시메이션 필터를 사용하여 비트스트림 정보를 낮은 샘플링 속도에서 다중 비트 이진값으로 변환할 수 있습니다.Conceptually, dual slope ADCs can be implemented using an op-amp, a voltage comparator, a binary counter, and state machine, as illustrated in the diagram below:

When in operation, a dual-slope ADC applies the input voltage to an integrator circuit and integrates the voltage for a fixed duration. A reference voltage of opposite polarity is then applied to the integrator and allowed to ramp until the integrator output returns to zero.

듀얼-슬로프 ADC는 동작 중에 입력 전압을 인테그레이터 회로에 적용하여 일정 기간 동안 전압을 적분합니다. The input voltage can then be calculated as a function of the reference voltage, the fixed length period and the measured discharge peiod; which is expresses as follows:

Vin = Vref*(discharge time / fixed_charge_time)

그런 다음, 반대 극성의 참조 전압이 인테그레이터에 적용되고 인테그레이터 출력이 다시 0으로 돌아올 때까지 램프 역할을 수행합니다. 그런 다음, 입력 전압은 참조 전압, 고정 기간 및 측정 방전 기간의 함수로 계산할 수 있습니다. 이는 다음과 같이 표현됩니다:

Vin = Vref * (방전 시간 / 고정 충전 시간)Longer integration times permit higher resolution measurements, and this kind of ADC is particularly suited for very accurate measurement of slowly carying signals.

10.3.3 Digital to analog conversions

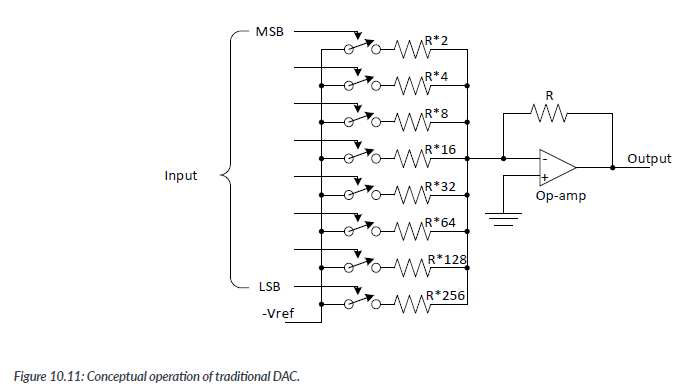

There are various ways to convert digital values into analog signals. Traditional DACs might use a combination of amplifier and resitor network to obtain analog outpus, as shown in the diagram below :

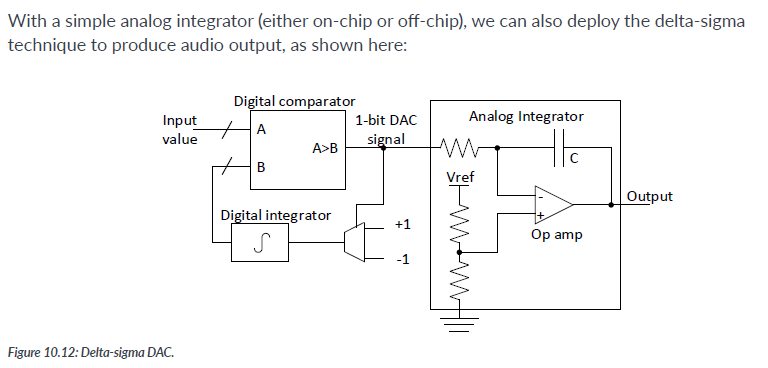

In some cases, when the quality of the output is not critical, we could consider simpler mechanisms for analog output. For example, a simple PWM (Pulse Width Modulation) output could be used to drive a small speaker for audio tone generation.

10.3.4 Other analog interface approaches

There are several different ways to connect audio/analog interfaces t digital ICs; namely:

I2S interface - For microcontroller-based products using an external I2S audio codec IC is a common choise. I2S are digital serial interfaces and therefore can be handled as digital peripherals. They can also be implemented on FPGA develpment boards.

I2C/I3C/SPI interface - External ADC and DAC chips often use serial communication protocols such as I2C/I3C or SPI. Such an arrangement is suitable for sensor and control applications. I2C and SPI interface peripherals are widely acailable from various peripheral IP providers.

PDM(Pulse Density Modulation) - In recent years, digital micophnes with PDM interfaces are becoming more common due to their low cost and simple interfaces. Similar to delta-sigma, a microphone's output is in serial bitsream where the density of '1' indicates a higher analog value.

The PDM signals can be converted to analog values using digital filters and be implemented as digital peripheral interfaces.

PDM (Pulse Density Modulation)는 최근에는 저렴하고 간단한 인터페이스를 가지고 있는 디지털 마이크로폰이 더 일반적으로 사용되고 있습니다. 델타-시그마와 마찬가지로, 마이크로폰의 출력은 '1'의 밀도가 더 높은 아날로그 값을 나타내는 직렬 비트스트림 형태입니다. PDM 신호는 디지털 필터를 사용하여 아날로그 값으로 변환되고 디지털 주변 인터페이스로 구현될 수 있습니다.10.3.5 Connecting ADC and DAC IPs into a Cortex-M system

In instances where you license ADC or DAC IPs, these components usually provide simple digital interfaces. To connect them to a Cotex-M system, the typical integration task includes the following steps: