arm

1.System-on-Chip Design with Arm® Cortex®-M processors - 2

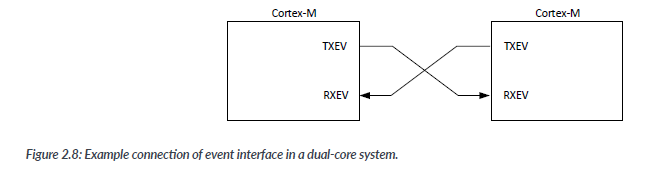

However, in many cases, a level-triggeredinterrupt is preferred because:If the interrupt event occurred when the processor is reset, the interrupt eve

2.System-on-Chip Design with Arm® Cortex®-M processors -3

The free running clock, system clock and debug clock( except the clock for the debug interface and DAP interface on Cortex M3/M4 processors) must be s

3.System-on-Chip Design with Arm® Cortex®-M processors -4

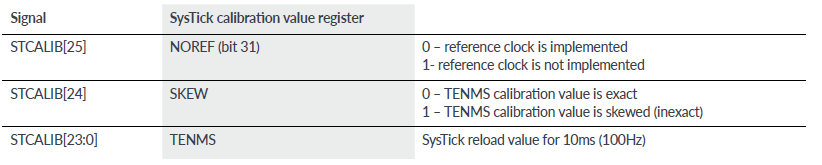

The SysTick timers in the Cortex-M processors support external reference " clock." Thechnically the reference "clock" in not a clock signal, as it is

4.System-on-Chip Design with Arm® Cortex®-M processors - 5

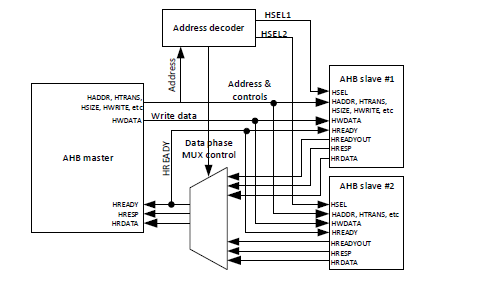

Almost all the AMBA specifications have the follwing characterisic:Synchronous operations - use only clock rising edge for flip-flops, friendly to com

5.System-on-Chip Design with Arm® Cortex®-M processors - 6

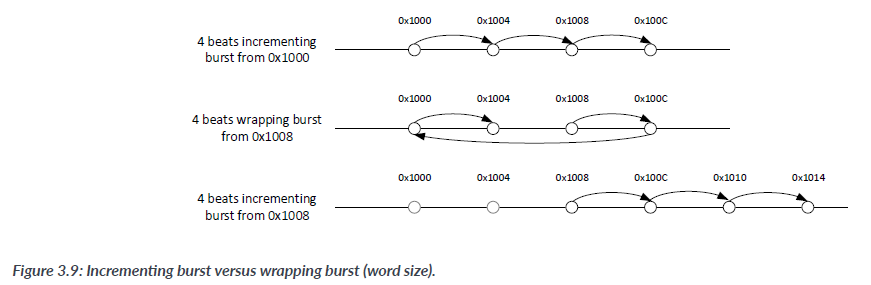

In AMBA 2 AHB and AHB Lite, the HPROT signal contains 4bits, each of them has a different function:When accessing to normal memories(not peripherals),

6.System-on-Chip Design with Arm® Cortex®-M processors - 7

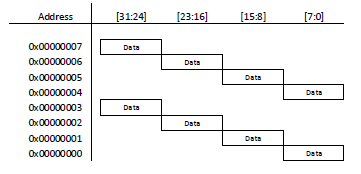

There are several AHB data phase signals. For signals from bus masters to slavesTable 3.16 : Additional AHB data phase signals from bus masters to bus

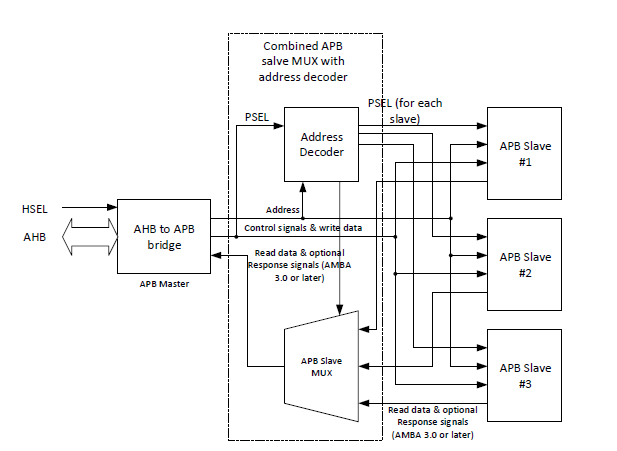

7.System-on-Chip Design with Arm® Cortex®-M processors - 8 (Overview of APB)

3.6 Overview of APB3.6.1 Introduction to the APB bus systemAPB is a simple bus mainly targeted for peripherals connections. It was introduced as part

8.System-on-Chip Design with Arm® Cortex®-M processors - 9 Building simple bus systems for Cortex-M processors

4.1 Introduction to the basics of bus designIn this chapter, we will look into the basics of bus system.there are several generla principles to be awa

9.System-on-Chip Design with Arm® Cortex®-M processors - 10

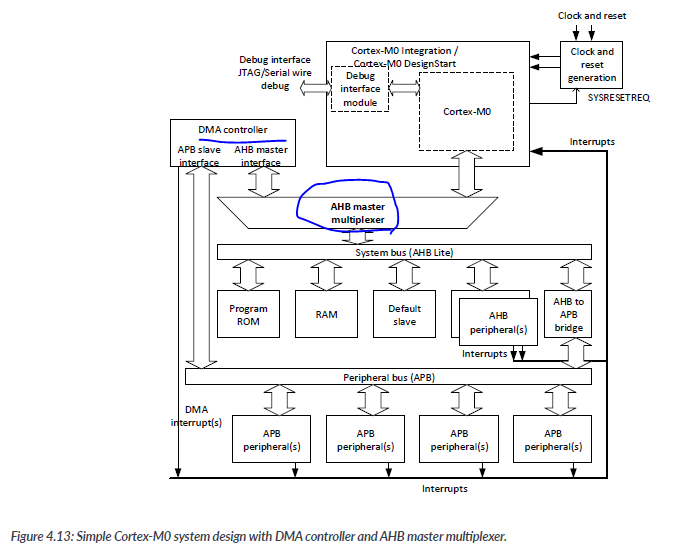

In many microcontroller systems, you can find multiple bus masters such as :Direct Memory Access (DMA) controllers;Peripherals that need high data ban

10.System-on-Chip Design with Arm® Cortex®-M processors - 11

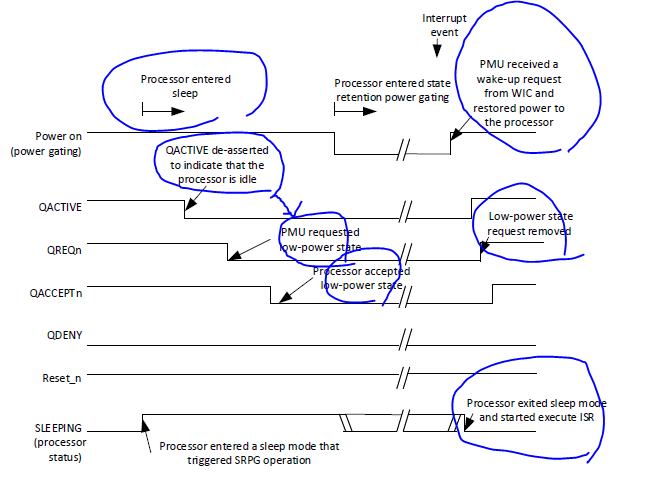

When the processor enters sleep mode, the power management unit dectects the sleep operation and then requests to change the processor to low-power st

11.System-on-Chip Design with Arm® Cortex®-M processors 12

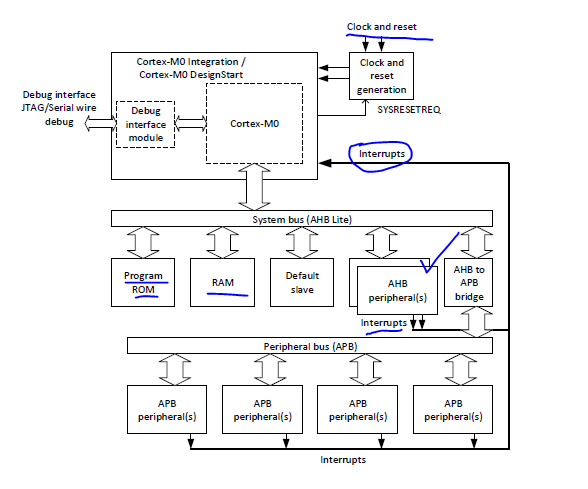

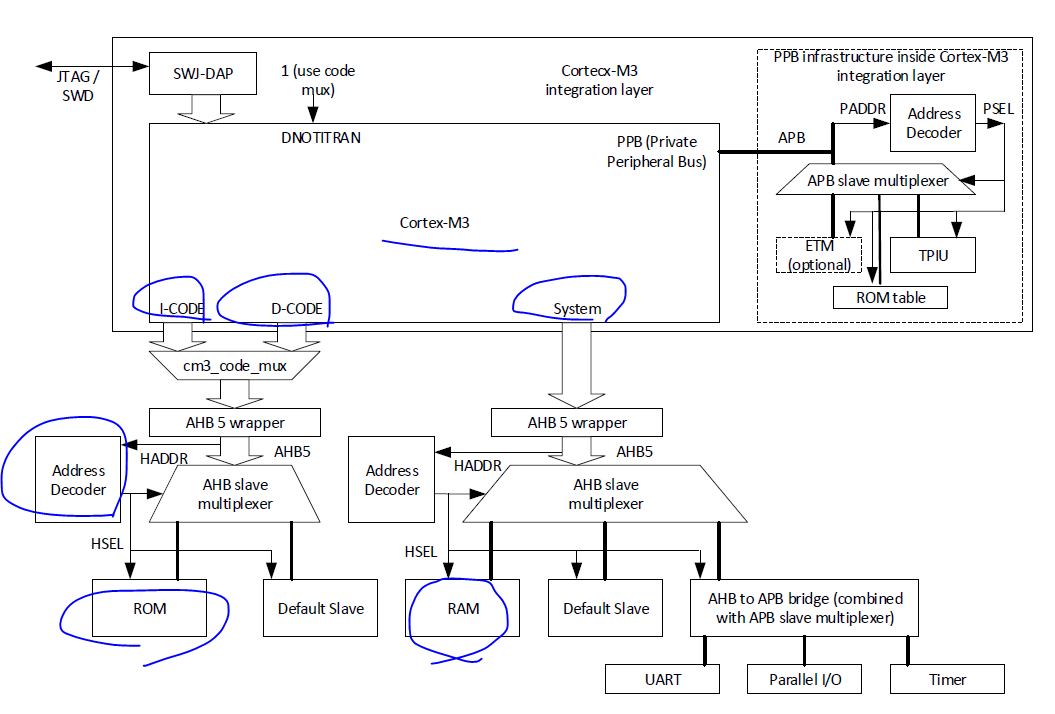

7.1 OverviewFor peripheral conncetions, APB is used in the example, and the APB bus segment is connected via an AHB to APB bridge, As explained in Sec

12.System-on-Chip Design with Arm® Cortex®-M processors - 13

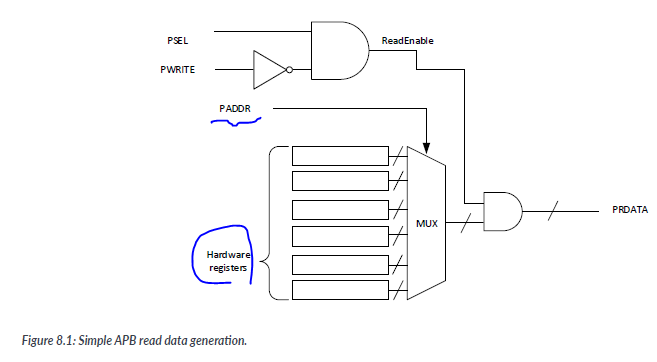

if you are designing a peripheral for a Cortex-M processor-based system or setting out to develop wrapper for legacy 8-bit or 16-bit peropheral blocks

13.System-on-Chip Design with Arm® Cortex®-M processors - 14 Putting the system together

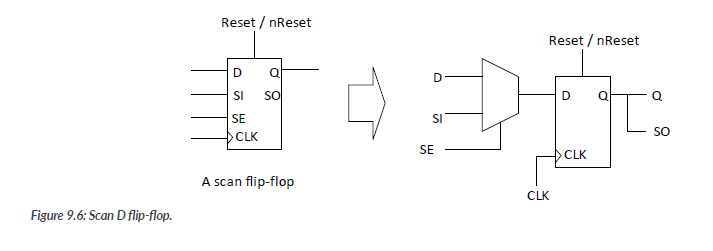

9.1 Creating a simple microcontroller-like system After designing the bus infrastructure components and peripherls, we can then put together a proces

14.System-on-Chip Design with Arm® Cortex®-M processors -15

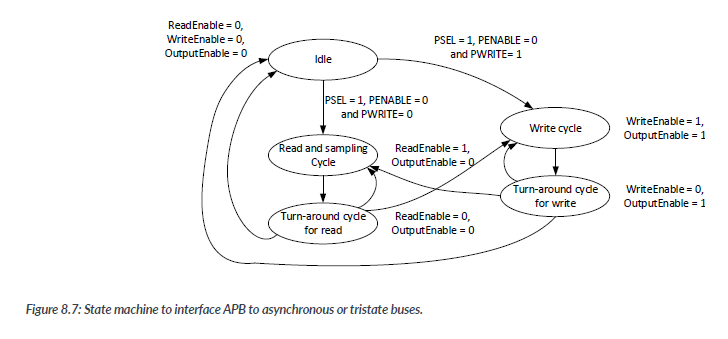

However, if the peripheral requires a tristate bus interface, or uses an asynchronous interface, the wrapper will have to handle the transfers in mult

15.System-on-Chip Design with Arm® Cortex®-M processors - 16 Chapter 10 - Beyond the processor system

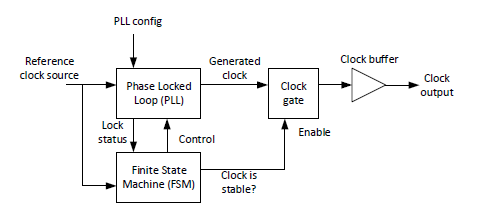

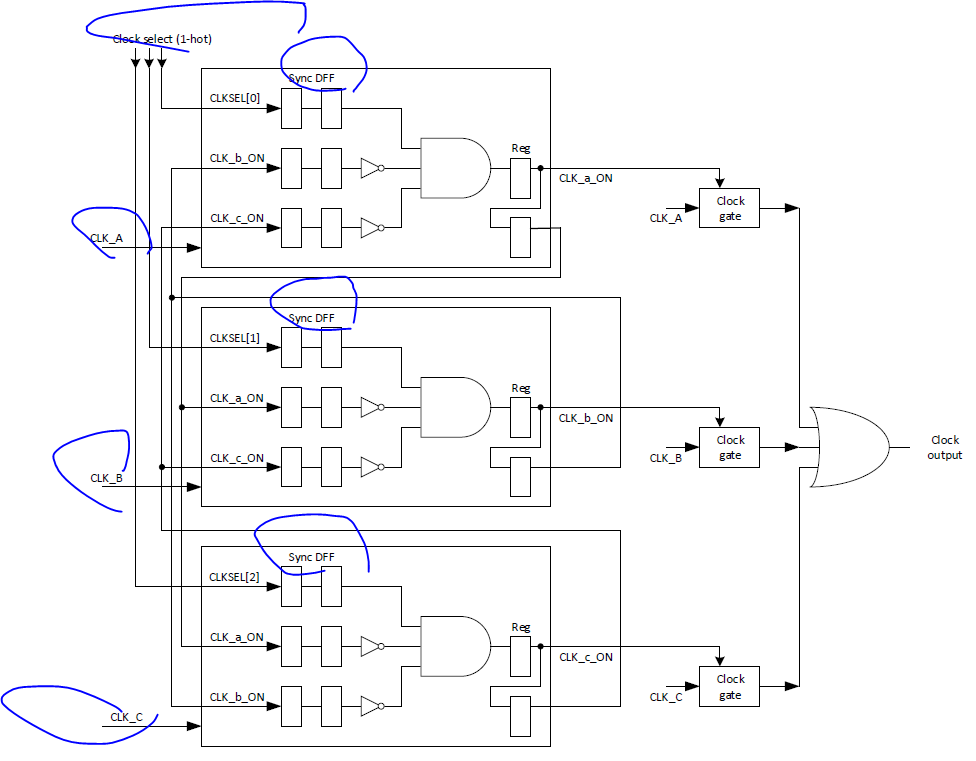

10.1 Clock system design10.1.1 Clock system design overviewAll processor systems need clock signals to operate.For the majority of microcontroller sys

16.System-on-Chip Design with Arm® Cortex®-M processors - 17

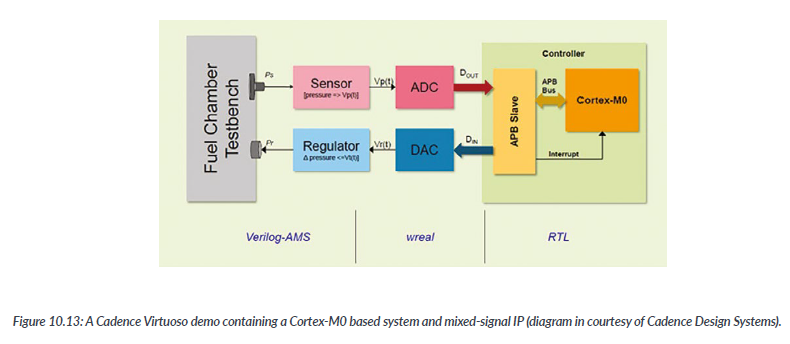

10.3.5 Connecting ADC and DAC IPs into a Cortex-M system.In instances where you license ADC or DAC IPs, these components usually procide simple digita