2.9 Interrupt signals and related areas

However, in many cases, a level-triggered

interrupt is preferred because:

-

If the interrupt event occurred when the processor is reset, the interrupt evetn could be lost.

-

Level Trigger interrupts can remain at a high level to indicate and additional service is needed by the pripheral(e.g, when additional data is available in a receiver's FIFO).

-

Easier for debugging (e.g, in Verilog Simulation, where it is hard to tell if there has been an interrupt event unless the event information is kept by, for example, a wavefirn database).

-

The peripheral design can be reused for other processors that do not support pulsed trigger interrupts.

In addition to the number of interrupt, there are other configuration options related to interrupt handling:

Number of interrupt priority levels - In Armv7 - M and Armv8 - M Mainline processors, the programmable interrupt priority level registers has configurable width from 3-bits to 8-bits. Typically, the options of 3-bit to 4-bit are used, and some devices do support 5-bit. Most applications do not need many interrupt priority levels, so eight levels(3-bit) is likely to be sufficient.

-> 인터럽트는 보통 3 bit 로 우선 순위를 나눈다 즉 8개 레벨

Wakeup Interrupt Controller (WIC) - An optional block to handle interrupt detection while the processor is in-state retention power gating (SRPG) or when the processor's clock is completely stopped. if the WIC feature is implemented and enalbled, the interrupt masking information is transferred from NVIC to WIC automatically before entering sleep mode. The WIC then takes over the role of interrupt event detection and can generate a wakeup request to power management blocks in the system when an enabled interrupt event is detected. The interrupt pending status is held in the WIC when the processor is waking up and transfers the interrupt request to NVIC when the processor is back up. At the same time, the masking information inside the WIC is cleared automatically by hardware as the NVIC is back running.

2.10 Event interface

Apart from the Cortex-M1 Processor, all other Cortex-M processors have and event input(typically named RXEV - receive event) and an event output(typically named TXEV - transmit event). The RXEV input is used to wake up a processor from Wait-For-Event(WFE) Sleep operation,

-> 다른 Processor 들을 깨울때 쓴다.

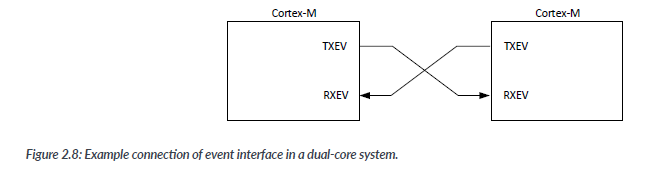

The event interface is typically used in multi-core systems to allow one processor to wake up another during spinlocks. In RTOS semaphores, if a processor is waiting for a spinlock, it can enter sleep mode using WFE to save power and wakes up if there is an interrupt to serve or if there is an event from another processor. By crossing over the event interface signal,

processors in a dual core system can wake up each other from WFE sleeps using the SEV(send event) intruction.

Events could also be generated from periherals or DMA controller, but normally interrupts are more suitable for that purporse as we need software to react to those hardware events vis ISRs.

For single-processor systems, it is fine to tie RXEV to 0 and leave TXEV unconcected.

-> single processor 면 RXEV 0으로 TXEV은 오픈해놓는다.

Please note:

The event interface on ther Cortex-M processor is unrelated to the definition of events in RTOS.

In RTOS, an application thread waiting for a certain operation X to be carried out can call an OS API that waits for an event Y.

This API call also takes the thread out of the ready task queue. When the specified operation X has been carried out(e.g., in another thread or an ISR), the other thread or ISR that carried out the operation X can call another OS API to set the OS event Y. This puts all the waiting threads that were waiting for the operation X to be put back in the ready task queue to resume operation.

2.11 Clock Generation

There are several clock signals on ther Cortex-M processors. Over the years there have been differnt design approacheds and therefore the clock and reset signal names vary between different processors.

Most of the existing Cortex-M processors provides:

Free-running clock (if gated, all logic in ther processor stopped and needs external logic blocks such as WIC to handle interrupt detection and wakeup);

system clock(can be gated during sleep mode);