2.11 Clock generation

The free running clock, system clock and debug clock( except the clock for the debug interface and DAP interface on Cortex M3/M4 processors) must be synchronmous and in the same phase. The separation of clock signals is to allow the system power to be reduced by gating off some of the clock signals when they are not needed.

-> system clock 하고 debug clock 은 같은 Phase 를 가져야 한다.

-

In Cortex-M0 and Cortex-M3 processors, the design exported GATEHCLK signal is asserted when the processor is in sleep mode, and there is no debug connection. This signal can be used to gate off the system clock.

-

In some of the Cortex-M processors, the clock gating logic is done internally and so might not have all these clock signals visible on the top-level.

-> Cortex-M0 및 Cortex-M3 프로세서에서 GATEHCLK 신호가 sleep 모드일 때, 디버그 연결이 없을 때 활성화되며, 이 신호를 사용하여 시스템 클럭을 차단할 수 있다는 것을 나타냅니다.

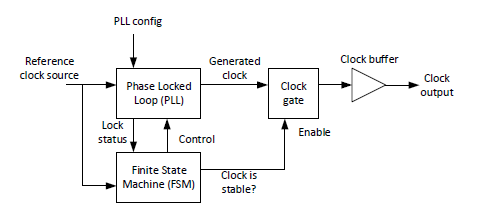

It is important not to gate off the system clock when the processor is running. In system-level designs,there can be multiple clock sources, and a glitch-less clock switching curcuit would be needed. The clock switching circuit is outside of the processor and is normally application and process node dependent. In FPGA designs, you can design an FSM that controls the PLLs (Phase-Locked Loops) and gate-off the clock signals to the processor

Depending on the FPGA design tool being used, the system clock generation/control logic might be generated by the tools. In this case, there is no need to develop your own clock generation / control logic.

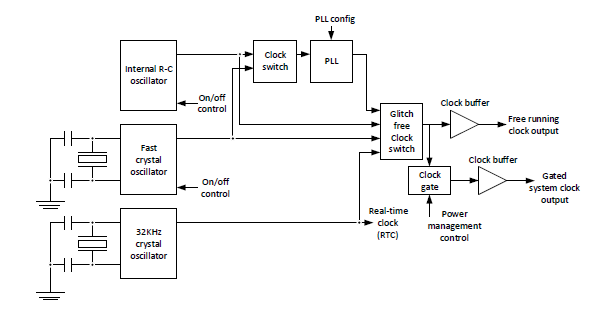

In ASIC designs, you might have the following clock sources:

External crytal oscilator for medium speed(e.g, 1Mhz to 12Mhz) - this might be turned off by default after a reset to save power. Instead of using a higher frequency crystal to generate higher frequency clocks,it is more common to use a PLL to generate a high clock speed when needed to avoid having a high-frequecny clock running all the time to save power.

Internal RC oscillator for medium speed. This will use less power than a rytal oscillator, but will not provide an accurate frequency reference for timing or peripheral interfaces.

External 32KHz oscillator for real-time clock(might also be used for system management)

In ASIC/SoC implementations, the system can boot-up from the internal RC oscilator and switch over to external crystal oscilator or PLL for clock source when needed. PLL can provide higer clock frequency for high-performance operations.

2.12 Reset generation

In the Cortex-M processors there are usually at least two reset signals, in some cases three signals:

System reset;

Debug reset;

Debug interface reset(e.g., nTRST) for JTAG interface;

Optionally you might find a power on reset, which resets both the system and debug logic.

If power-on-reset is present, it resets both the system and debug system. The reason that we separate the reset into two signals is to allow the processor to be reset without affecting the debug system.

Otherwise, the debug settings like breakpoints, watchpointsm and the debug connection from the debugger to the core, would be lost each time the processor core is reset.

-> 전원 리셋 신호가 존재하면, 이 신호는 시스템과 디버그 시스템 모두를 재설정합니다. 이를 통해 시스템 전체가 안정적으로 시작되고, 디버그 설정이 재설정되어 디버그 작업을 계속할 수 있습니다.

그러나 시스템 리셋과 디버그 리셋을 분리하는 이유는, 디버그 시스템에 영향을 미치지 않으면서 시스템만 재설정할 수 있도록 하는 것입니다. 이를 통해 시스템이 재설정되면서 디버그 설정이 손실되지 않고, 디버그 작업을 계속할 수 있습니다.

따라서, 시스템 리셋과 디버그 리셋을 분리하여 사용함으로써 안정적이고 신뢰성 있는 전자 제품을 설계할 수 있습니다. 이를 통해 시스템의 안정성과 신뢰성을 보장하면서 디버그 작업을 지속할 수 있습니다.

The processor also outputs a reset request signal called SYSRESETREQ. This is controll by a register bit in the Application Interrupt and Reset Contorol Register inside System Control Space. This allows:

Software to requeset a system reset, for example, in the case of fault error handling;

Debugger to request a system reset. This is essential to allow the debugger to request a reset of the targeted processor.

Designers must make sure that :

SYSRESETREQ only generates a system reset but not debug reset or power-on reset;

SYSRESETREQ does not generate a system reset in a combinatiorial path(in other words - it must be registered by registers that are not affected by the system reset), as the SYSRESETREQ output is affected by a system reset and the use of a combinatiorial path for reset eneration cause a reset glitch

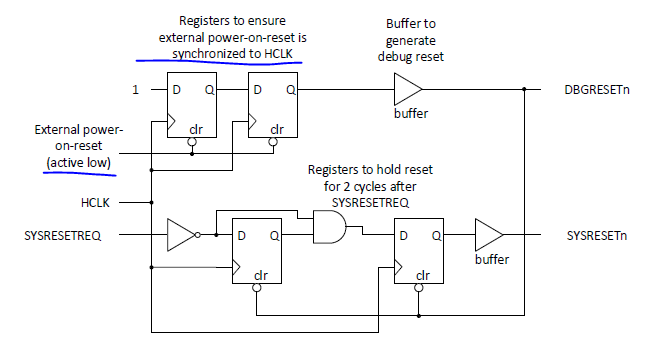

All of the Cortex-M processors use an asynchronous active-low rset signal and must be de-asserted synchronously to the system and debug clock to prevent timing violations. This ensures that most of the registers can be reset when the clock is not running. However, most of ther Cortex-M processorss require the reset to last at least two clock cycles. This arrangement has the following benefits:

-

Enables synchronization flip-flops, which present in double DFF synchronizers to be reset.

-

In the case where the assertion of reset causes timing violations and leads to mestability, the multi-cycle natrue of reset ensures the metastabuility is cleared up. To ensure reset de-assert occurs at the correct time, a simple reset generator could be used for a Cortex-M0/M0+/M1/M3/M4 processor. Figure 2.11 shows such an example.

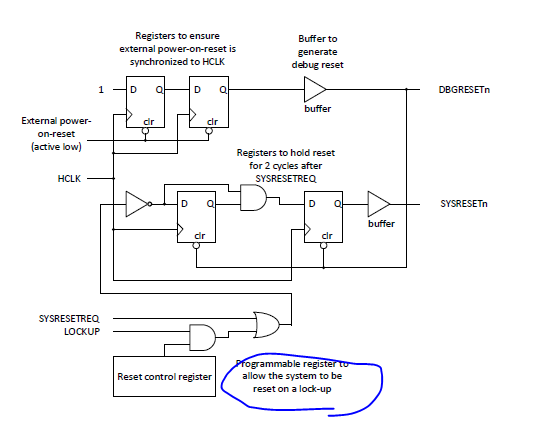

Assuming the Cortex-M1 is used(some other Cortex- M processors have different signal names for reset signals): The Cortex-M1 processor generates the SYSRESETREQ signal. Since the Cortex-M1 processor can be reset by SYSRESETn, the SYSRSETREQ siganl must not drive SYSrESETn in a comninatorial path. Otherwise, it could result in a race condition where SYSRESEREQ gets clearedin a very short time after assert, as it gets cleared by its output. This could result in a race condition where SYSRESETREQ gets cleared in a very shor time after assert, as it gets cleared by its output . This could result in some parts of the processor getting reset and other parts not. For this reson, The SYSRESETREQ signal must be registered by a separated flip-flop that is not affected by SYSRESETn before being used to generate SYSRESETn. In the example above, the reset request from the SYSRESETREQ is held in two registers that are reset by DBGRESETm, or if using Cortex-M3/M4, you can use power on reset in Cortex-M3/M4 processor.

-> SYSRESETREQ 신호는 SYSRESETn을 생성하기 전에 SYSRESETn에 영향을 받지 않는 별도의 플립플롭으로 등록되어야 합니다.

We can also design the reset generator so that it can optionally reset the system if it enters lock-up state. To make this behavior controllable, a programmable register would be needed in your FPGA/system design to specify if a lock-up state can cause a reset. This register is not provided in ther Cortex -M processor core as such requirement is application dependent.

During software development, the control signal at his external reset control reguster can be set to 0 to disable the automatic reset.

In a production system, the reset control register can be set to 1 so that when the system enters lock-up state, the SYSRESETn is activated automatically.

-> 리셋 생성기(reset generator)를 설계하여 시스템이 잠깐 멈추는 lock-up 상태일 때 선택적으로 시스템을 리셋할 수도 있다는 것을 나타냅니다. 이러한 동작을 제어하기 위해, FPGA/시스템 설계에서 프로그래머블 레지스터가 필요합니다. 이 레지스터를 사용하여 lock-up 상태가 리셋을 유발할 수 있는지 여부를 지정할 수 있습니다. 이러한 레지스터는 Cortex-M 프로세서 코어에서 제공되지 않으며, 응용 프로그램에 따라 필요할 수 있습니다.

Depending on the FPGA desing tool begin used, the system reset controller might already be included. in this case, there is no need to develop your own reset controller.