9. Debugging Constraint Issues

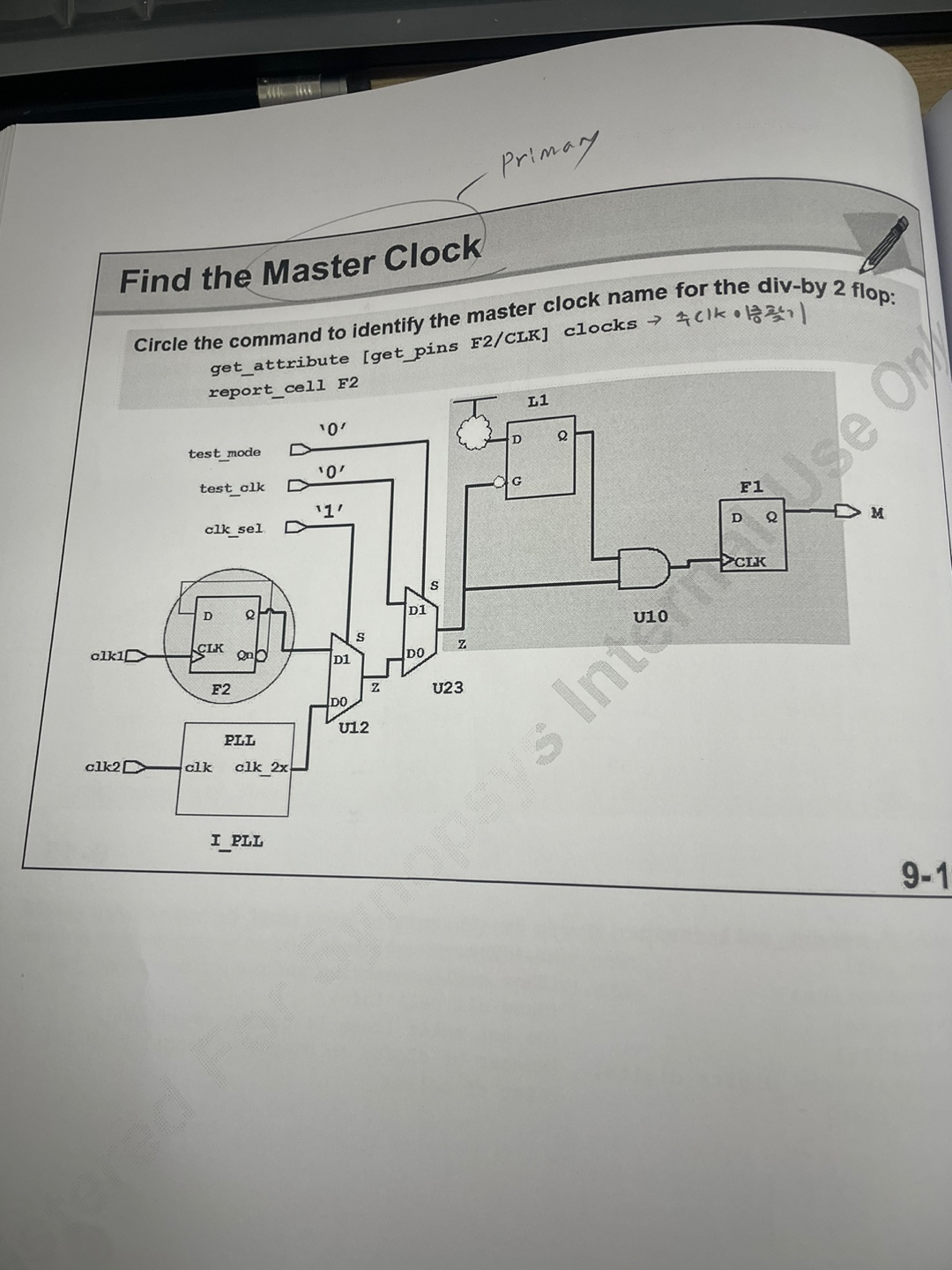

9.16.17) Master Clock(Primary) 찾기

get_attribute [get_pins F2/CLK] clocks

report_cell F2

제약조건에서 Master Clock이 중요함

위의 2가지 command로 Master Clock 이름을 알 수 있음 >> 9-17

9.19) Disabled Arcs 확인하기

report_disable_timing [all_fanin -only_cells -to F1/CLK -flat]

report_disable_timing [all_fanin -only_cells -to F1/CLK -flat]

합성 STA는 async 선언 안 하면 무조건 sync로 해석

위의 2가지 command는 Timing disable를 찾을 수 있음

9.20) 리포트 확인하기

9.21)

report_case_propagation [get_pins U23/s]

all_fanin -flat -to U23/S -startpoints

9.22) How Does report_case_propagation Work?

report_case_propagation I_Clock_GEN/U21/S1

: 다른 사람이 설정한 거 확인하는 command

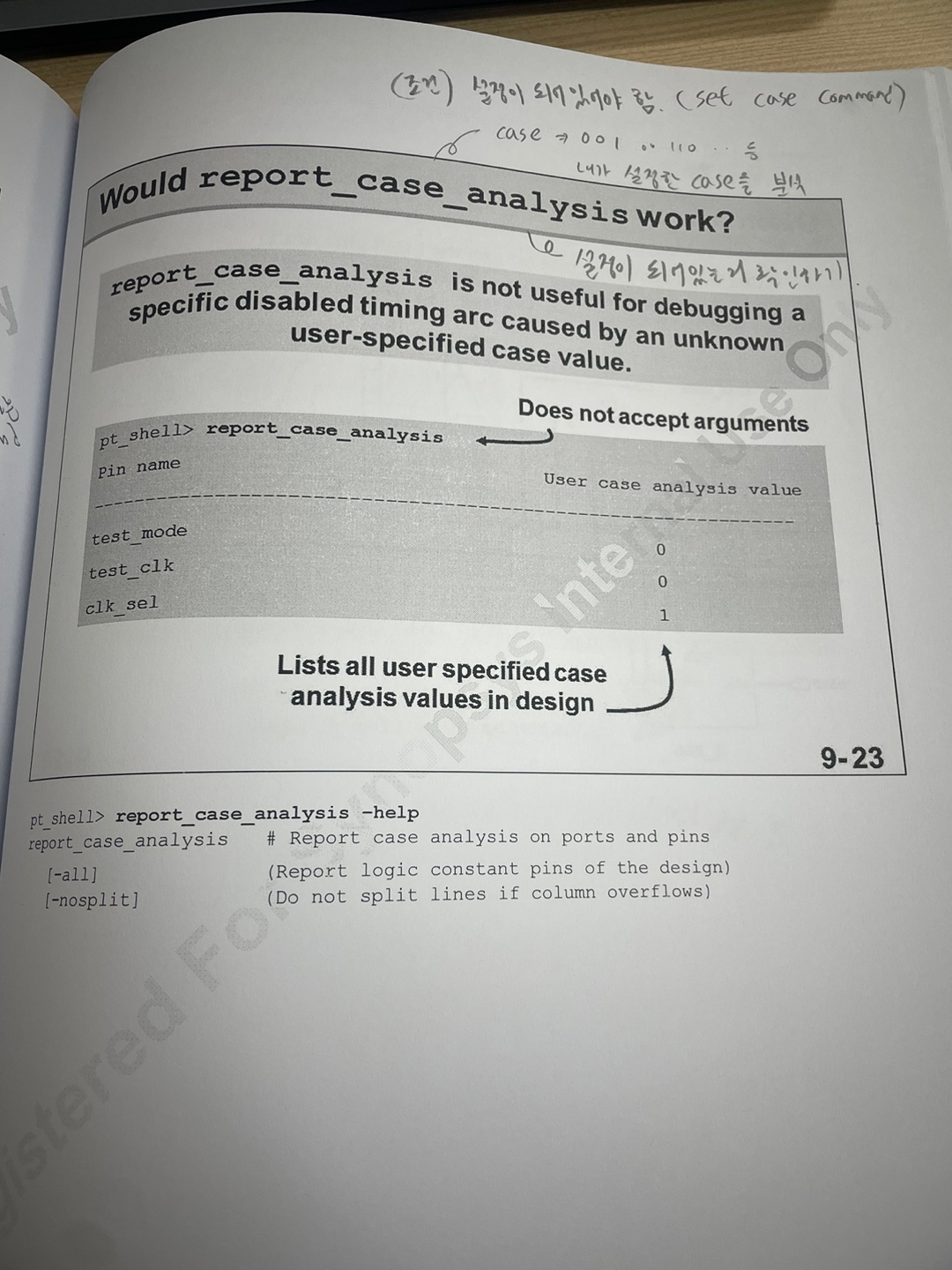

9.23) Would report_case_analysis work?

report_case_analysis

: 직접 설정해준 0,1,1 분석하여 확인

그전에 설정값은 설계자가 직접 넣어줘야 함

9.24) Dismiss Clock Gating Logic

report_case_propagation F1/CLK

all_fanin -start -flat -to F1/CLK

9.25) Sketch a Schematic

report_cell -connections -verbose L1

:L1 연결 pin , net 찾기

9.26) Expand Sketch One Level at a time

report_cell -connections -verbose [all_fanout -levels 1 -flat -only -from L1/Q]

:Gate Clock의 Cell 찾기

9.27) How Does all_fanout Work?

all_fanout -flat -endpoints -from L1/Q

all_fanout -help

: Fan_out 찾기

9.29) Useful Commands

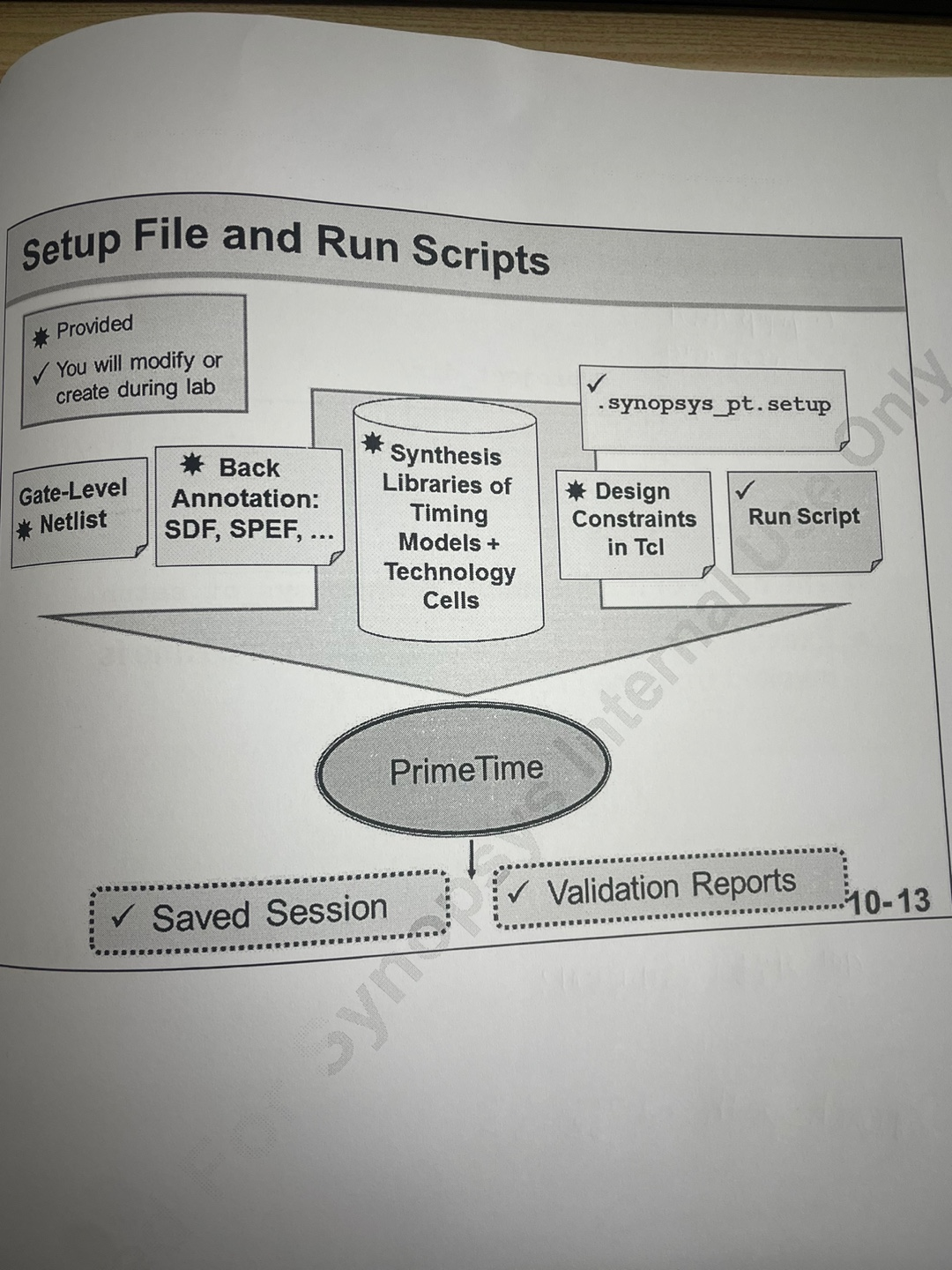

10. Timing Analysis Flow

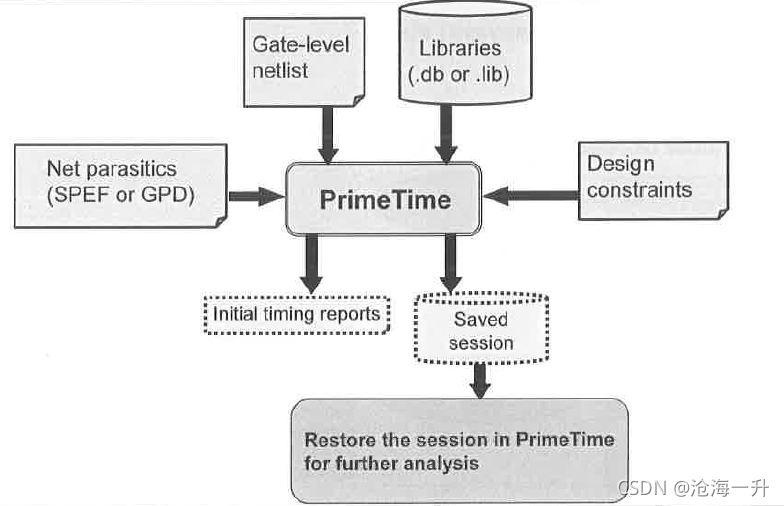

10.5) Timing Analysis Flow in Prime_Time

Timing Analysis Flow

1. Load Design, Libraries : 여기서 Design은 합성 or P&R

2. Read Parasitics(LC 값) >> 중요함 // 이유) 지금 공정에서는 net-delay가 중요

3. Source Timing Constraints

4. [Update Timing] Generate Reports & Analyze

안에서 loop(save session > restore session)

5. Signoff & Celebrate

Design 확인하기

current_design : 현재 디자인 이름 출력

list_designs : 어떤 디자인이 있는지 출력

'*' 현재 디자인

'L' 디자인과 연결된 것

'N' 메모리에 없는 디자인

'I' 디자인이 부분적으로 연결되어져있는 것

Design이 사용하는 Libraries 확인하기

printvar search_path : 디렉토리 경로 리스트

printvar link_path : 라이브러리 파일 리스트

list_libraries : PT에 로드된 라이브러리 >> '*' Main Library 표현

report_lib : library report

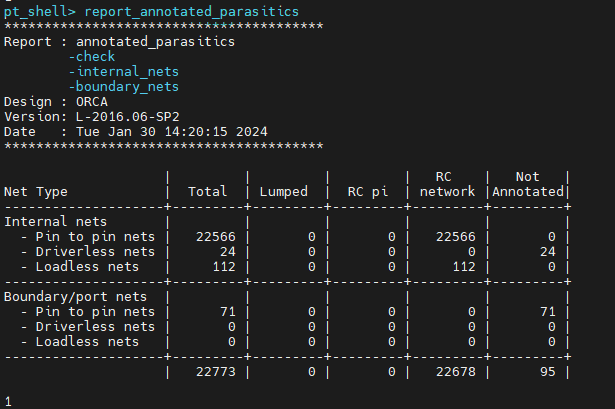

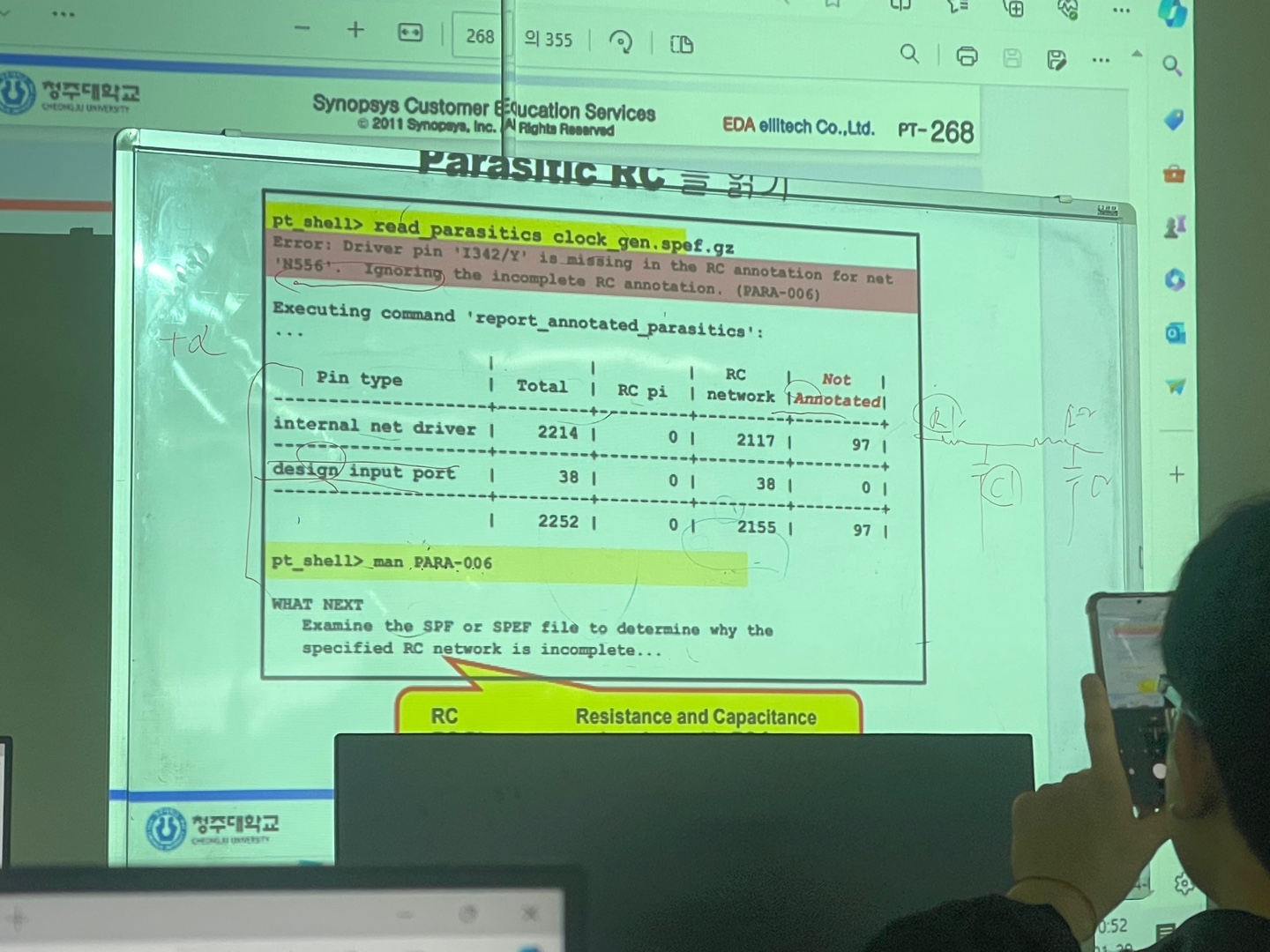

Parasitics (RC값) 확인하기

report_annotated_parasitics : RC값 리포트

여기서 not annotated는 RC값 확인이 불가

annotated : 주석을 달다

즉, 주석을 달 수 없다고 이해하면 됨

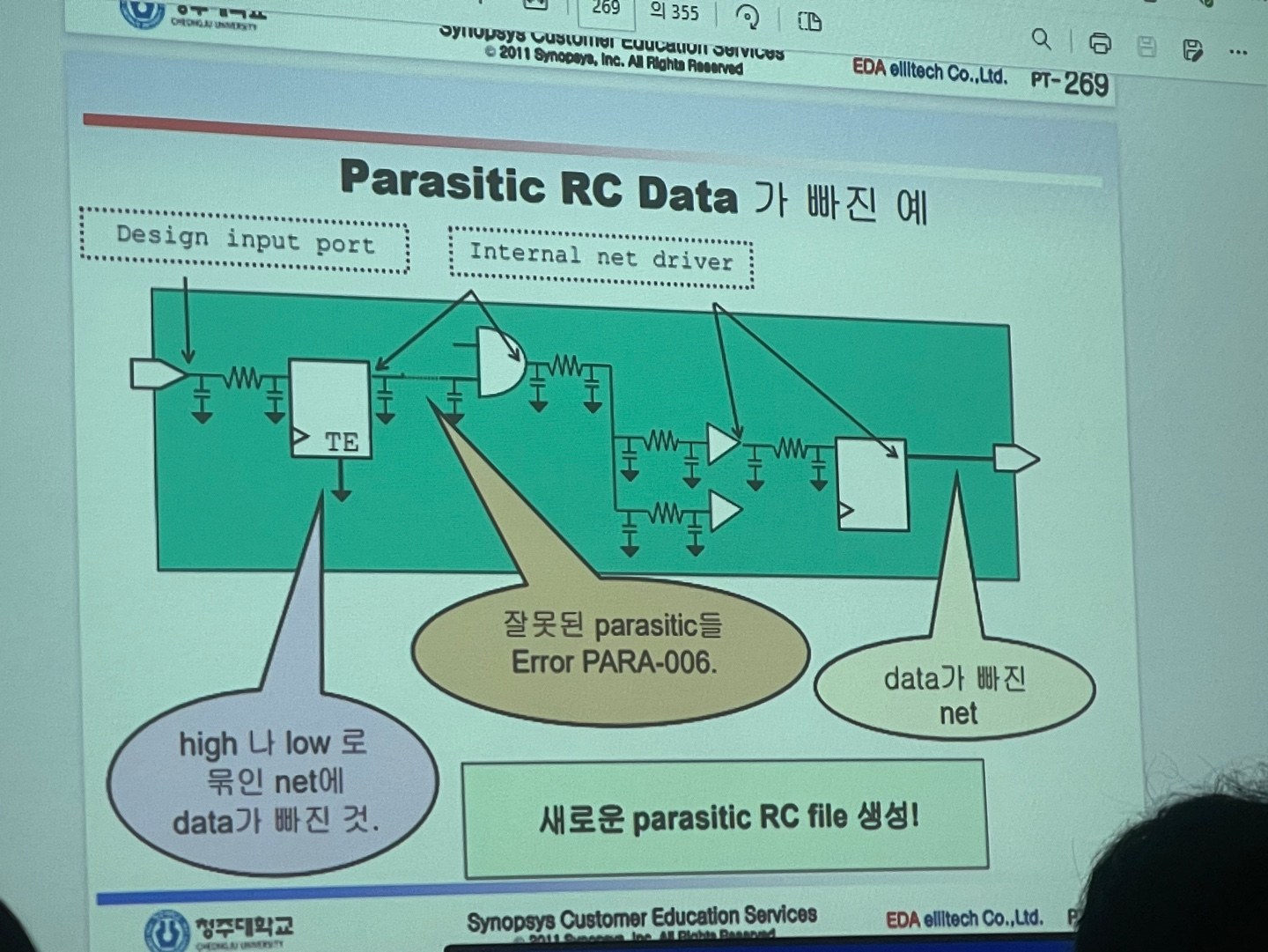

RC Data가 빠진 경우

선이 끊어짐

하이랑 로우가 묶여있음

data가 빠진 net

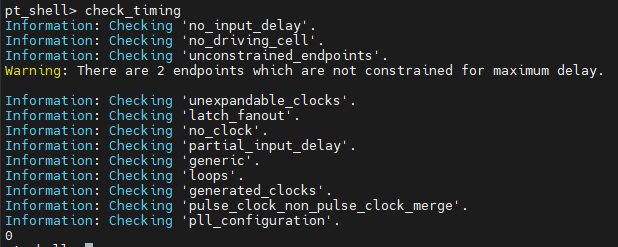

Constraint 파일 확인하기

check_timing

여기서는 설계자가 설정해야할 set out이 빠짐

Ignored Timing Exceptions 확인하기

report_exceptions -ignored

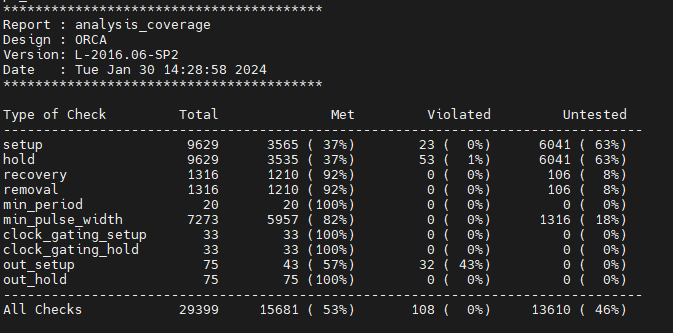

Coverage Analysis

report_analysis_coverage

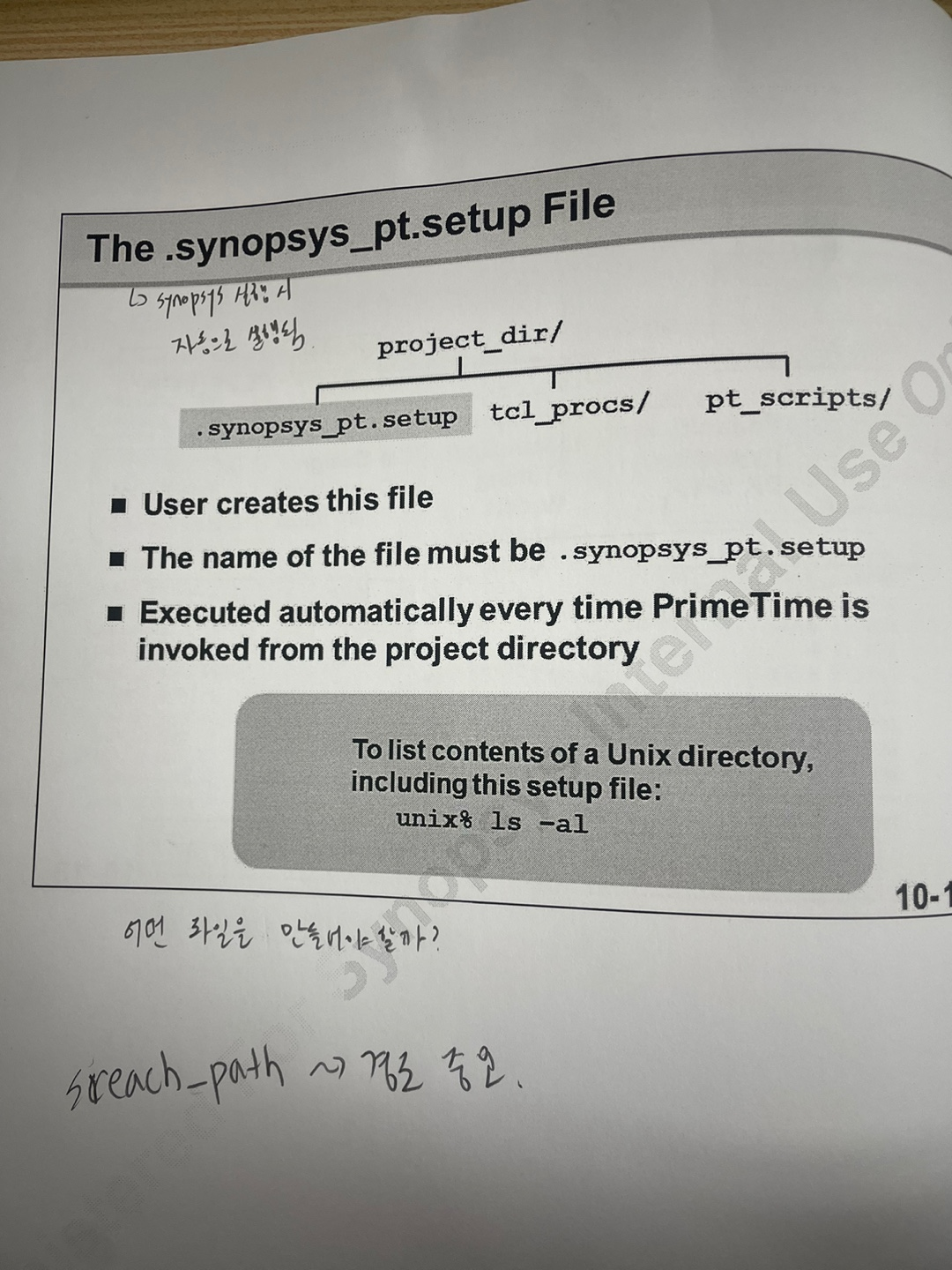

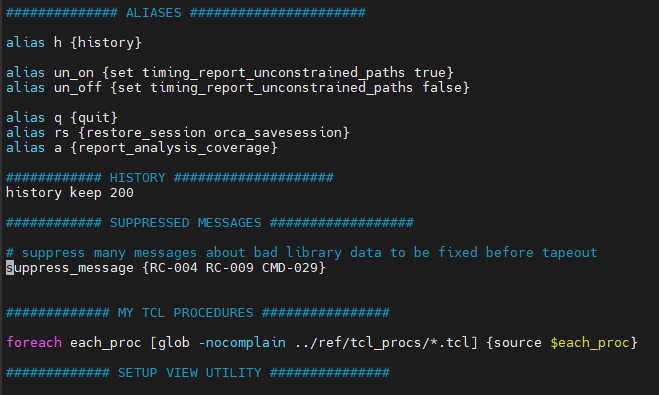

Setup File and Run Scripts

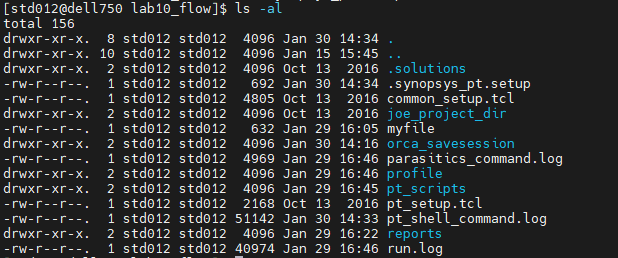

ls -al

lab 10에 있는 파일들을 확인할 수 있음

vi .synopsys_pt.setup

에디터를 이용하여 내부 파일을 볼 수 있음

+alias를 이용하여 command(report_analysis_coverage) 를 단축키 a로 변경

+tcl은 스크립트 파일임

RM FILES

common_setup.tcl : DC, PT, ICC에서 사용 가능

pt_setup.tcl : PT에서 사용 가능

./pt_scripts/pt.tcl : pt에서 사용 가능하고 내가 짜놓은 명령어로 검사 가능

실제 실무에서는 read verilog로 netlist파일을 가져와서 읽고 pt.tcl로 반복하여 pt.tcl안에 명령어 수정하여 반복 검사함.

-f run.tcl | tee -i run.log : run이라는 파일을 실행 동시에 결과를 저장하라는 cmd

Save the PT Session

PT는 디렉토리로 저장

다른 버전의 PT는 다른 버전 PT TOOL로 읽지 못해서 실무에선 컴퓨터에 저장됨