lab7

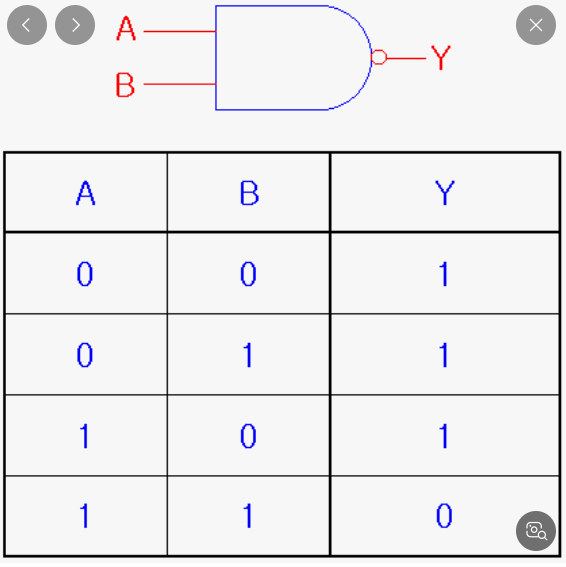

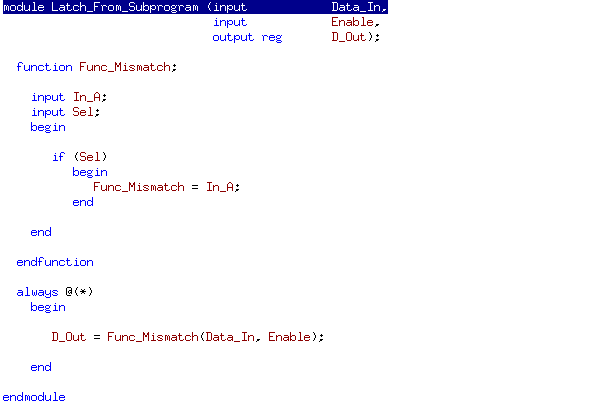

- lab7 simulation과 synthesis의 불일치가 일어나는 지 확인

lab8

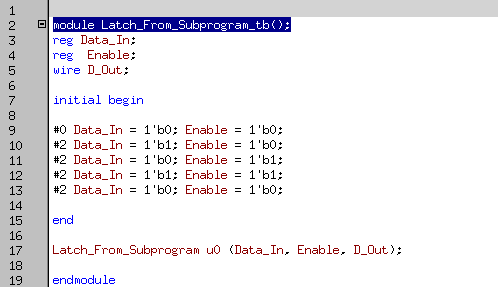

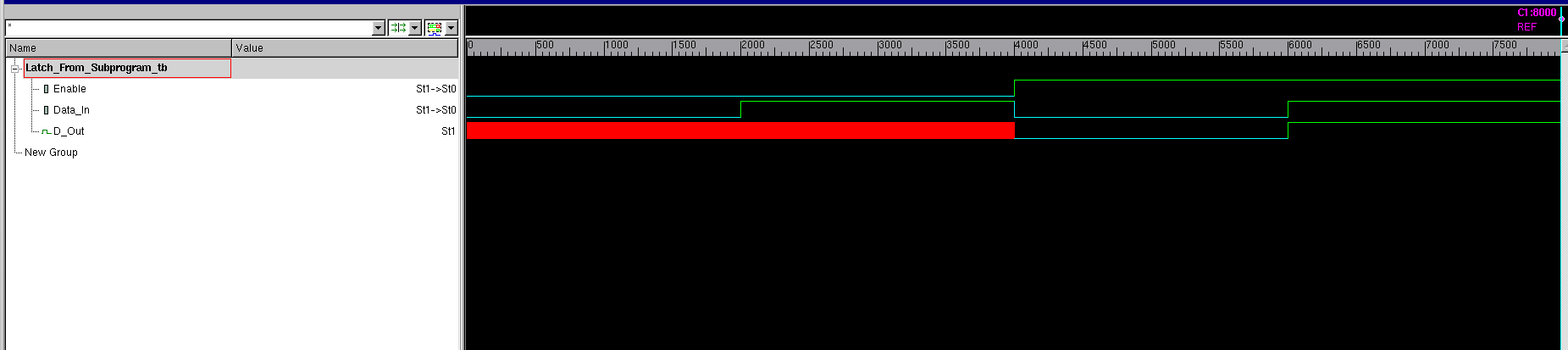

- lab8 simulation과 synthesis의 불일치가 일어나는 지 확인

lab 7,8 차이 비교

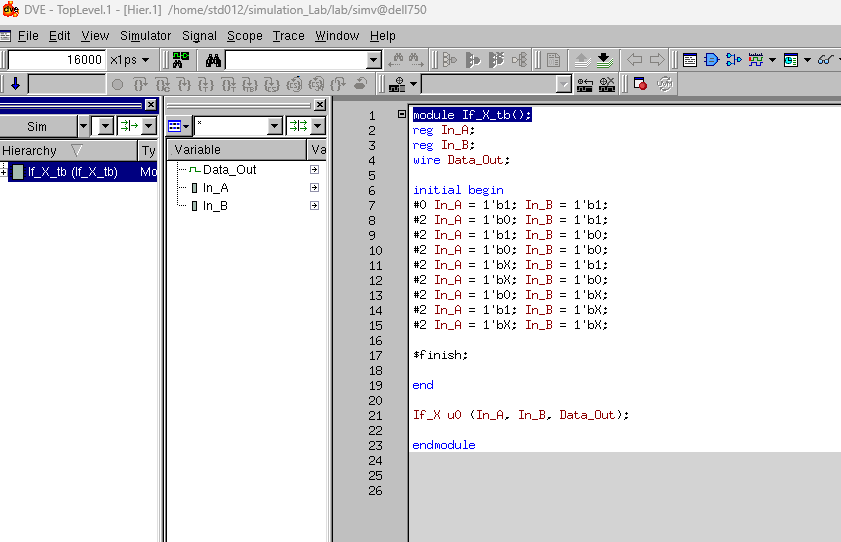

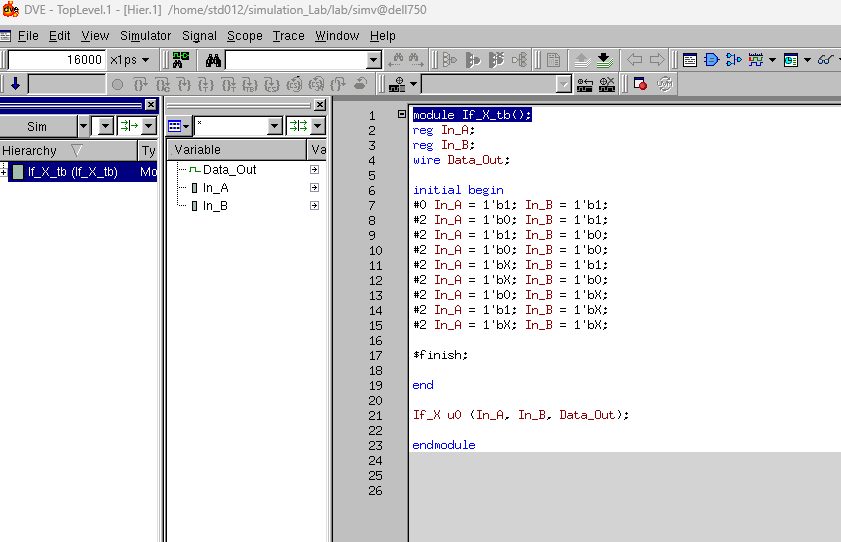

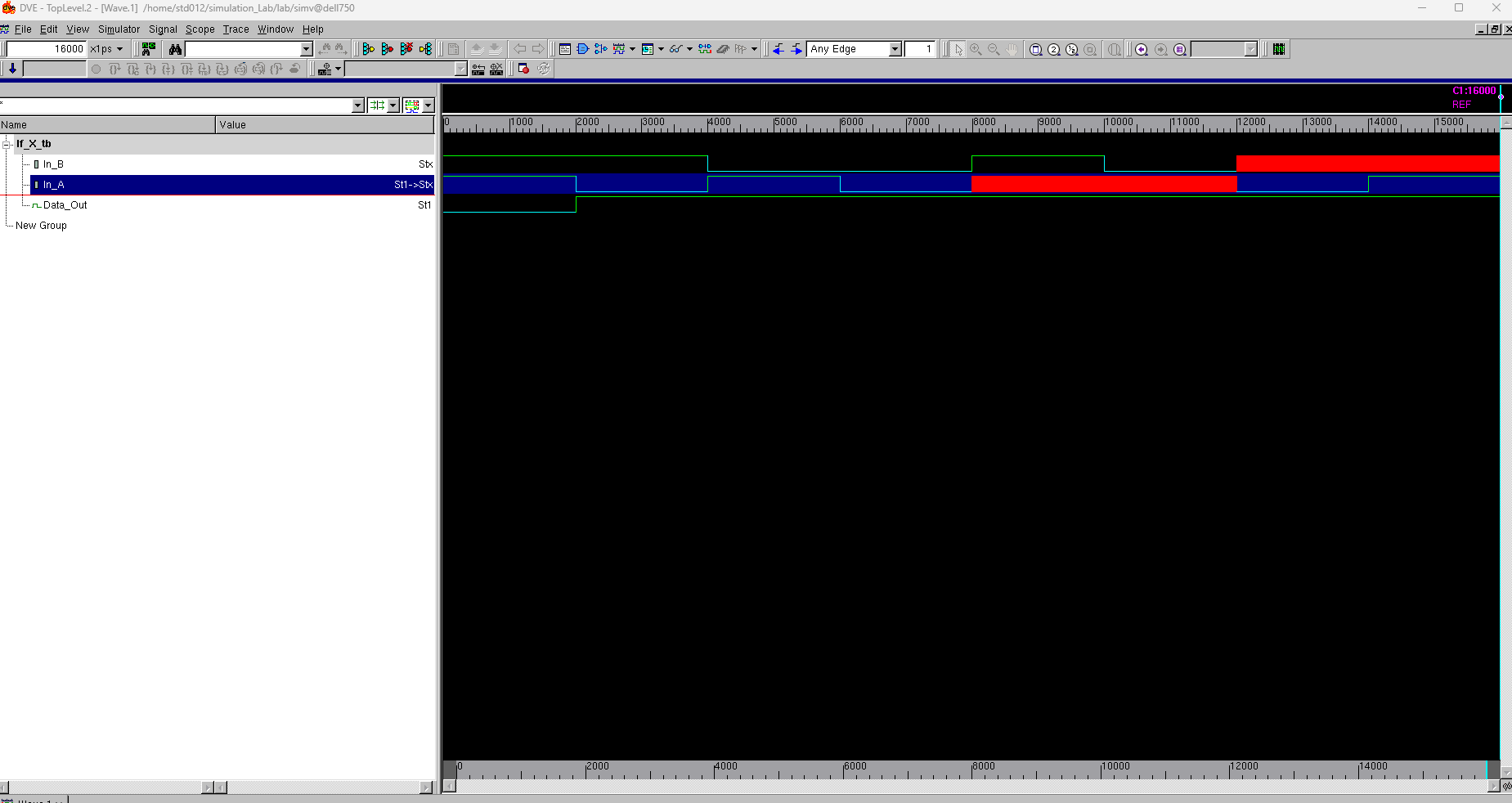

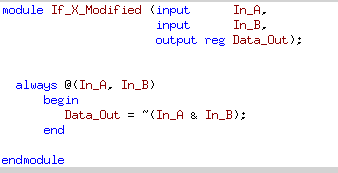

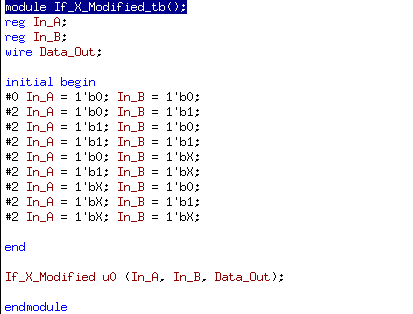

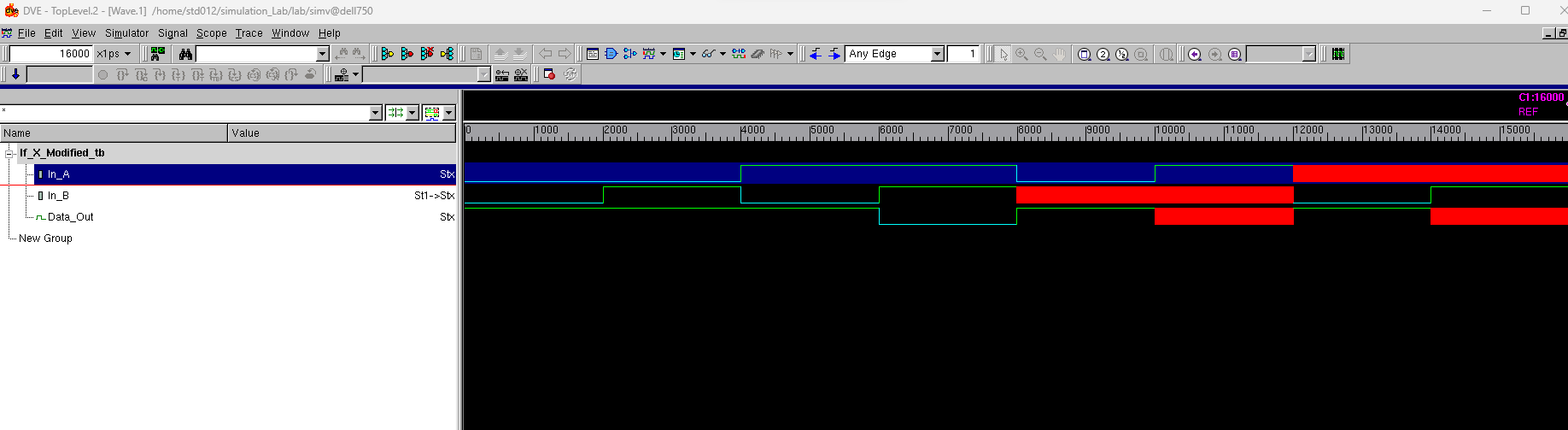

결과 : X(돈케어)가 들어간 NAND 게이트 결과 WAVE로 확인하기

lab 9

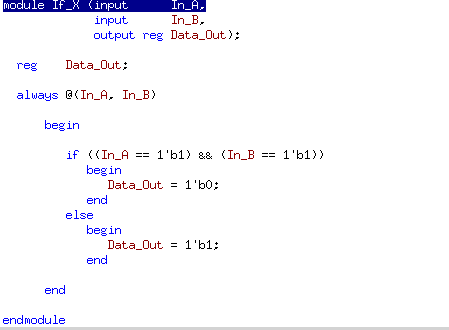

왜 입력이 00이고 11일 때 dont care로 나타나냐?

이전 값이 정해져있지 않아서 발생함

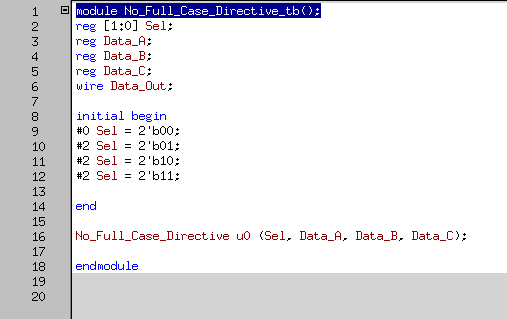

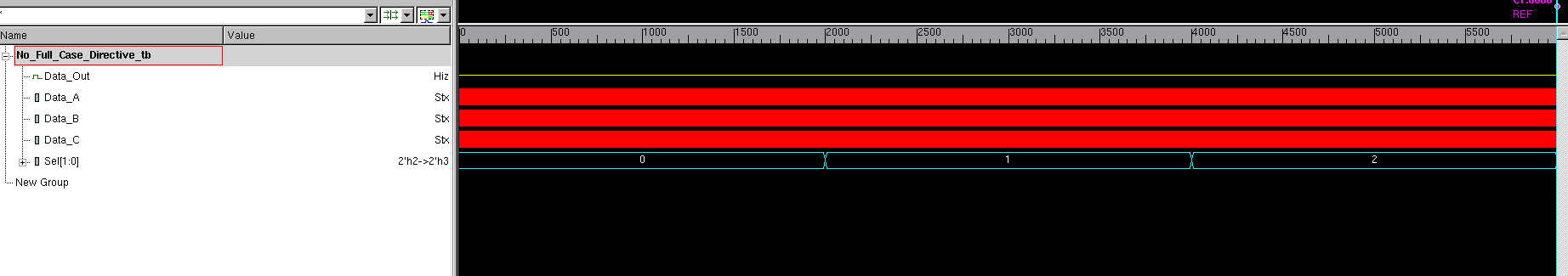

lab 10

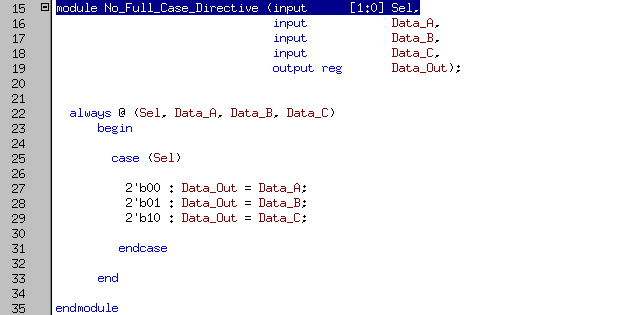

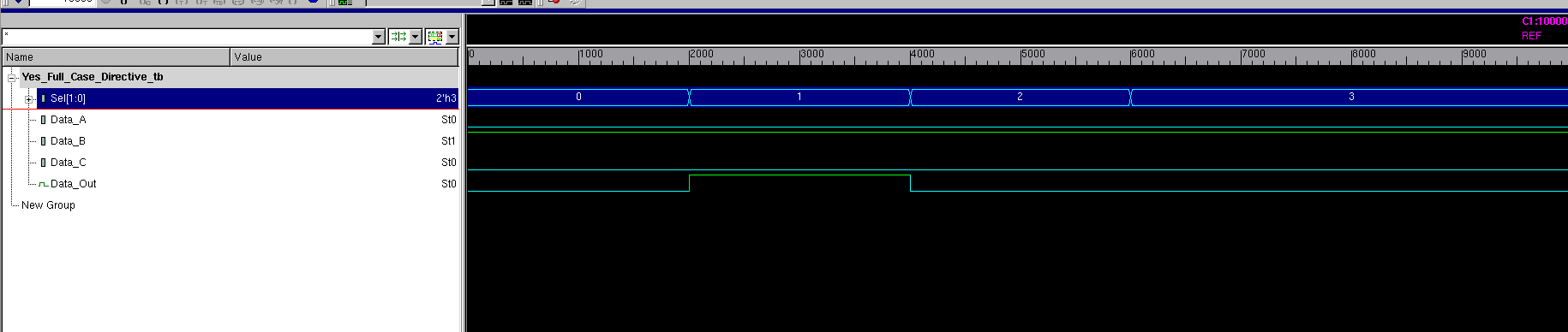

오류발생 : 원인은 Data A,B,C의 디폴트 값을 주지 않음

수정 완료

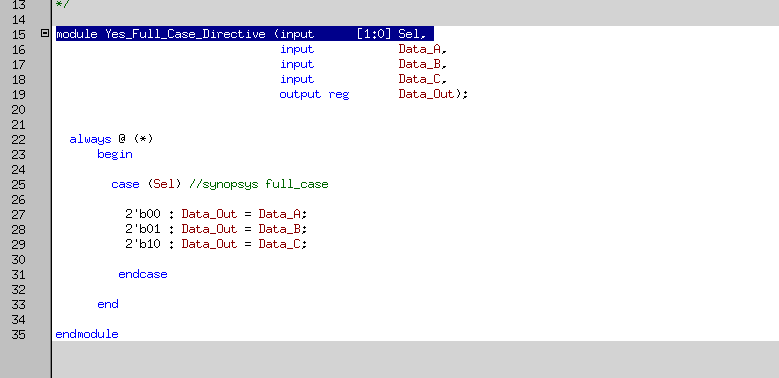

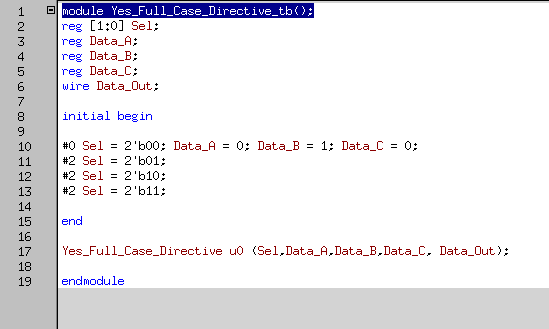

lab 11

lab 10과 11 비교

Non-full-case에 관련된 내용임

DC에서는 전체 조건에서 누락된 경우 Latch가 생성됨

(Solution in DC) full_case Directive로 DC에게 아래 코드로만 case로 되어있고 나머지는 없다는 것을 알려줌

//synopsys full_case : DC에서는 full_case Directive로 인식함.

하지만 VCS에서는 주석처리하여 마지막 값을 출력으로 받음.

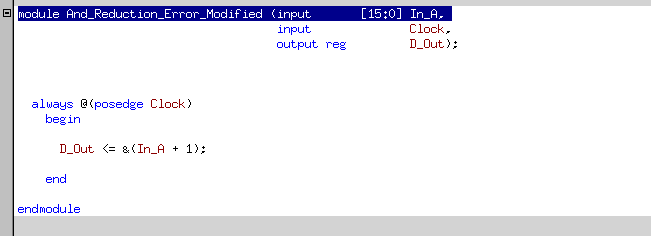

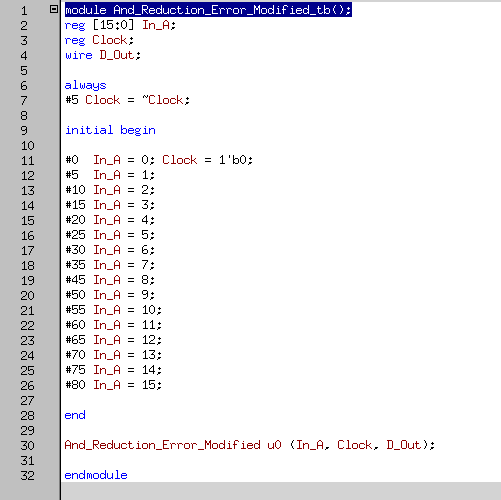

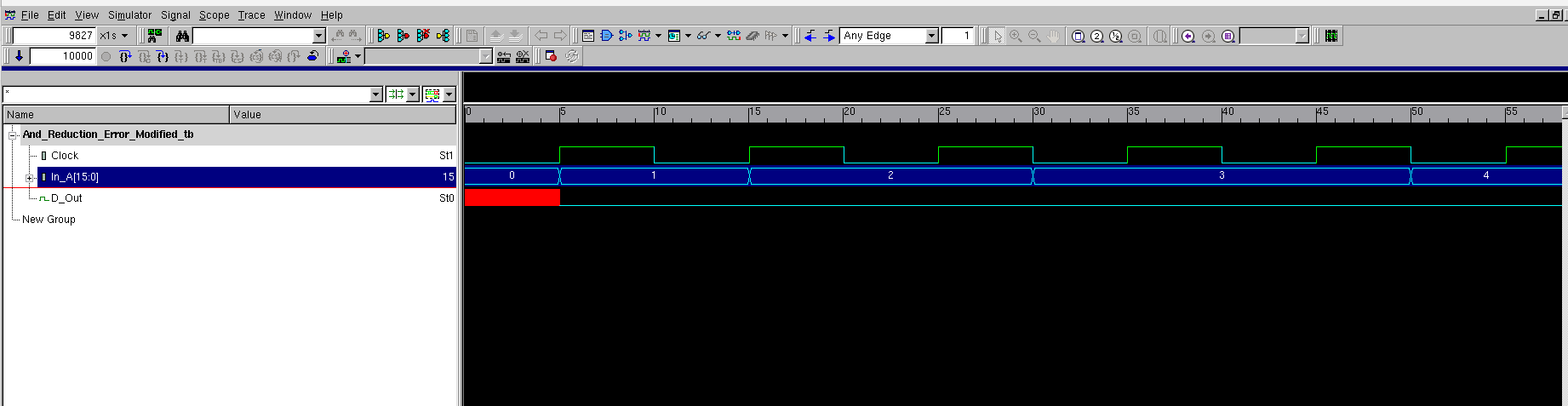

lab17

모든 값이 그라운드로 나온 이유

D_out <= &(In_A + 1)

'1'은 32bit로 인식 그러면 32'b00000...0001

In_A는 16bit이기에 In_A + 32'b00..001은 32bit 나옴

&( ) 는 가로 안에 있는 자리수 값을 다 &로 처리

그렇기에 가로 안에 0이 무조건 있기에 D_out은 0으로 출력

해결방법) 변수 variable을 16비트로 선언하면 결과값 16비트

variable = (InA+1); D_out=&variable; 만약 변수값이 16'b111...111이면 D_out = 1로 출력 가능