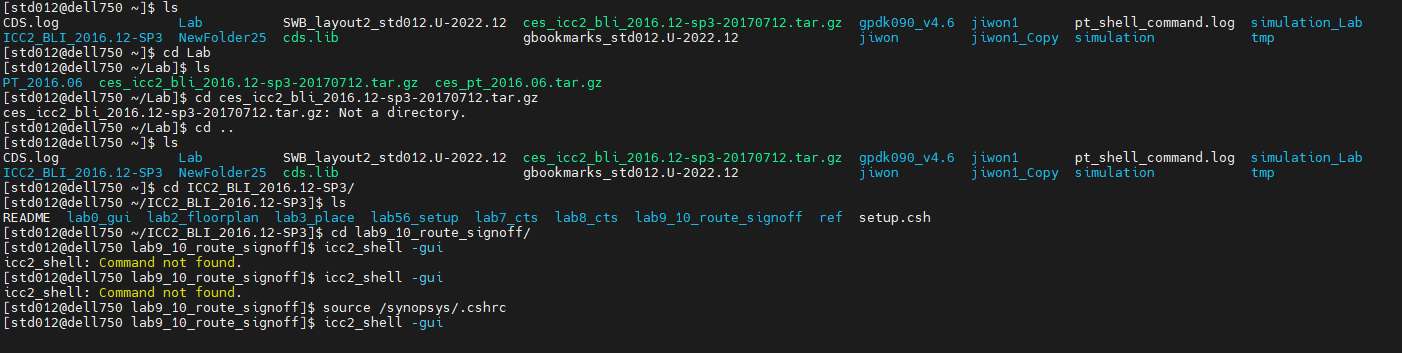

IC Compiler

SYNOPSYS의 주요 TOOL 정리 (by. GPT)

Design Compiler (DC):

- 역할: DC는 RTL에서부터 물리적 레이아웃까지의 과정을 담당하는 통합 툴입니다.

- 기능:

RTL Synthesis: RTL 코드를 물리적인 논리 회로로 변환하고 최적화합니다.

Low Power Synthesis: 저전력 디자인을 위한 기능을 제공합니다.

Formal Verification: 논리 회로의 정확성을 검증하는 기능을 제공합니다.VCS (Verilog Compiler Simulator):

- 역할: VCS는 Verilog와 SystemVerilog 기반의 디지털 회로를 시뮬레이션하는 도구입니다.

- 기능:

기능 시뮬레이션: 디지털 회로의 동작을 확인하는데 사용됩니다.

성능 최적화: 높은 성능의 디지털 시뮬레이션을 제공합니다.

디버깅: 디지털 회로의 버그를 찾고 해결하는데 도움을 줍니다.IC Compiler (ICC):

- 역할: ICC는 반도체 칩의 물리적 레이아웃을 생성하고 최적화하는 도구입니다.

- 기능:

Place and Route: 반도체 칩의 레이아웃을 배치하고 연결하는 단계를 수행합니다.

타이밍 최적화: 디자인의 성능과 타이밍을 최적화합니다.

전력 최적화: 저전력 설계를 위한 최적화 기능을 제공합니다.PrimeTime (PT):

- 역할: PT는 디지털 회로의 타이밍 분석과 타이밍 최적화를 수행하는 도구입니다.

- 기능:

타이밍 분석: 디지털 회로의 타이밍을 분석하여 충족 여부를 확인합니다.

타이밍 최적화: 회로의 성능을 향상시키기 위해 타이밍을 최적화합니다.

시간 및 전력 분석: 디자인의 시간 및 전력 특성을 분석합니다.

1. Data Setup & Basic Flow

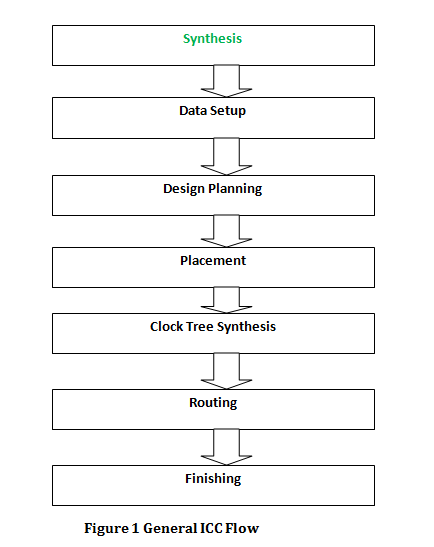

High-Level IC Compiler Flow

Back-End의 흐름

Data Setup:

- 역할: 레이아웃 설계를 시작하기 전에 필요한 기본 데이터를 설정하는 단계입니다.

- 활동:

디자인 라이브러리 및 기술 라이브러리의 불러오기.

사용할 제조 공정에 대한 설정.

디자인의 논리적인 구성을 정의.Data Planning:

- 역할: 레이아웃의 전반적인 계획을 수립하는 단계로, 디자인의 요구 사항과 제조 가능성을 고려합니다.

- 활동:

필요한 클럭 도메인 및 리소스 할당 계획 수립.

전체 디자인의 큰 그림을 그리고 디자인을 어떻게 배치할지 계획.Placement:

- 역할: 디자인의 논리 블록을 물리적인 위치에 배치합니다.

- 활동:

클러스터링: 논리 블록을 물리적으로 가까운 지역으로 그룹화.

초기 위치 배정: 블록을 특정 위치에 초기 배치.

성능과 타이밍 제약을 고려한 최적화된 레이아웃 생성.CTS (Clock Tree Synthesis):

- 역할: 클럭 신호를 전체 디자인에 균등하게 전파하도록 클럭 트리를 합성합니다.

- 활동:

클럭 네트워크 생성: 클럭 트리 네트워크를 디자인에 적용.

클럭 신호의 지연 최적화와 전력 소비 최적화.

클럭 경로 설정.Routing:

- 역할: 논리 블록 간의 연결을 완성하고, 디자인을 물리적으로 연결합니다.

- 활동:

전역 라우팅: 전체 디자인의 초기 연결을 설정.

디테일 라우팅: 각 논리 블록 간의 세부적인 연결을 설정.

경로 최적화: 성능 및 타이밍에 따라 라우팅 경로를 최적화.Finishing:

- 역할: 레이아웃을 최종적으로 검증하고 필요한 보정 작업을 수행합니다.

- 활동:

레이아웃의 물리적인 검증 (DRC 등).

LVS (Layout vs. Schematic) 검증 수행.

다양한 레이아웃 및 타이밍 보정.

ICC를 통한 ASIC 설계 플로우에서는 이러한 단계들이 순차적으로 진행되어 최종적으로 반도체 칩의 레이아웃이 생성되고 검증됩니다. 각 단계에서는 최적화와 검증이 반복적으로 이루어지며, 최종 레이아웃은 디자인 목표와 제조 공정의 요구 사항을 모두 충족하도록 조정됩니다.

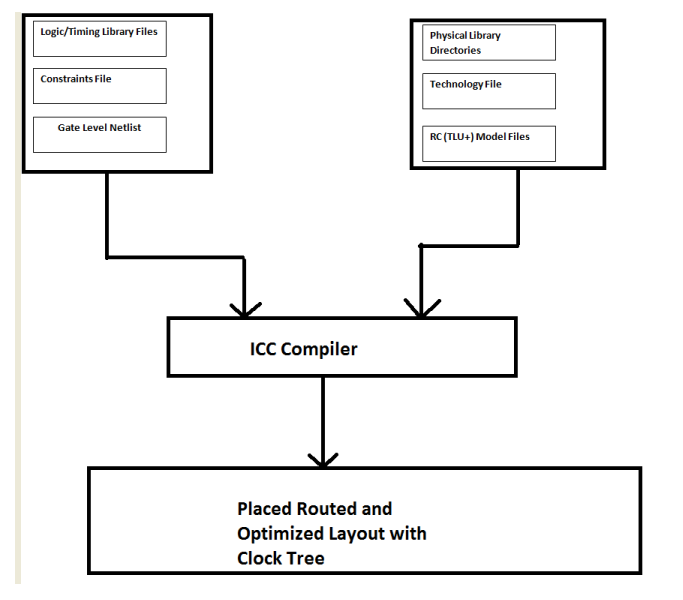

Data Setup

Synthsis Data

Logic/timing library files : 공정사 공급

Constraints File (orca.sdc) : Front-End 공급

GLN : Design Compiler의 결과물

Physical Data

Physical Lib Directories : 셀모양, 특성

Technology File : 메탈의 속성?

RC Model Files(TLU+) : 단위길이당 RC값 >> 결과적으로 timing 알아보기

Logical Lib vs Physical Lib

-

Logical Lib

standard cells : timing, functionality 정보 제공

macro cells : timing 만 제공 (이유 : IP, ROM, RAM은 지적 재산권이어서 공정사가 주는 거 받아쓰면 됨) -

Physical Lib

여기서는 일단 셀들이 실제로 어떻게 생겼는지 정도로 이해

+피지컬 라이브러리의 Milkyway 구조

1. FRAM : 간단. 핀이 어딨고 어떻게 생겼는지

2. LM : logic model view. 조금 더 자세하게, 안에 어떻게 생겼는지

Technology File:

layer, via의 정보, Design Rule에서의 정보, 단위, 색 등등

TLU+ (RC Model File):

레이어의 단위길이당 RC값 정보 >> 이 길이를 계산하여 timing 분석함

라이브러리를 제대로 불러왔는지를 확인하기 위해서는 command를 사용해야 함

set_check_library_options -all

check_library

check_tlu_plus_files

놓친 것이 없는지 확인 & 로직이랑 피지컬이 매칭이 되는지

확인 후에 logical P/G connection 정의해야 함

: 즉, Tool에게 연결할 것을 알려줘야 함

derive_pg_connection -power_net PWR -power_pin VDD -ground_net GND -ground_pin VSS (예)

마지막으로는 Timing Constraints 확인 후 적용해야 함

이 파일은 PI가 줌 파일 .SDC로 되어있음

SDC의 약자는 "Synopsys Design Constraints"입니다. SDC는 주로 디지털 회로 설계에서 사용되는 파일 형식 중 하나로, 회로의 타이밍 및 제약 조건을 명시하는 데에 쓰입니다.

Chip이 어떻게 구동되었는지 적혀있음

예를 들어 clock 주기, set_input,output delay 등등 적혀있음

적절한 Clock Tree 모델 확인하기

clock skew, latency, transition time을 파악해서 적절성을 확인하면 됨

- Clock Skew (클럭 스튜):

정의: 클럭 신호가 다양한 부분에서 도달하는 데 걸리는 시간의 차이를 의미합니다.- Latency (지연):

정의: 시스템이나 회로에서 입력이나 이벤트가 발생한 시점부터 출력이 나오는 시간까지의 경과 시간을 나타냅니다.- Transition Time (전환 시간):

정의: 디지털 신호가 전환되는 데 걸리는 시간을 나타냅니다. 이는 신호가 높은 수준에서 낮은 수준 또는 그 반대로 변하는 데 소요되는 시간을 의미합니다.

그리고 Perform a 'Timing Sanity Check' 해야함.

배치를 시작하기 전에 설계가 제약조건을 넘었는지 확인하는 것이 중요함

제약 조건은 설계 사양과 일치!!!!가 정말 중요

그리고 배치하기 전에 버퍼를 지워야 함

배치 후 버퍼를 지우면 다시 배치해야해서 효율성이 떨어짐

여기서 버퍼는 PI에서 만든 FF의 clk pin 연결 버퍼를 이야기 함

버퍼까지 완료했으면 이제 data_setup 저장!

save_mw_cel -as ORCA_data_setup

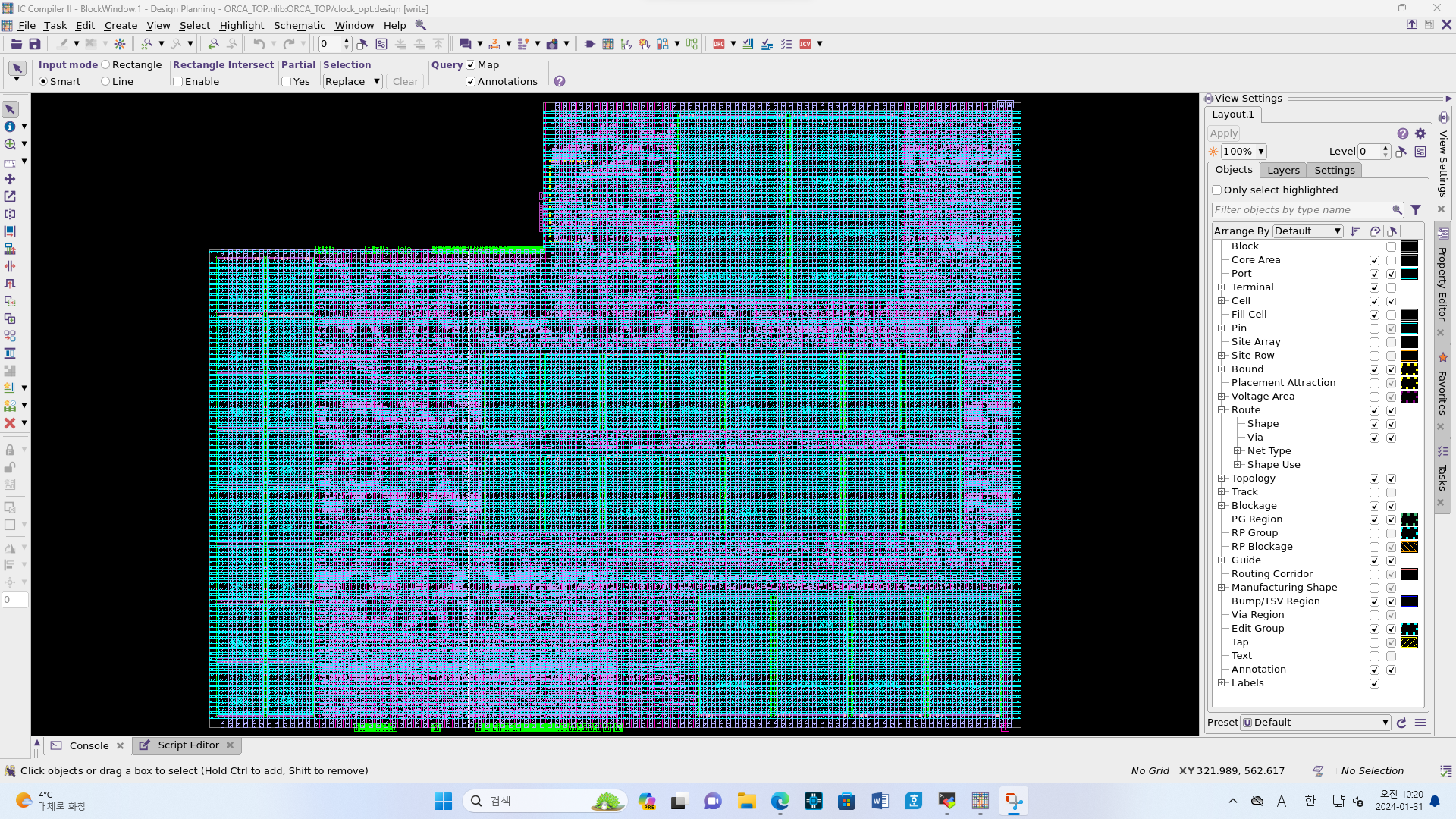

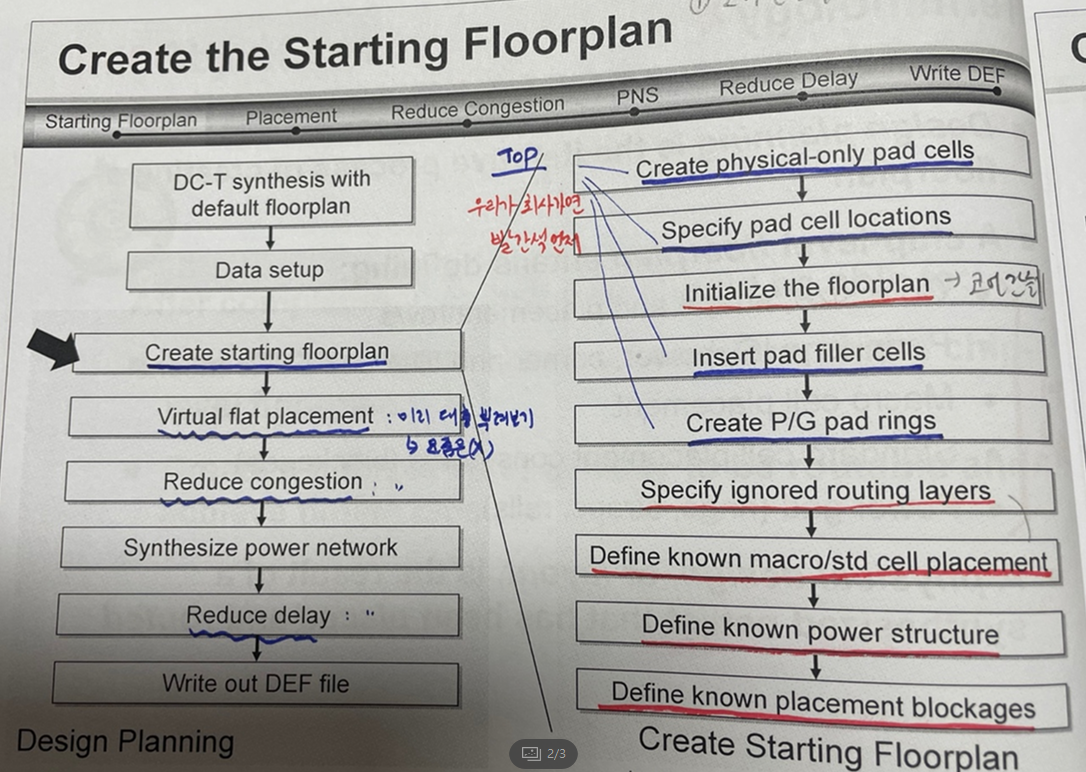

2. Design Planning

이번에는 Design Planning을 Top 관점으로 설명

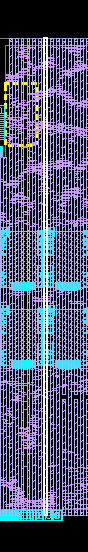

Floor paln

칩크기 > 패드배치 > IP 큰 거 > block-cage(물리적 공간확보를 위해)

Power plan

그 이후 층마다 power 연결하는 power plan

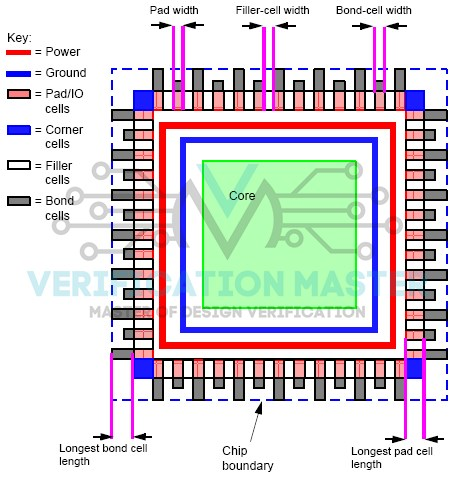

[간단지식]

칩-외부 : 패드

칩-내 디자인 : 포트

게이트 입출력 : 핀

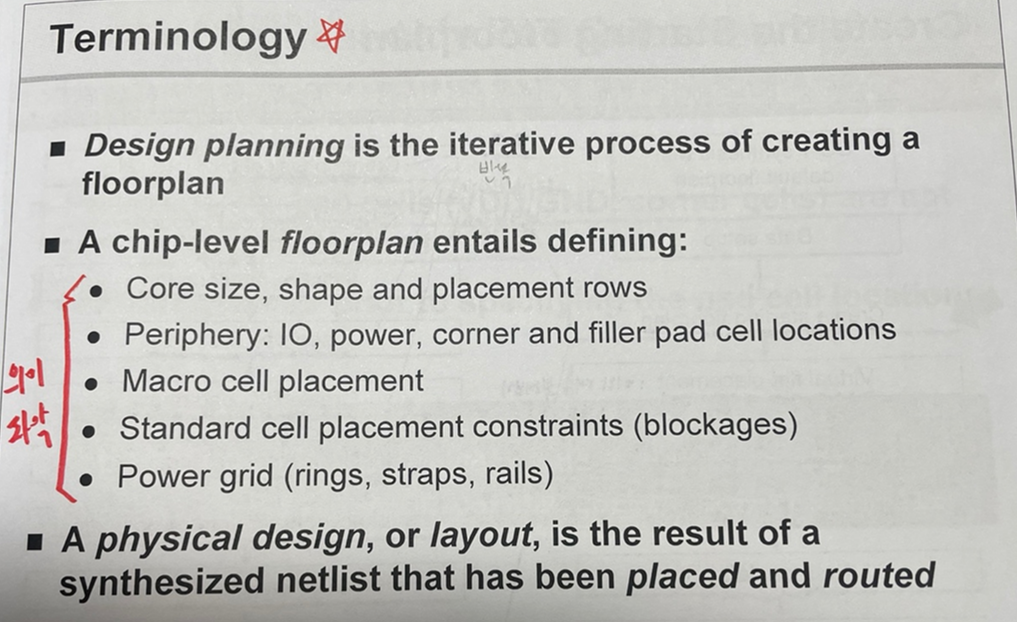

Terminology

Design planning은 flowplan 생성의 반복 과정이다.

A Chip-level floorplan entails defining:

- Core size, shape and placement rows

- Periphery : IO, power, corner and filler pad cell locations

- Macro cell placement

- Standard cell placement constraints (blockages)

- Power grid (rings, straps, rails)

- Core size, shape, and placement rows:

칩의 핵심(Core)의 크기와 형태를 결정합니다.

레이아웃을 행(row) 단위로 구성하며, 각 행에는 특정 유형의 셀이나 요소들이 배치됩니다.- Periphery:

입력/출력(IO), 전원(power), 코너(corner), 그리고 필러 패드 셀의 위치를 결정합니다.

IO 셀은 칩의 외부와의 연결을 담당하고, 전원 및 코너 셀은 전원 공급 및 코너 영역에서 필요한 요소들입니다.- Macro cell placement:

큰 기능 블록인 매크로 셀(Macro cell)들의 배치를 정의합니다.

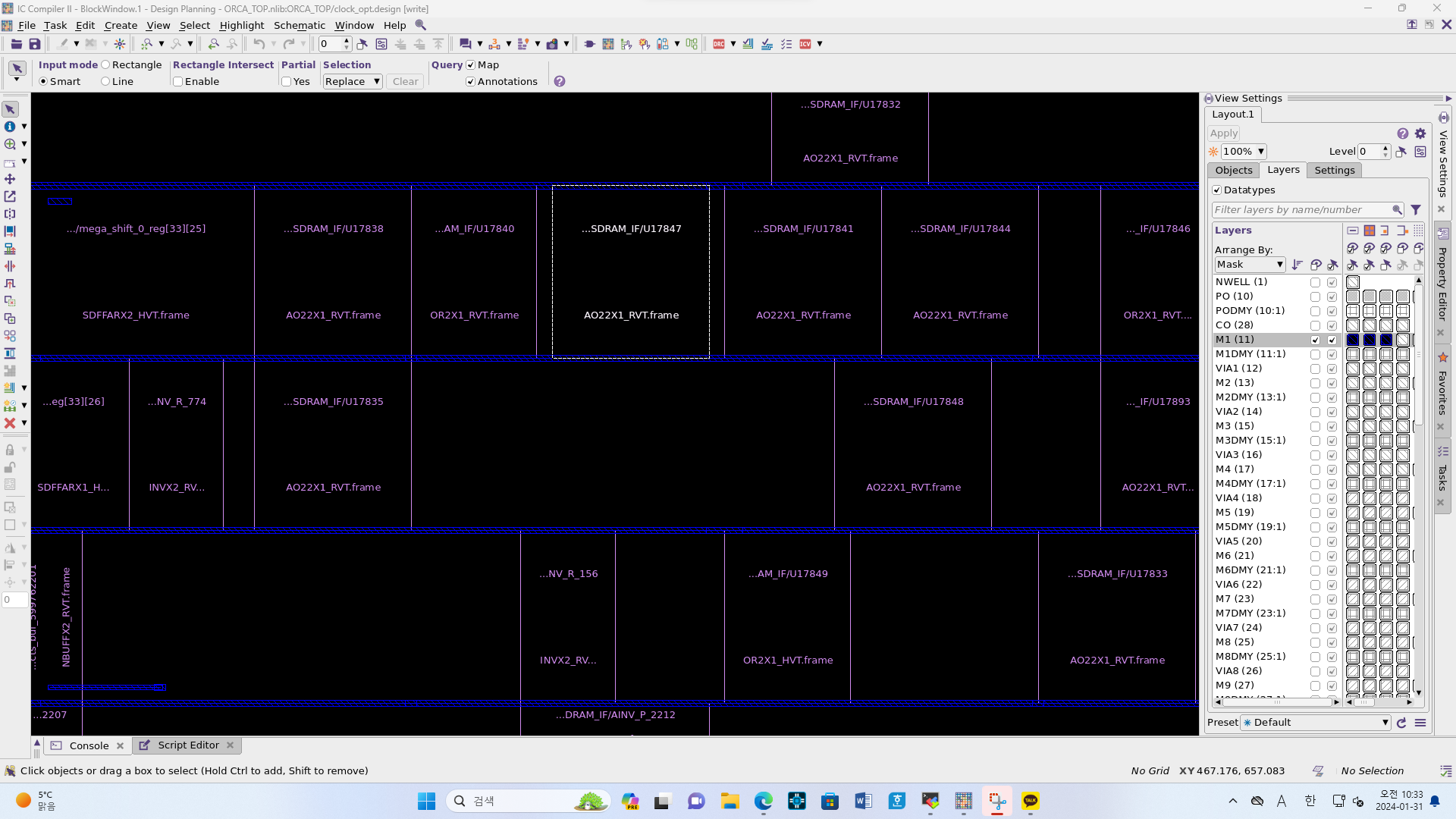

매크로 셀은 일반적으로 복잡한 기능을 수행하는 블록이며, 이러한 블록들은 특별한 배치와 연결이 필요합니다.- Standard cell placement constraints (blockages):

표준 셀들의 배치에 대한 제약사항이나 방해 요소(blockages)를 정의합니다.

일부 영역은 다른 셀들의 배치에 대한 자유도를 제한하기 위해 지정될 수 있습니다.- Power grid (rings, straps, rails):

전원을 공급하기 위한 그리드를 정의합니다. 이는 칩의 전원 신호를 안정적으로 전달하고 전원 분배를 효율적으로 관리하는 데 사용됩니다.

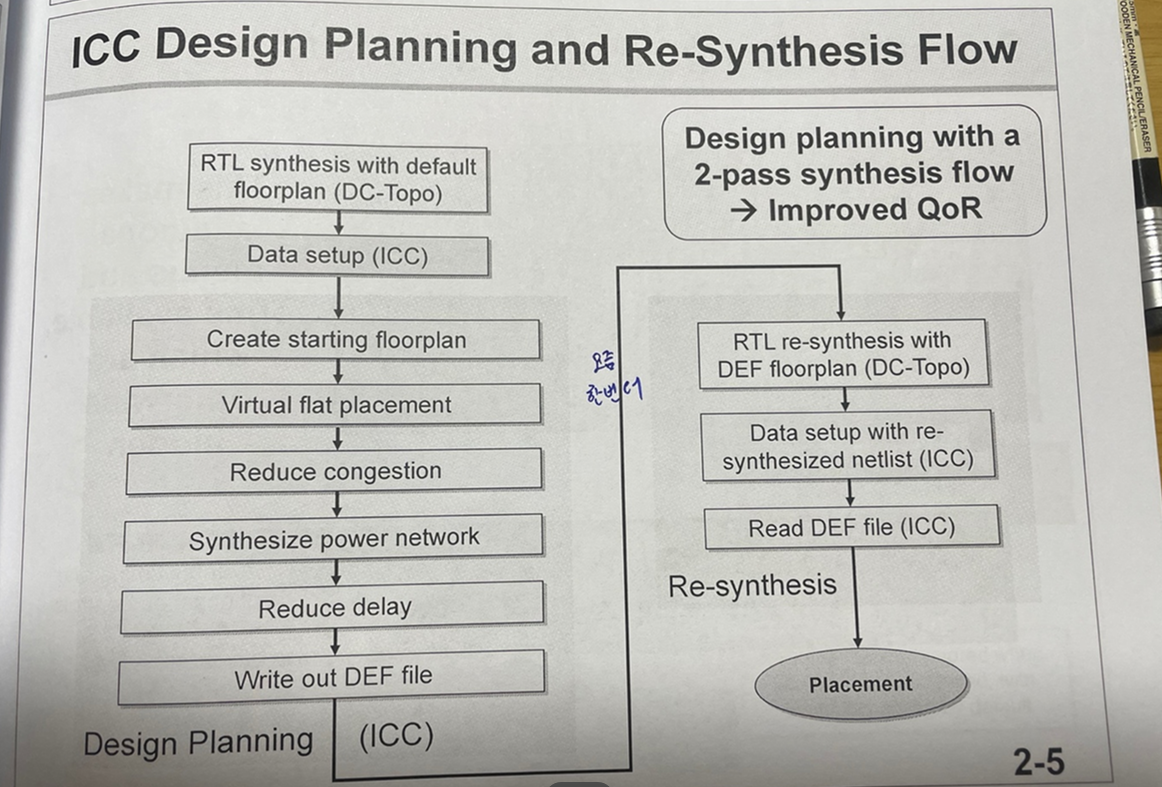

ICC Design Planning and Re-Synthesis Flow

요즘은 DEF 파일을 하고 DC로 가서 한 번 더 검사함

Create starting floorplan

// 빨간줄 우리가 회사가면 할 거

// 파란줄 TOP 엔지니어가 할 거

Create Physical-only Pad Cells

: 전기가 통하는 Pad Cells ( ICC2에서 만들어줘야 함 )

Physical-only pad cells(VDD,GND,corner cells)은 합성된 netlist에 없다.

Pad cell 위치

: side 옵션을 이용하여 배치

corner cell 배치 평면과 pad cell 배치 평면은 다름

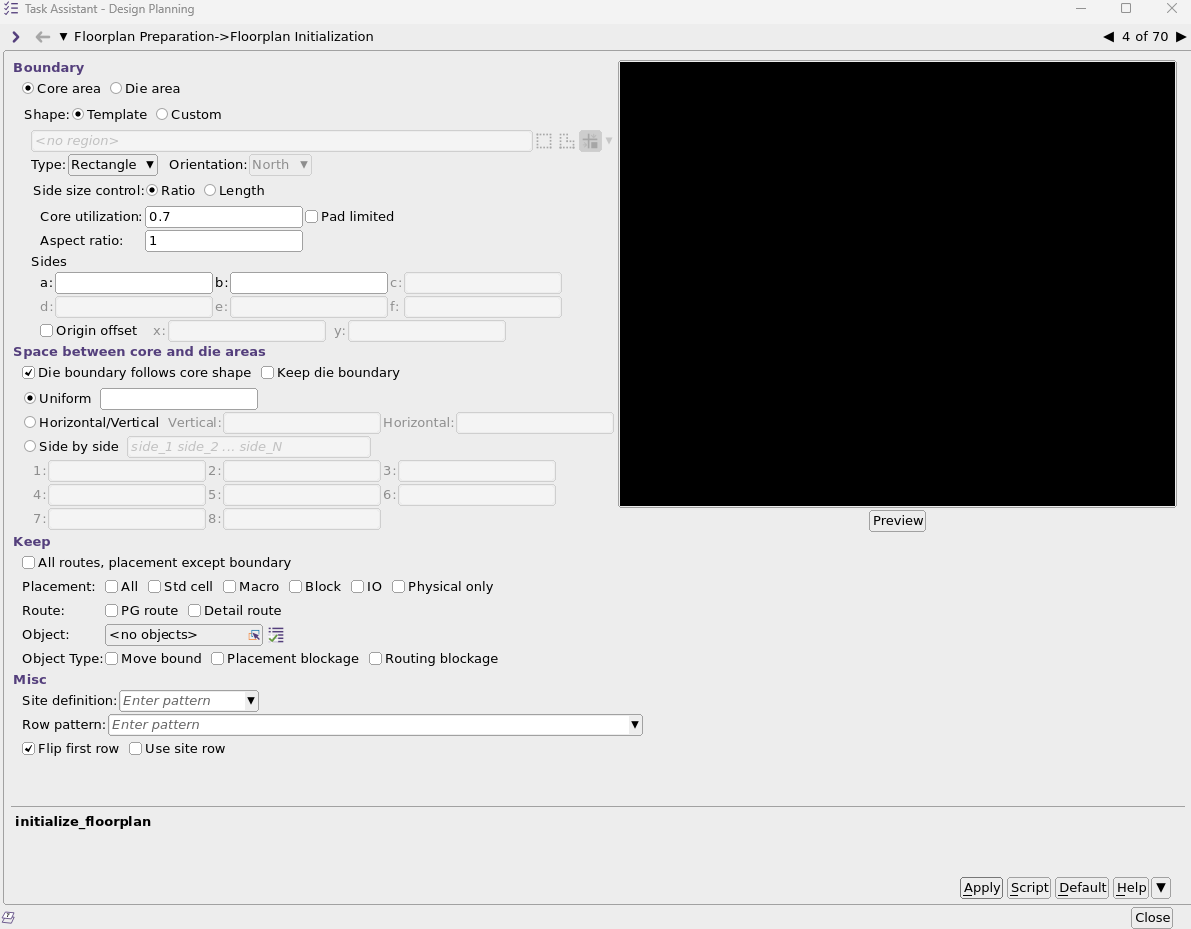

Floorplan 초기 설정 : core와 periphery area 생성

*중요포인트

core utilization : 코어 내부에 얼만큼 cell을 넣을 수 있는지(라우팅 가능한 최대 배치 공간), core to left/right/bottom/top

Insert Pad Filler Cells

: 아무 기능 없는 pad filler cells

P/G Pad Rings

pad 간의 연결다리

Prior to Virual Flat Placement

대충 스탠다드 셀, 고정안된 마크로셀 등등 배치, tech file 레이어 추정

레이어 사용 안하는 거나 placement blockage등등 설정해줘야 함

최대 Routing Layers

Top에서 최대 layer 주어짐

만약에 M1~7로 주어졌는데 더 적게 쓰면 라우팅할 공간이 부족해짐

+congestion analysis는 빠름

Constraining Macros

IP등 Macro cell은 외곽으로 빼는 게 좋음

데이터가 cell마다 연결해서 이어질 때 IP가 가로막으면 net를 길게하여 연결하여야 함

그렇기 때문에 직접 IP 배치를 해야함

그럼 엔지니어는 어떻게 IP를 배치할까?

초반에는 IP 갯수가 적을 때 손으로 배치함

DFF(Data Flow Flylines)는 배치 형식을 알려줌 (방향 : 물리적 공간 (resource)을 아끼기 위해)

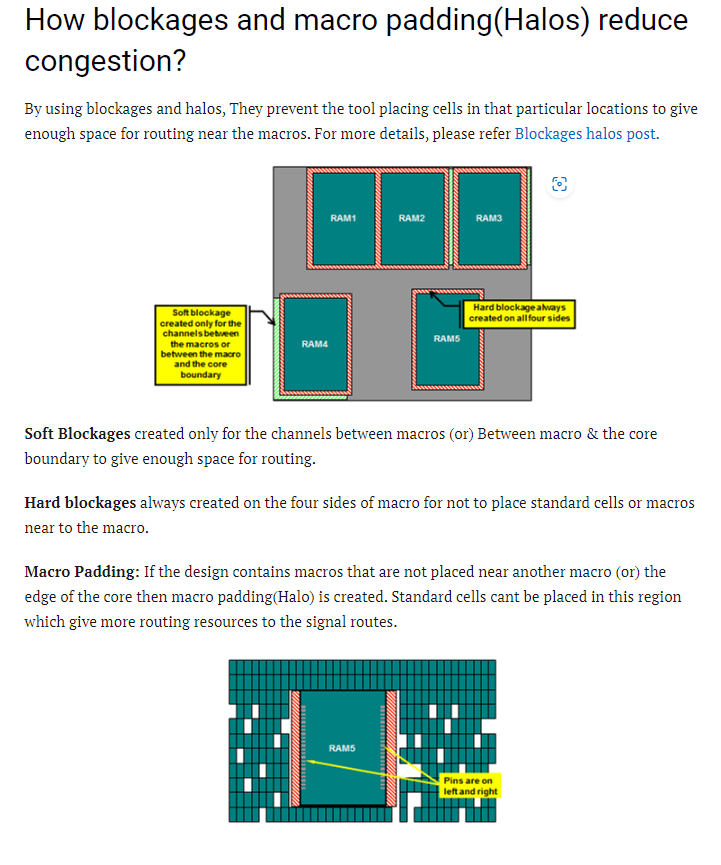

Congestion Potential Around Macro Cells

문제) 라우팅하는 스탠다드 셀은 마크로셀 주변 배치가 어렵다.

해결) 마크로 셀 주변에 Blockage를 두른다.

Hard blockages : 안에 어떠한 스탠다드 셀을 넣을 수 없음

Soft blockages : 필요로 의해서 적당히 들어올 수 있음

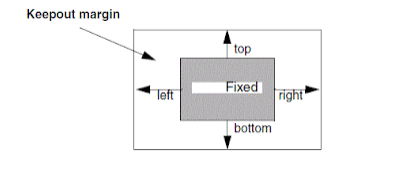

그럼 keepout margin이랑 blockage의 차이는??

셀을 라우팅할 때 편하게 하기 위하기 위한 장벽

명령어로 설정하는 거와 끌어쓸 때 설정하는 거의 차이가 있음.