2. Design Planning

Create starting floorplan 끝난 이후 다음 단계 진행

2.2 Virtual flat placement

2.2.1 Set placement strategy parameters

배치 전략을 짜는 것은 마크로셀을 어떻게 배치하고 다룰 건지, 알고리즘, 노력 등등을 정할 수 있다.

<고려사항>

- sliver size : keepout margin or blackage와 용도 비슷

그래서 실무에서는 silver size 사용 잘 안함

- virtual IPO(VIPO)

timing-critical path(이유 : fan-out) >> tool이 VIPO 안 하고 배치 최적화를 하면 거리만 짧게하고 크리티컬 패스의 원인을 해결하진 못함

VIPO를 이용하면 버퍼를 이용하여 fan-out을 줄이고 크리티컬 패스를 해결할 수 있음

2.2.2 Perform virtual flat placement

- congestion driven : 혼잡도

- timing driven : 타이밍을 줄이는 방식

- hierarchical gravity : 같은 기능을 모아주는 방식

(같은 기능의 cell을 모아서 해주면 net delay가 줄어들고 타이밍이 좋아짐)

하지만 모여 있을 때 라우팅이 잘 될 수 있는지 파악하면서 하는 것도 중요

이후에 혼잡도 분석

2.3 Reduce congestion

2.3.1 Analyze congestion

2.3.2 Modify placement constraints

<혼잡도 줄이는 방법1-마크로셀>

- 마크로셀 사이 간격 늘림

- 마크로셀 사이 버스 신호들 나란하게 함

- 방향 회전, 반전등으로 해결

<혼잡도 줄이는 방법2-스텐다드셀>

- 스텐다드 셀 제약조건 변경 및 설정

+특정 부분 util 조절 가능함

<혼잡도 줄이는 방법3-FP Placement Strategy 옵션>

- 실버사이즈, VIPO 등등

- 마크로셀 가장자리로 주기

2.3.3 Perform congestion-driven virtual flat placement

가상으로 뿌려줌

2.3.4 Analyze congestion

혼잡도를 분석을 하고 문제가 생기면 다시 전 단계들 시작

2.3.5 Perform high-effort congestion-driven virtual flat placement

높은 EFFORT로 가상으로 뿌려줌

실제로는 바로 대부분의 설정값 high로 설정하여 진행

2.3.6 Analyze congestion

다시 분석

2.3.7 Modify the floorplan

만약 최선을 다했는데 안됐다. >> Top 엔지니어한테 부탁해서

포트위치, 칩 사이즈등을 변경

실제로는 말도 안되는 일이다.

2.3.8 Fix all macro cell placements

set_dont_touch_placement [all_macro_cells]

: 마크로셀은 건드리지 말아라. 만약 고정안하고 place 기능을 사용하면 움직임

2.4 Synthesize power network (PNS)

2.5 Reduce Delay

2.5.1 Global Route

route_zrt_global : 가상의 net 잇기

장점 : 시간 단축 / 단점 : 결과가 확실하지 않음

이 교재는 디자인 플래닝에서 가상으로 돌려서 라우트와 플레이스를 하여 확인함

실제로는 현재 가상으로 돌려서 하는 걸 하지 않음 (시간낭비?)

2.5.2. Modify Power Net Placement Blockages

2.5.3 Analyze congestion

다시 확인하기

2.5.4 Analyze Timing

타이밍이 좋으면 DEF write로 감 : Acceptable timing

optimize timing high등등 설정값을 가장 좋게 해서 돌리는 것도 방법

2.5.5 Modify Floorplan or Re-Synthesize, if Needed

노력했는데 안되면 맨 처음부터 다시

2.6 Write out DEF file

배치하기 위한 가장 표준 포맷 파일로 생각하면 좋음

포트나 마크로셀등 고정이 되어있는 것을 저장해두면 나중에 초기로 돌아오거나 다시 시작할 때 큰 틀이 있으니 비교적 수월함

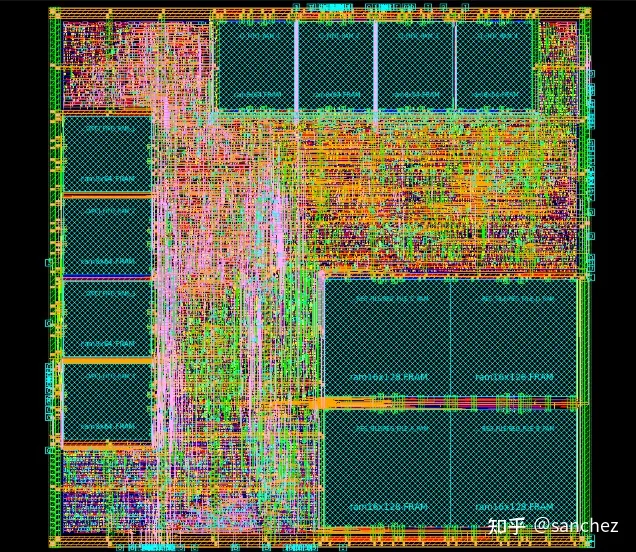

결국 Design Planning은 가상을 제외하면 chip의 모양, 마크로셀 고정, cmd 적용(set 설정해준 것들)을 하여 Placement 준비

3. Placement

Placement 전에 디자인 상태 확인

- 디자인 플레닝 완료되었는지

- Second-Pass Synthesis가 완성되었는지

- Second-Pass Data Setup이 완료되었는지

- Floorplanned cell이 배치를 위해 생성되었는지

코어, 마크로셀 고정, 플레이스먼트 블럭에이지 설정, 파워플랜, 스탠다드셀 지워졌는지

IC Compiler Placement Flow 5단계

3.1 Placement Setup and Checks

-

마크로 셀

set_dont_touch_placement [all_macro_cells] : 셀 고정하는 cmd

-

레이어와 플레이스먼트 constraints 확인하기

3.2 DFT Setup

: design for test

(요약) 만약 PI에서 scandef 파일을 제공해주면 이 명령어를 쓰면 됨

place_opt -optimize_dft

- Scan Chains : 칩이 제대로 작동되는지 확인하기 위해

회로안에 scan chain을 레지스터마다 값을 강제로 집어넣어줌.

모든 레지스터 선을 연결

하지만 선이 비효율적으로 됨

- Chain Reordering : 선 재배열을 통해 효율적으로

reordering을 하면 결과 순서가 달라지는데 큰 문제가 되지 않음. 왜냐면 결과 검사하는 사람이 순서가 바뀐 것을 알고 있으면 문제 없음

3.3 Power Setup

요즘 칩이 작고 민감해서 요즘 timing 다음으로 중요해졌다!