- NDM

- Design Setup

- Timing Setup

NDM을 만들어 ICC2가 읽을 수 있게 logic lib이랑 psysical lib을 합치고 design & timing setup을 해주고 Floorplan으로 넘어가는 상황

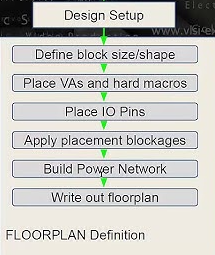

4. Floorplan Definition

엔지니어가 Floorplan에서 무엇을 해야하는지 파악

1. 설정해야하는 요소

- Block shape/size

- Voltage area(VA)

- Macro cell 위치

- I/O pin 위치

- Standard cell placement blockages (to address congestion)

2. PNS Overview

3. DEF file을 write out 하기

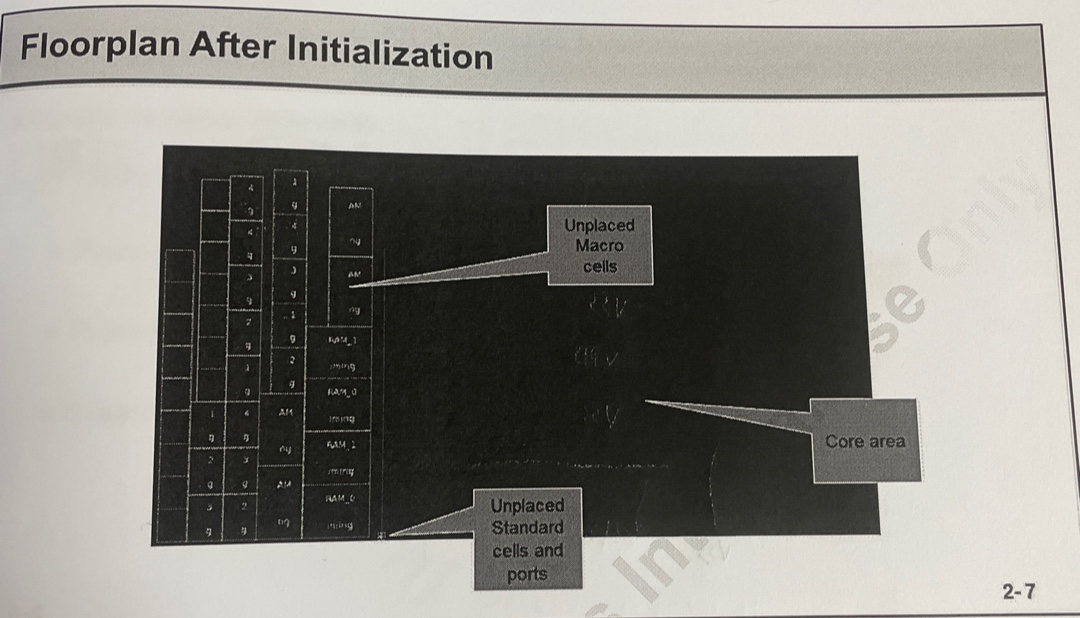

Create the Initial Floorplan

- 스텐다드 셀를 core area에 배치

- 코어 모양 (Rectangular, L, T, U)

initialize_floorplan -core_offset 40 - ....

실무에서는 GUI가 아니라 텍스트로 작업하는 거 참고

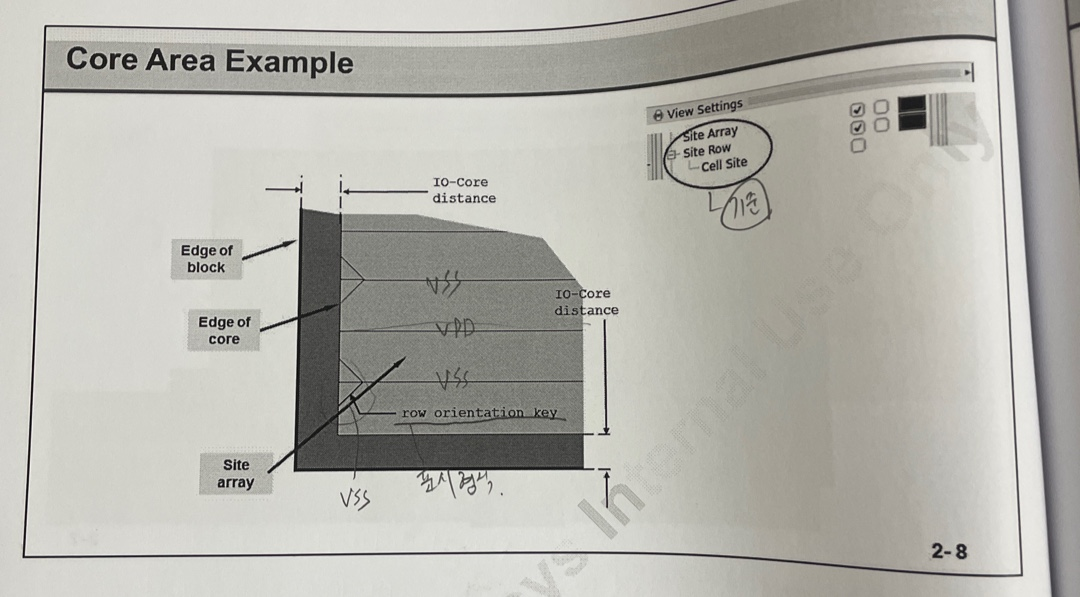

Core Area

site array, row의 역할은 기준을 잡아주는 것 : 배치 배선의 기준

row orientation key는 VDD, VSS 표시 형식 >> 그림 참고

Flat Floorplanning Tasks

- Place and shape all voltage areas

- Place the macros

- Place the block ports (pins)

- Create the power plan

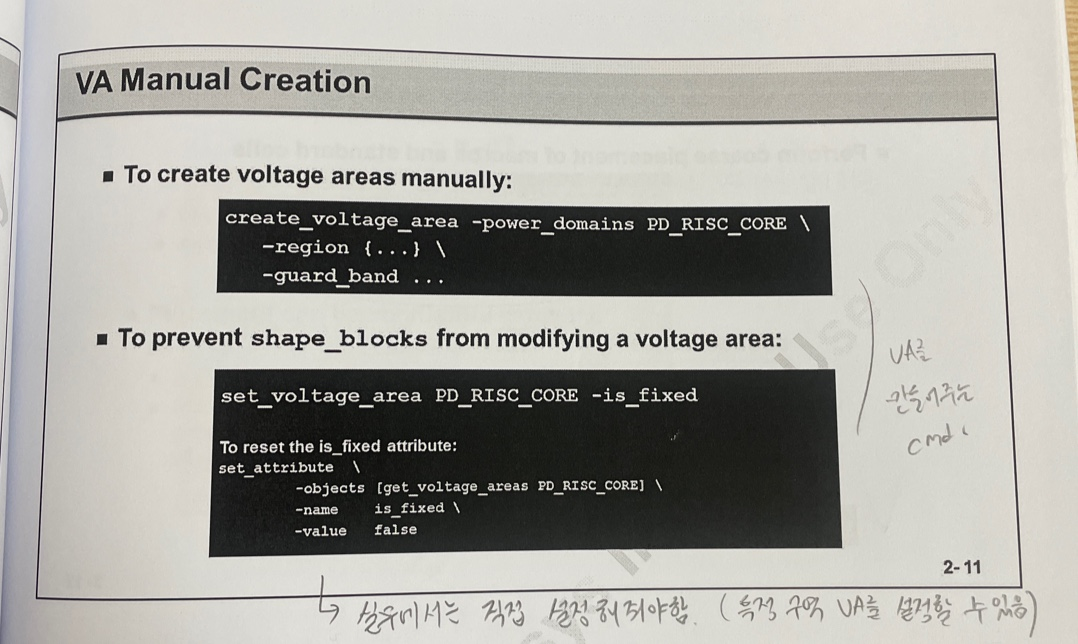

VA : "Shape Blocks"

VA를 하려면 UPF 파일이 필요함

VA를 형성하고 배치하려면 Shape_Blocks이 필요함

ex) level shifter(변압기) 배치를 위한 margin

set_shaping_options -guard_band_size 10

VA 형성 메뉴얼

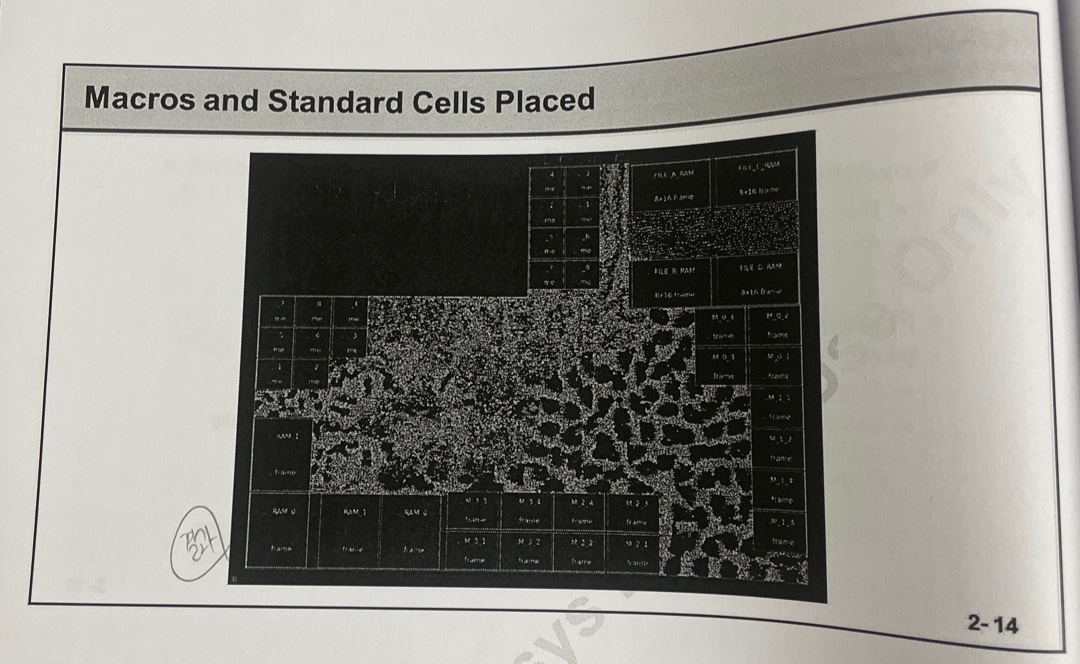

Macros & Stardard Cell 배치

create_placement -floorplan : 모든 스텐다드 셀과 고정이 안된 마크로셀을 배치

배치할 때 plan.place. , plan.macro.을 사용하여 설정해주어 application option을 줄 수 있음

또한 SMART 마크로 배치를 통해 마크로 셀들을 그룹으로 자동적으로 배치할 수 있음

또한 자동적으로 Blockages 배치가 되기는 하지만 다른 요소들도 고려하여 직접 설정이 필요함

Macro cell 배치에는 고정이 필요함

이유) 스탠다드 셀을 배치하고 place_opt (배치 최적화 - TOOL)을 한다면 마크로셀도 움직임

그렇기에 마크로셀 고정이 필요함

set_app_options -list {place.coarse.fix_hard_macros true}

set_placement_status fixed $all_macro_cells : 전체 고정 적용

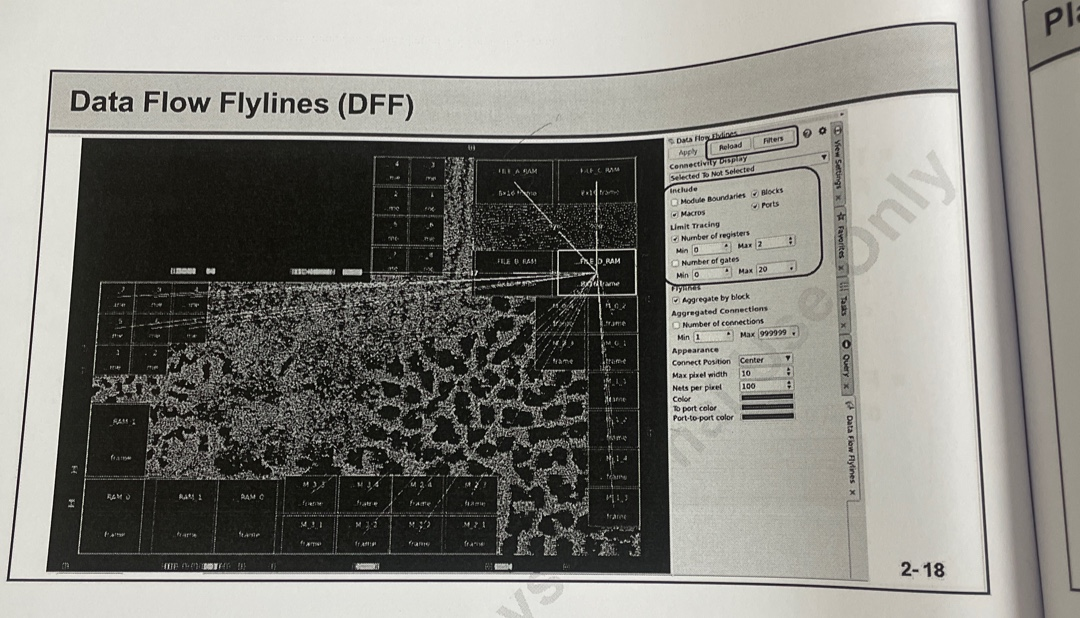

Data Flow Flylines (DFF)

마크로 셀 배치 시 연결선(DFF) 확인하면서 배치

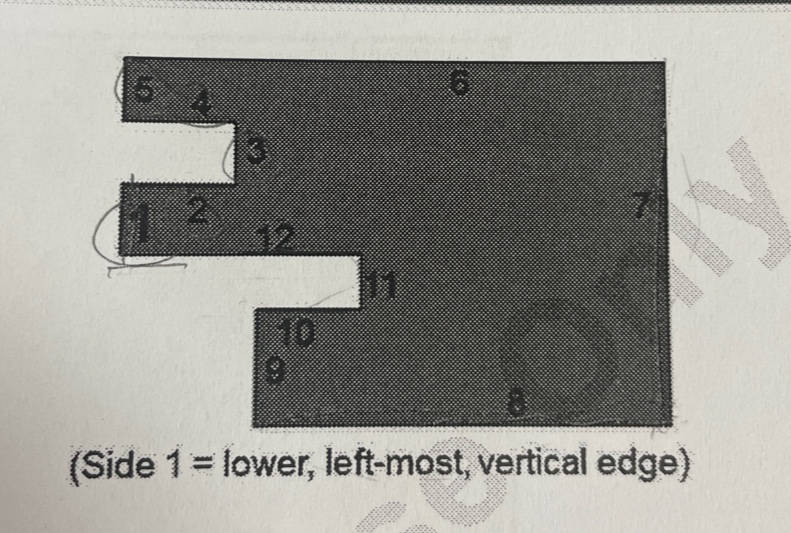

Place I/O Pins

set_block_pin_constraints -self -allowed_layers "M3 M4" -sides "1 2 3 4 5" | -exclude_sides "7 8"

set_individual_pin_constraints -ports ... - ... -

: 세팅

place_pins -self

: 배치

// 왼쪽 가장 아래부터 변의 숫자값 1

Global Route Congestion 분석하기 (GRC)

route_global -floorplan true -congestion_map_only true

Macro cell 주변 padding 적용

keepout margin 주기

create_keepout_margin -type hard -outer {15 0 18 0} RAM5

+$all macro : 모든 IP에 적용

킵아웃마진, 블록지, 헤일로 차이

Power Planning Challenges

- many designs have multiple voltage areas

- complex core rings

- special P/G patterns

Pattern-Based Power Network Synthesis

- PG 구역 정하기

- 패턴짜주기 (링, 레일 메쉬) : metal layers, spacing, width

- PG에 어떤 방식을 사용할 건지 정하기

- Compile power network하기(연결하기)

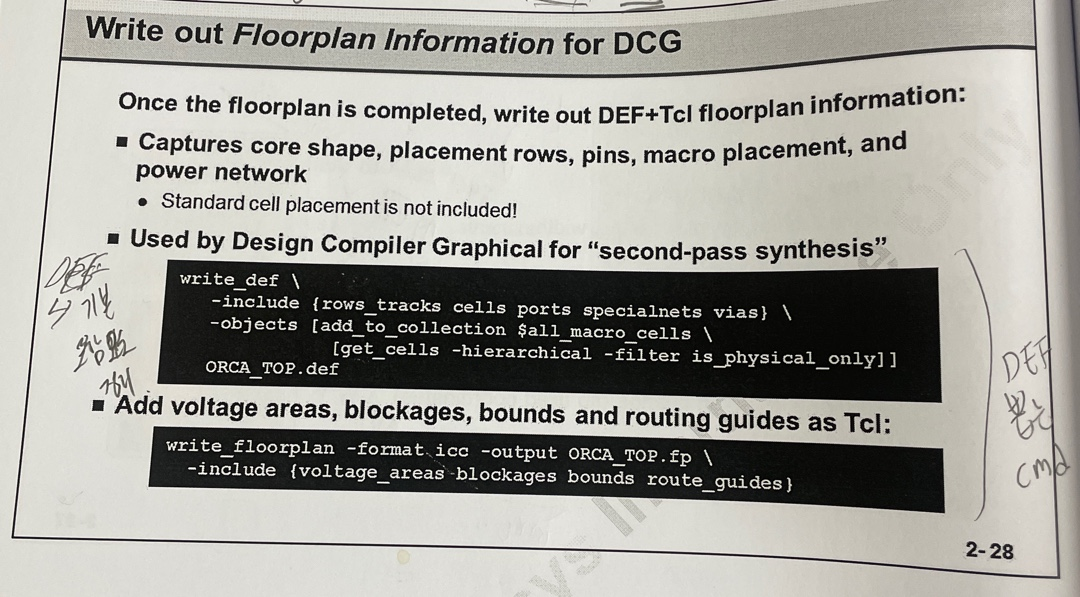

Write out Floorplan Information for DCG

floorplan이 완료되면 DEF + TCL floorplan information을 뽑음

뽑는 이유 : PI 쪽으로 DEF를 넘겨 PD의 피드백이 들어간 틀대로 다시 코드를 짜서 더 효율적인 결과물을 만들 수 있음. 즉, 소통의 역할이라고 생각해도됨

- DEF 뽑는 CMD