Cadence-OrCAD

1.orcad 1일차

수업이 빠르게 진행되어 복습 참고식으로 작성한 글입니다. > Cadence Orcad Capture CIS 회로설계 > CIS ; Component Information System 구매나 제조에서 필요로 요구하는 데이터를 자동으로 검색하고 Schematic 내에

2.orcad 2일차(1)

test07 L1을 변수로 두어 parameter sweep을 사용하여 회로를 간소화 가능 Value List 사용 시 주의할 점 순차적 증가, 순차적 감소만 허용 ex) 5m 15m 20m 11m >> 11m로 감소하면 오류가 나타남 test08 - 몬테카를로

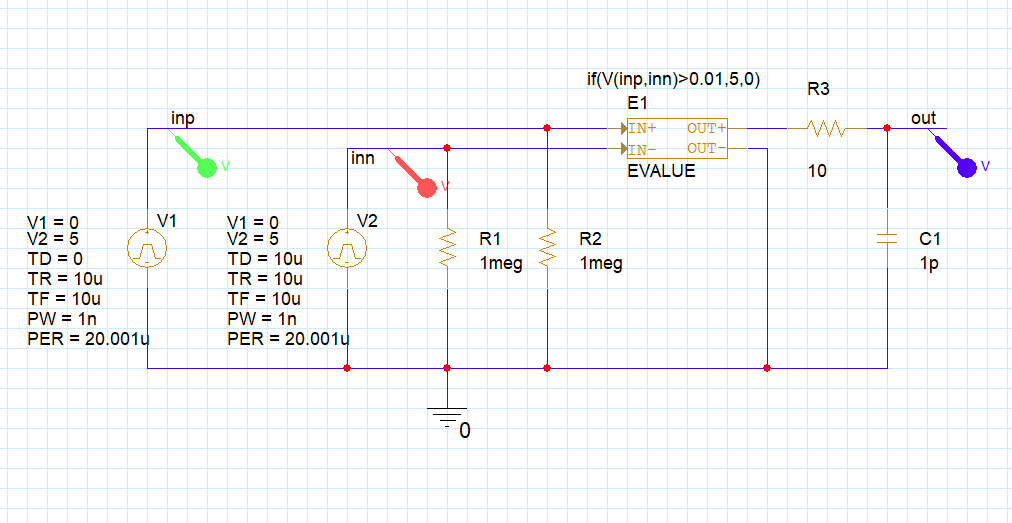

3.OrCAD-2일차(2)

회로도(comp)//0.01//1hie 포트 >> 라이브러리 핀?복사 붙여 넣기 후 진행tools > create netlist나오는 순서는 관계없지만 나오지 말아야 할 문구가 있다고 함SCHEMATIC1 >> comp 모델로 변경inn inp 순서면 1,2번핀 순서

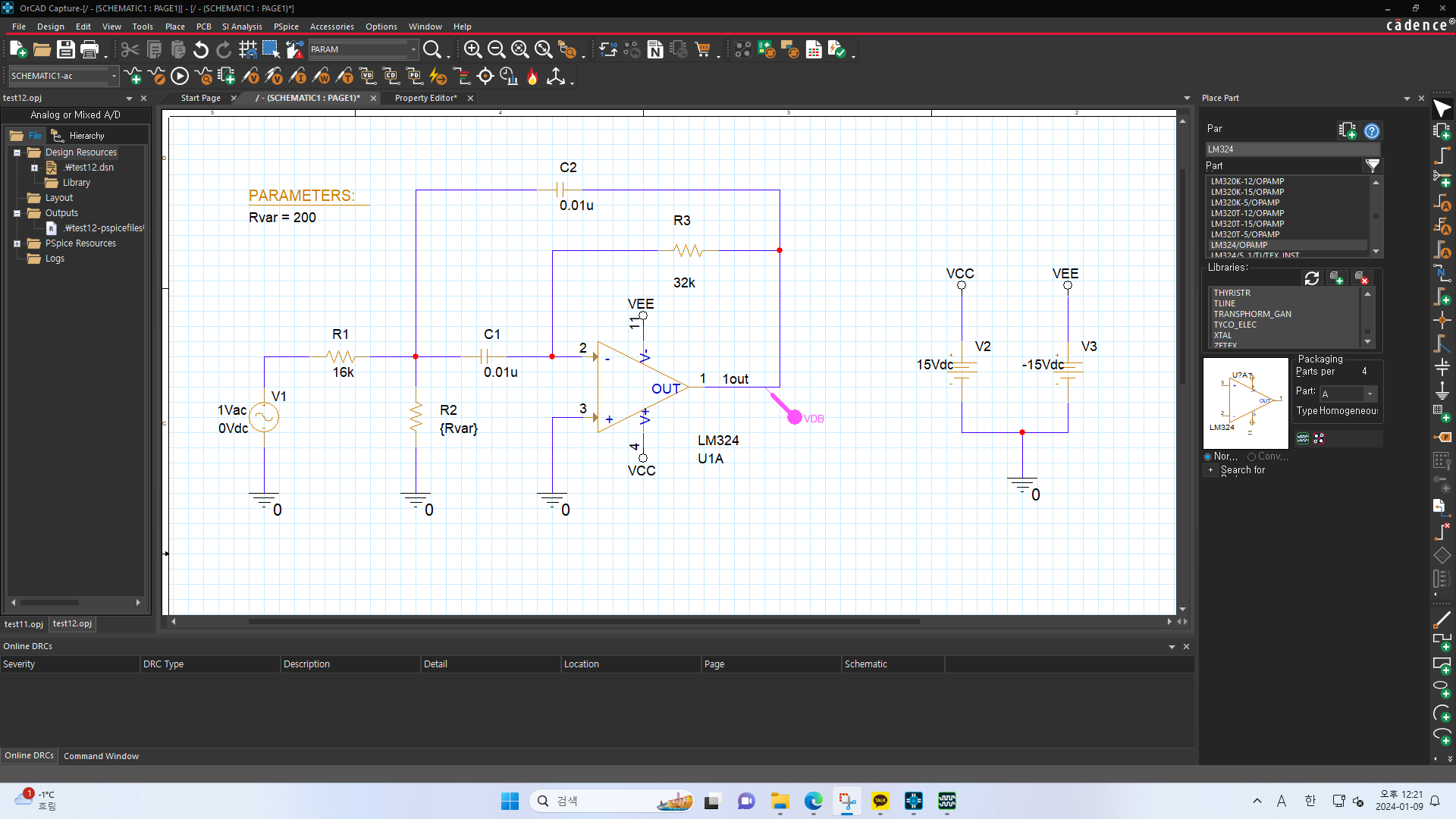

4.OrCAD 3일차

레이아웃 회로설계이기에 체크안함기본 구조로 생성환경설정 단계 먼저option > disign template > page size 사이즈 : A로 A4로 바뀌지 않음앞으로 진행될 형식을 바꿔주는 거임스키메틱 페이지에서 바꿔야지 현재 양식이 바뀜표시는 변경되었다 정도로

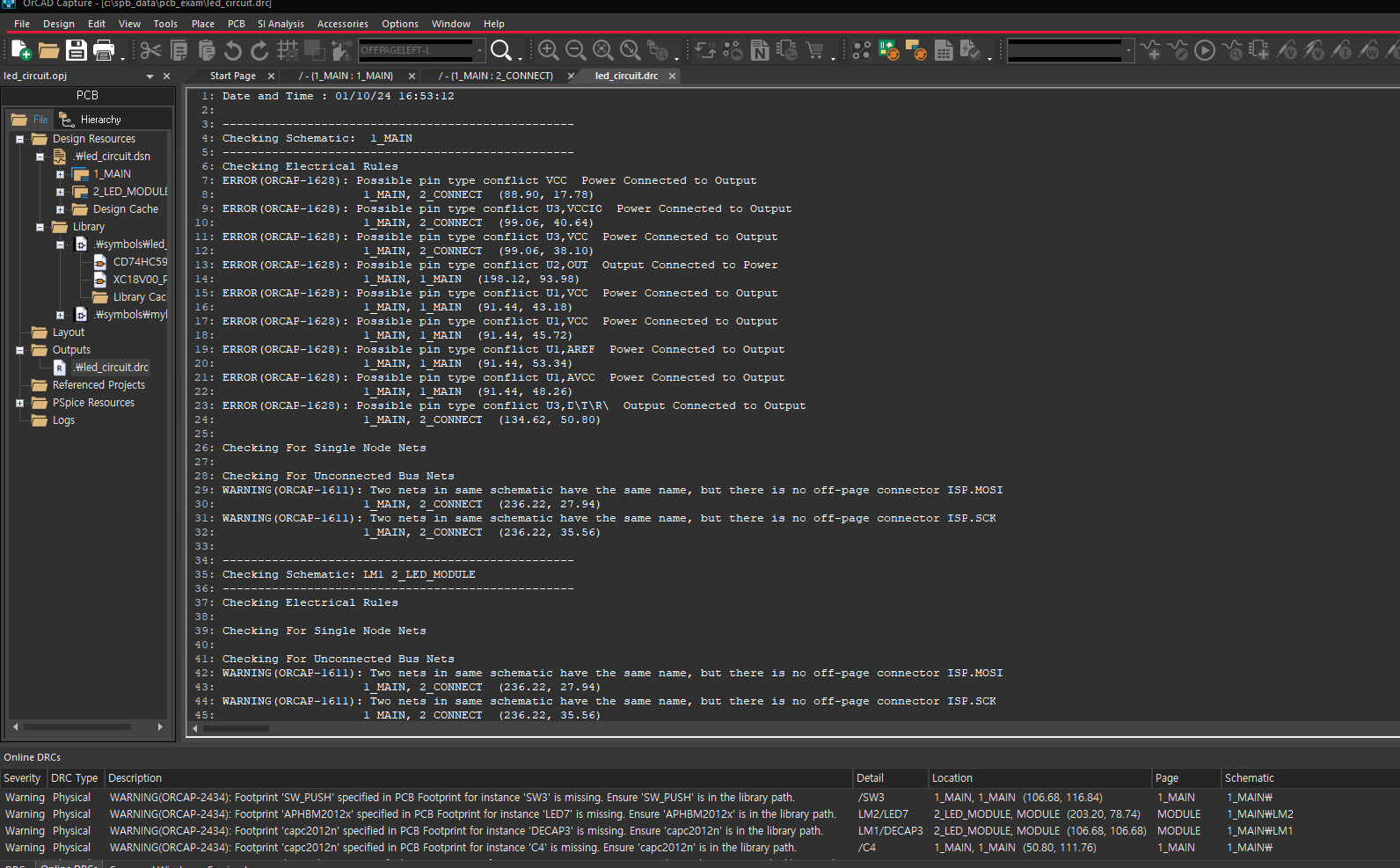

5.OrCAD 4일차

3일차이어서 그대로!DRC 파일이 생성되고 오류 발생된 거 확인해야 함.ERC Matrix : DRC 검사를 할 때, 어떤 기준으로 오류를 검출을 해낼 건지 기준 제시해주는 것W : warning / E : error오류가 해결이 되지 않음.다시 하나씩 차근차근 확인해

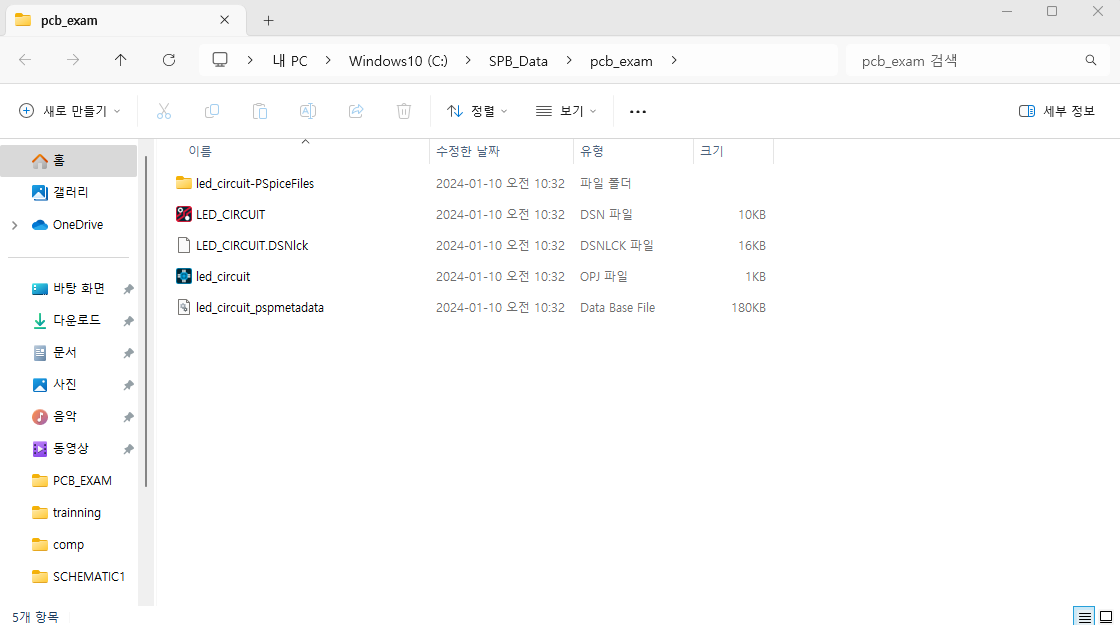

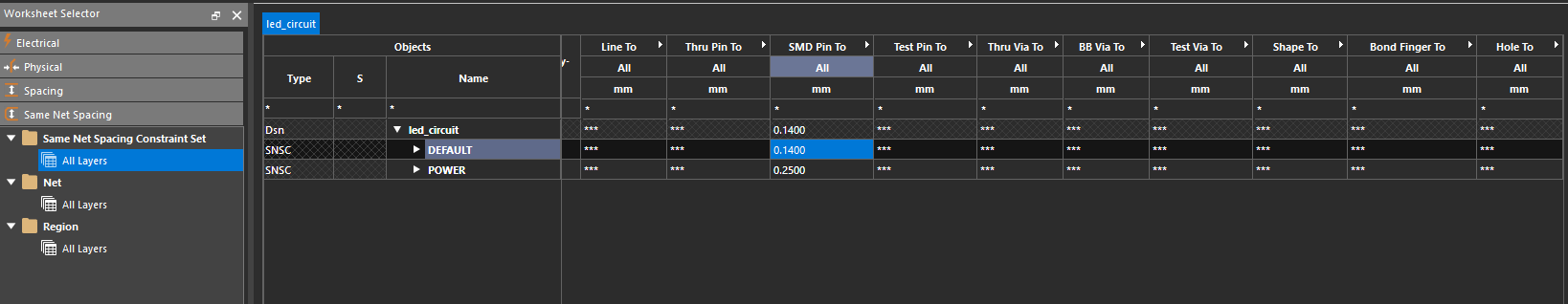

6.OrCAD 5일차

CM- spacing, same net spacing 동일 조건 완료netlist 표시하지 않는 방법(GND)업데이트 DRC방법1.check > DRC UPDATE (이전 작업까지 적용)2.CM > tools > update drcroom 영역 만들기 (outline