공부

1.푸리에 변환, DFT 고찰

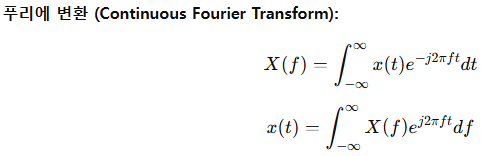

푸리에 변환e^(-j2πft)는 크기가 1이고 각속도를 갖는 복소평면(주파수 영역)의 회전을 나타냄y(t)는 시간 영역에서의 신호이다.두함수 X와 Y가 있을 때 ∫X•Y는 두 함수의 내적(내적 (i,j,k)•(p,q,r) = ip+jq+kr)따라서 회전을 나타내는 함수

2.도움 되는 페이지

https://trts1004.tistory.com/

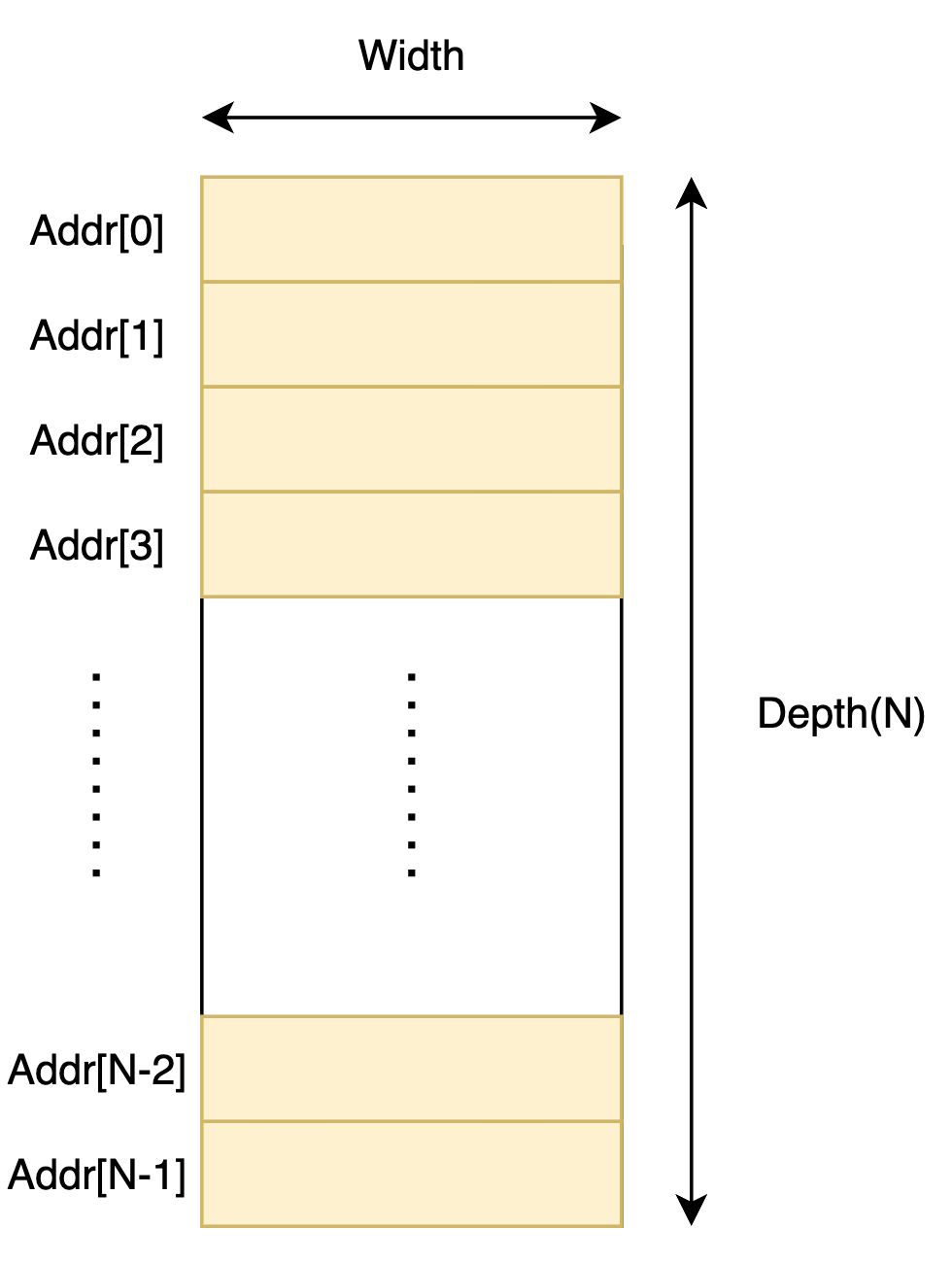

3.메모리 크기(width, depth)

width : 한번에 데이터 길이depth : 메모리 주소의 크기\* 주소 인덱스가 7까지 있다면 모든 주소를 표현하기 위해선 3비트 변수 필요

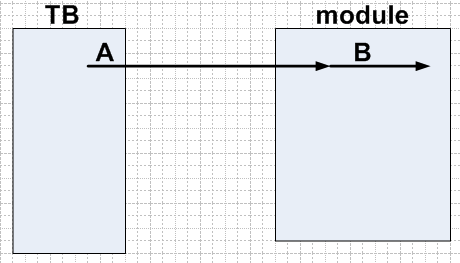

4.verilog, vhdl에서 값 할당

이렇게 TB에서 module로 연결되어 A값을 B에 할당한 신호가 있을때 B로 사용된 신호(조건문에 들어간다던가)를 변경하고 싶을 때 B에 값을 넣는 것이 아니라A값을 변경 해야 한다.

5.미세 팁

enableA와 enableB를 제어할 때 둘은 동시에 켜지면 안되고 하나씩만 활성화 할 수 있을때 signal 하나로 제어하는 법은, 한 쪽을 not을 붙여 연결. 한 쪽을 활성화 했을 때 다른 한 쪽은 비활성화enableA = signalenableB = not s

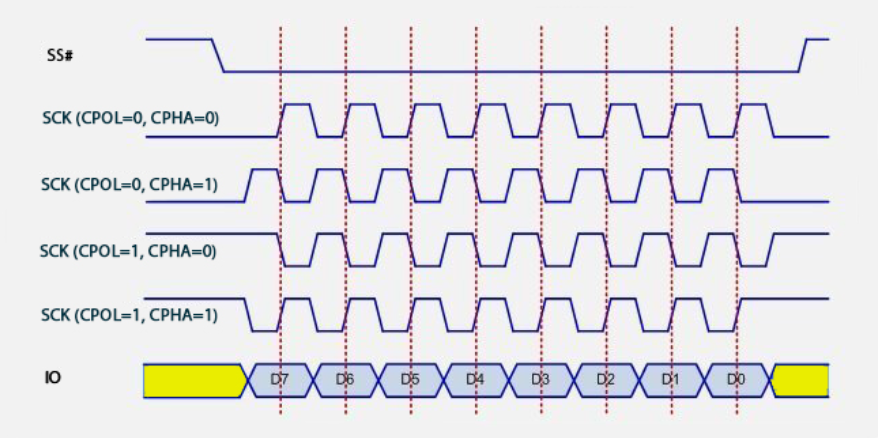

6.SPI mode

spi mode에 따른 데이터 통신의 첫 시점MODE 1 (CPOL = 0, CPHA = 0): 클럭의 기본 상태가 0, 데이터 전송은 클럭이 LOW->HIGH로 변할때 발생MODE 2 (CPOL = 0, CPHA = 1): 클럭의 기본 상태가 0, 데이터 전송은 클럭

7.최초 한번 클럭 펄스

8.I/O standard 관련

I/O standard

implementation, place 후에 즉 합성이 끝나고 로직을 내부적으로 배치할때

10.주파수 분해능과 샘플

제로 패딩은 보기 좋게 만들고 보간(interpolation)한 것일 뿐 실제 정보는 더 주지 않음따라서 더 많은 주파수 성분이 보인다고해도 그것은 해상도가 좋아진 것이 아니라 샘플 수가 늘어난 것뿐=======================================

11.컴파일 에러 디버깅

문제가 되는 모듈을 찾기 위해 하나씩 빼거나 추가, 교체 해본다로직에 문제가 없다면 클럭이 문제될 수 있다. clock_generator의 옵션들의 기능을 살펴보며 점검ILA와 같은 디버깅 분석 툴은 컴파일이 완료되고 신호 분석을 위해 마지막에 사용되어야 하는데 컴파일

12.차동 신호, IBUFDS

clock wizard를 직접 설계가 아닌 IP로 사용한다면 IBUFDS가 내부에 포함되어 있다?

13.SG, SA, GUI

mode 버튼 -> Dual ARB -> ARB (ON) (NR_DL_100MHz_4D1U\~\~~선택)freq 버튼 -> 3650.01 MHzAMPTD 버튼 -> -56dBm, 케이블 감쇄 테스트시에는 -10dBmAMPTD offset 사용span : 100~200

14.PS의 듀얼 코어 사용

https://www.hackster.io/whitney-knitter/dual-arm-hello-world-on-zynq-using-vitis-9fc8b7플랫폼 프로젝트platform.spr에서 도메인 추가새로운 어플리케이션 프로젝트 생성하면서 두번째 코어로

15.최저 수신 레벨 테스트

기본 TDD 신호 사용

16.종단