단위공정

반도체 8대 공정과 8대 단위공정이 무엇인지 설명하시오.

8대 공정:

웨이퍼 제조

산화 공정

포토 공정

식각 공정

증착 & 이온주입 공정

EDS 공정

패키징 공정

단위 공정:

Photo

Etch

Ion Implant

Diffusion

CMP

Thin Film

Claning

layer의 의미와 단위공정과의 관계를 설명하시오.

-

반도체 FAB 공정 진행의 기준은 항상 PHOTO 공정

-

Mask를 이용해 원하는 패턴을 미리 만들어 놓고 이를 식각하고 junction을 만들기 위해 이온주입을 한 후 다시 박막이나 메탈을 쌓고 연마를 함

-

이러한 photo 공정을 중심으로 다른 단위 공정들의 조합으로 만들어지는 one-turn을 layer라고 하며, 보통 한 장의 mask를 이용하여 한번의 photo 공정을 한 layer라고 함

단위공정의 종류와 목적을 설명하시오.

- photo 공정

wafer 패턴을 만들기 위해 패턴이 그려진 mask를 이용하여 PhotO Resist를 도포한 후 마스크를 정령,노광,현상하는 공정 - Etch 공정

원하는 패턴을 만들기 위해 photo 현상 후 드러난 막질이나 실리콘을 화학적으로 녹이거나 깎아내는 공정 - clean 공정

wafer 표면을 깨끗하게 하기 위해 오염물을 화학적,물리적으로 제거하는 공정 - 이온주입 공정

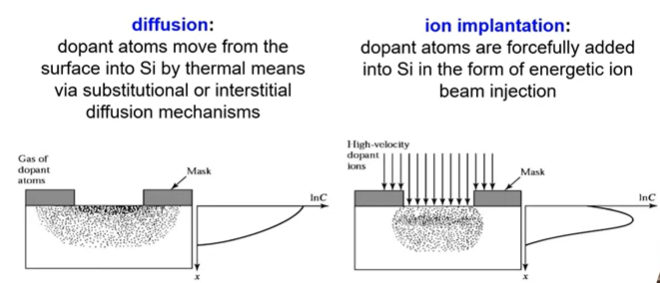

반도체가 전기적 성질을 가질 수 있도록 전기를 흐르게하는 캐리어를 지닌 원자나 분자를 이온 형태로 silicon에 주입하는 공정 - 확산 공정

확산을 이용하여 원하는 소자의 특성을 확보하기 위해 silicon 표면에 주입된 불순물 이온들을 고온 가열을 통해 원하는 깊이만큼 고르게 분포시키는 공정 - CVD 공정

silicon 위에 박막을 형성하기 위해 원자/분자 단위의 물질을 기체 상태로 분사하여 반응시켜 원하는 두께의 막질로 증착하는 공정 - CMP

단차에 의한 후속 공정 불량을 막기 위해 울퉁불퉁한 막질이나 물질을 화학적 반응과 기계적 힘을 이용해 연마하는 공정 - Metal 고정

소자들의 전기적 연결을 위해 전기전도도가 높은 금속 물질을 막질로 증착하여 연결하는 배선 공정

Clean

세정공정의 중요성을 설명하시오.

- 미세공정으로 갈수록 step 수가 증가하여 오염물 발생 기회가 증가

- 오염물의 크기도 과거에는 무시할 수준인 것들이 미세공정에선 치명적인 불량을 일으킬 수 잇음

- 이런 물질을 잘 제거하지 않으면 수율을 떨어뜨릴 수 있음

이로 인해 세정공정의 중요성은 증가하고 있으며 실제 반도체 미세공정의 공정 수 증가에 제일 큰 원인은 세정공정의 추가라고 할 수 있습니다.

반도체 공정의 다양한 오염물들을 설명하시오

- 외부에서 유입되는 오염물질

- 사람의 유기물, 염분, 미세먼지, 장비 오염물질

-> 이는 사람이나 원부자재가 FAB Line에 들어올 때 유입될 수 있음

- 사람의 유기물, 염분, 미세먼지, 장비 오염물질

- FAB 진행 중 발생

- 공기 중 노출에 의해서 발생하는 자연 산화막

- PR제거 과정에서의 PR 잔류물

RCA 세정

- 단점

1) 다양한 케미컬과 많은 양의 케미컬이 필요함

2) metal이 사용된 물질에는 사용할 수 없음

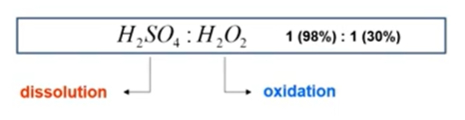

1) Piranha : 유기 잔류물 제거

황산 + 과산화수소

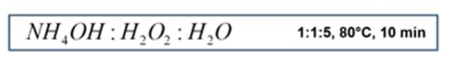

2) SC-1 : 유기물 잔류와 입자들 제거

수산화암모늄 + 과산화수소 + 물

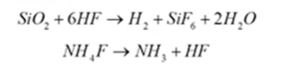

3) native oxide strip: SiO2 제거

불산(HF)

BOE: HF+ NH4F

4) SC-2: 금속성 오염물질 이온화

HCl

5) rinse and dry

Oxidation

반도체에 필요한 유전체나 절연체를 silicon과 산소/산소화합물의 결합으로 만드는 것으로 높은 온도의 챔버에서 SiO2막을 만드는 공정

- 건식산화

- 산소 gas를 주입하여 SiO2를 만드는 것

- 시간이 오래걸림

- 얇고 균일한 막을 만드는 데 사용됨

- 케패시터 유전체

- 습식산화

- H2O 수증기를 주입하여 SiO2를 만드는 것

- 시간이 짧게 걸림

- 많은 양의 막을 만드는 데 좋음

- 보호막, 절연막

건식산화 공정에서 발생하는 Dangling Bond와 그 대책을 설명하시오.

- Si와 O2가 만나게 되면 SiO2 막질이 만들어 지는데 Si와 Si02의 접합계면에서 단결정 Si은 공유 결합인 옥텟 규칙이 깨져 빈자리가 생기고 이상을

Dangling Bond라고 함 - 이 빈자리를 방치하게 되면 MOS 구조의 케페시턴스 특성이 나빠짐

(전자의 움직임을 방해함->mosfet의 성능에 영향을 끼침)- Dangling Bond에 의해 전계 전달력에 문제가 생김

- 이로 인해 Cox가 떨어지고 Vth가 높아지게 됨

- 이를 방지하기 위해 전자가 하나인 수소 가스 열처리로 빈자리를 없게 만듬

Photo

Photo 공정의 순서와 목적을 설명하시오.

photoresist: 빛에 민감한 물질로서 빛에 노출되었을 때 화학적 물리적 성질이 변함

- 용매인 solvent, 고형물인 resin, 광을 받으면 성질이 변하는 photo active compund(PAC)로 구성됨

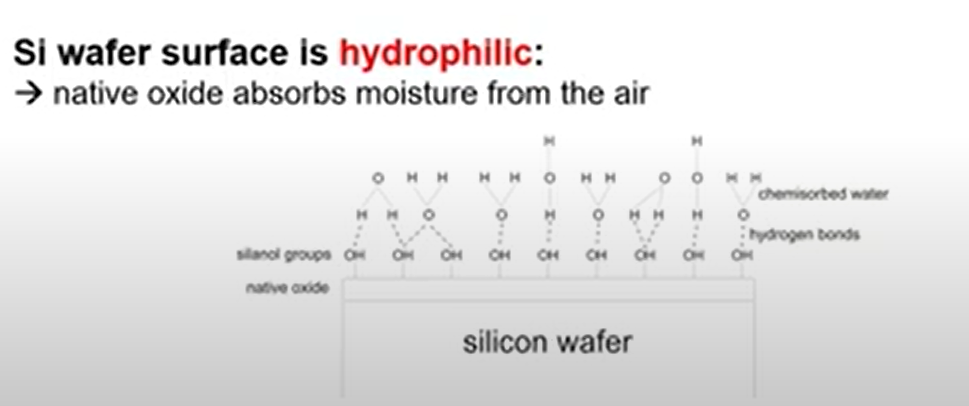

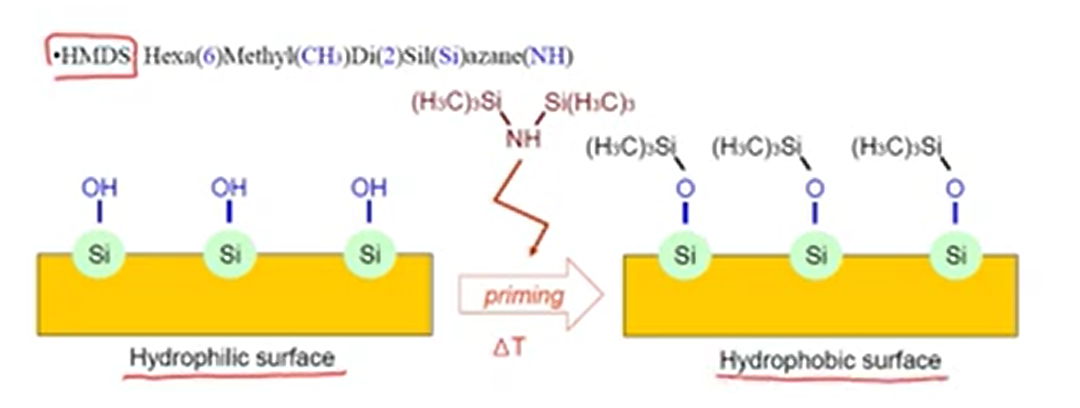

- HMDS 처리

- wafer 표면에 HMDS 분사를 통해 친수성인 웨이퍼 표면을 소수성으로 바꾸어 주어 웨이퍼와 PR의 접착력을 향상시킴

- native oxide가 생성되면 OH기가 공기 중 수분과 쉽게 결합하여 PR 코팅이 잘 안됨

- native oxide가 생성되면 OH기가 공기 중 수분과 쉽게 결합하여 PR 코팅이 잘 안됨

- PR Coating

- Spin coating 방식을 이용해 PR을 코팅함

- Soft Bake

- PR 내부의 솔벤트를 제거해 오염을 방지하고, 접착력을 좋게 함(오븐에 구움)

- Mask Align

- Align Key를 이용해 Mask를 이전 Layer와 정렬하는 것

- Exposure

- 노광은 마스크에 광을 통과시켜 PR 위에 패턴을 새기는 것

- 파장이 짧은 UV 사용

- PEB(post exposure baking)

- PR에 열을 가해 PR 성분을 재정렬시켜 Standing Wave 현상을 없애 해상도를 좋게 만들기 위함

- Develop

- 현상은 현상액을 뿌려 PR의 노광된 영역과 그렇지 않은 영역을 선택적으로 제거해 회로 패턴을 형성

- Hard Bake

- etching 과정을 견딜 수 있도록 단단하게 굳히는 과정

➡️ 파장이 짧은 빛을 사용하는 이유?

- 빛의 회절현상은 파장이 길면 길수록 퍼짐이 더 심해지기 때문에, 점점 더 짧은 파장의 광원을 이용하는 것이 회절현상을 극복하고 미세 패턴을 만들 수 있는 핵심기술!

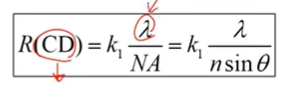

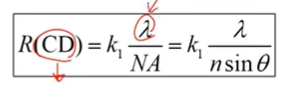

광의 Resolution과 DOF를 설명하시오.

resolution: mask pattern을 노광하였을 때 전사될 수 있는 최소 크기, 최소 선폭

- 값이 작을 수록 더 작은 선폭을 구현

Critical Dimension: 만들어낼 수 있는 최소한의 선폭

- 낮은 CD값을 얻기 위해선 더 짧은 파장의 빛을 사용해야 함

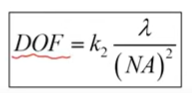

DOF(Depth of Focus): 초점을 맞출 수 있는 범위

- 그러나 짧은 파장은 DOF값을 낮춤

- 단차가 존재하는 경우에는 파장이 짧은 빛을 사용할 수 없음-> 평탄화의 중요성(CMP)⬆️

Phase Shift Mask를 설명하시오.

- 마스크를 통해 입사된 광이 회절현상으로 인해 인접한 구멍을 통해 입사한 광의 퍼진광과 서로 만나면 위상이 같아서 증폭되므로 미세 패턴을 구현할 수 없음

- phase shift 물질을 광이 통과할 자리에 선택적으로 발라주면, 광의 위상이 반전되어 다른 광과 중첩되더라도 간섭/상쇄되므로 원하는 패턴의 미세 패턴 구현이 가능하게 됨

이머전 ARF 기법을 설명하시오.

- 매질의 굴절률을 높이면 Resolution을 낮출 수 있음

- 공기보다 굴절률이 높은 물을 사용하면 193nm의 플루오린-아르곤 광원의 파장을 134nm까지 줄일 수 있어 더 미세한 회로를 그릴 수 있음

Photo 광원 ARF와 EUV에 대해 광원의 파장으로 설명하시오.

193nm 파장의 ArF 광원을 이용해 미세공정을 구현해왔고, 이에 이머전 방식으로 웨이퍼와 광이 나오는 렌즈 사이에 물을 넣어 굴절률을 높임으로서 더 미세한 패턴을 만드는 방법의 액침공정 기법을 사용함

하지만 이에 한계에 도달하여 13.5nm 파장의 EUV 설비를 사용하고 있음

Positive PR과 Negative PR의 차이를 설명하시오

PAC 성분이 광을 받은 성분이 파괴되어 광을 받지 않은 부분이 현상되는 Positive PR이 있고, 광을 받은 부분이 딱딱해져서 광을 받지 않은 부분을 현상하는 negative PR이 있음

➡️ 에칭공정이 힘들 때 주로 사용

노광장비의 Stepper와 Scanner 방식을 설명하시오.

Stepper: 한번에 광을 마스크와 렌즈를 통해 wafer에 노출시켜 원하는 패턴을 만드는 방법- 웨이퍼 영역마다 빛이 조사되는 정도가 달라 수율이 떨어짐

Scanner: 광을 한꺼번에 노광하는 것이 아니라 좁은 "선"으로 스캐닝하듯이 mask와 노광 장비가 움직이면서 노광하는 방법- 더 정밀한 CD와 Overlay 확보

Etching

Etch Rate, Selectivity, Uniformity를 설명하시오.

Etch Rate : 시잔에 따른 Etch량

Selectivity : etch를 해야하는 막질과 하부 막질과의 etch Rate의 차이

- wet 방식은 화학적 반응-> 높은 선택비

- dry 방식은 물리적 식각방식 -> 상대적으로 낮은 선택비

Uniformity : 패턴이 좁거나 넓은 영역에서 동일한 etch rate가 나오길 희망하는 수준

- etch가 많이 진행된 부분과 적게 진행된 부분의 차이를 합으로 나눈 항목

- 작을수록 좋음

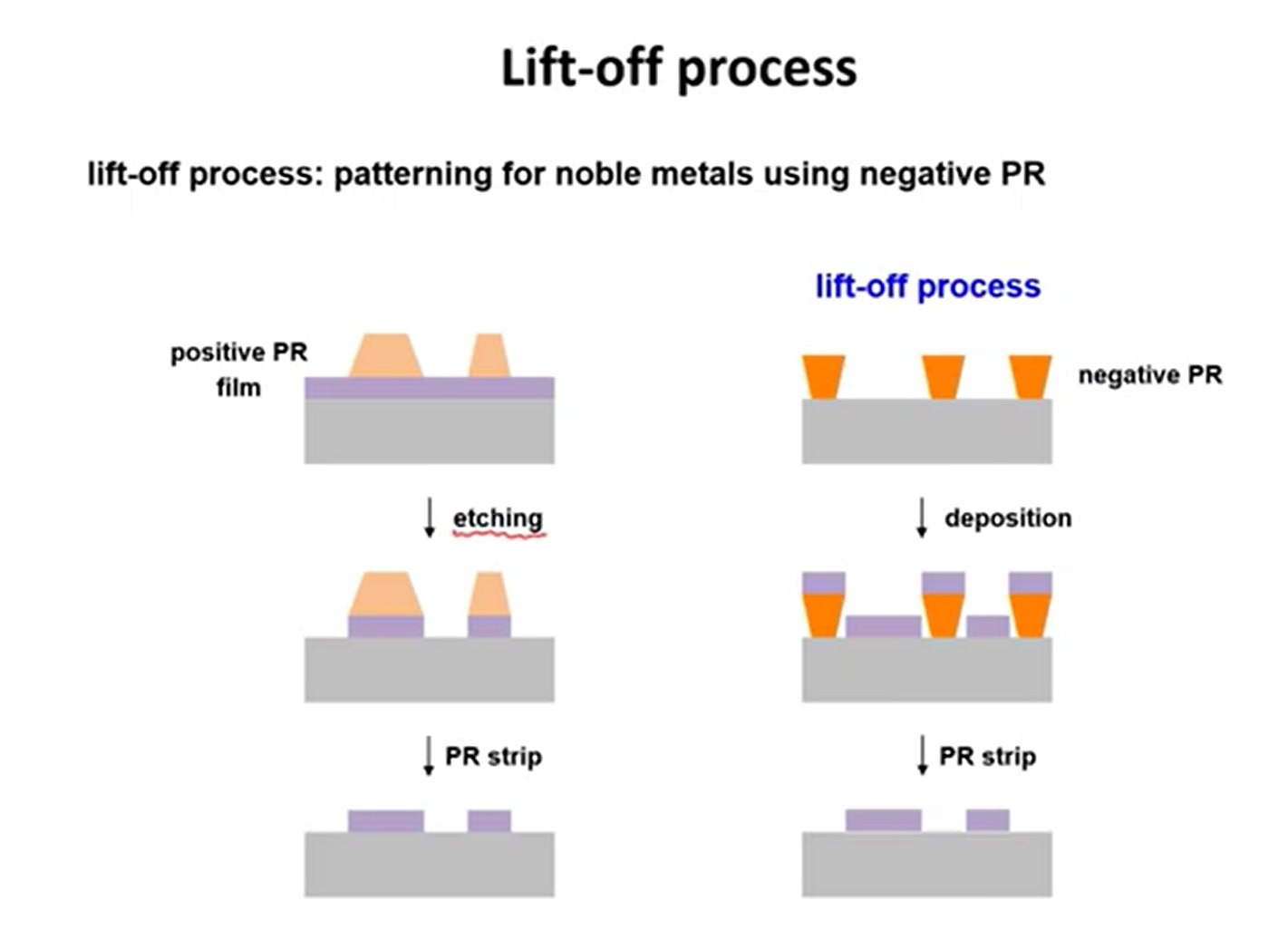

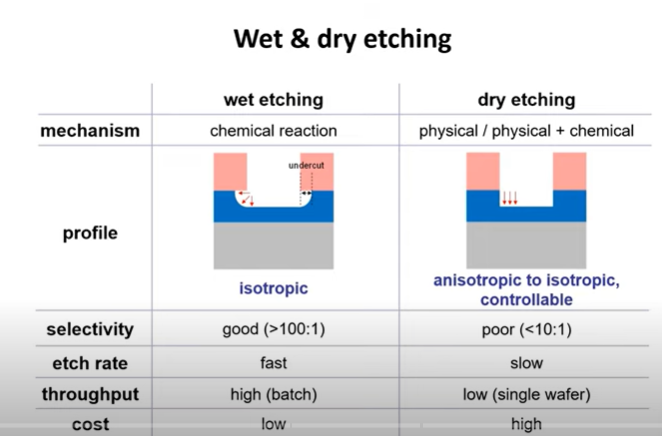

etching profile

isotropic: 방향에 상관없이 모두 일정한 etching rate를 가짐anisotropic: 수직 etch rate가 수평 etch rate보다 훨씬 큰 상황

etching bias: 원래 얻고자 했던 폭과 실제 etching 공정이 끝나고 얻은 폭의 차이

Wet Etch와 DRY Etch 비교 설명하시오.

Wet Etch

- chemical 용액으로 isotropic함

- etch rate, selectivity 좋음

- 정밀도 나쁨

- cost가 싸고 생산성이 좋음

Dry Etch

- 반응성 플라즈마 사용, anisotropic함

- 정밀도 좋음

- cost가 비싸고 생산성이 좋지 않음

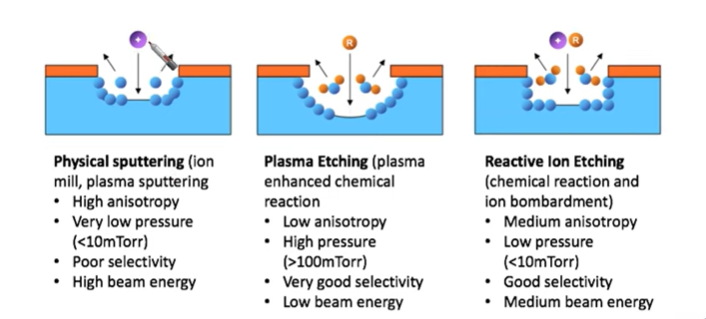

Plasma를 이용한 Dry Etch 방식의 종류를 설명하시오.

Physical sputtering

- 아르곤 원소를 플라즈마화시키고 아르곤 이온을 전압을 가해 가속시켜 이 에너지를 이용해 물리적인 충돌로 깎아내는 형식

- 낮은 진공도

- anisotropic

- 높은 전압 필요

- 선택비 낮음

plasma Etching

- 화합물을 플라즈화시키고 이온화된 화합물이 etching하기 원하는 film에 달라붙음, 화학적 반응을 통해 새로운 화합물이 생겨나고 이는 떨어져 나와서 가스와 함께 빠져나가는 방식

- isotropic

- 선택비 좋음

- 부산물이 휘발성을 가져야 함

Reactive ion Etching

-

플라즈화된 화합물과 가속된 이온을 동시에 이용,

가속된 이온들은 케미컬 반응성을 좋게 해주거나 결합에너지를 끓어내기 위한 추가적인 에너지를 제공 -

중간 정도의 진공

-

중간 정도의 anisotropic

Doping

실리콘에 불순물을 넣는 과정

- diffusion

- ion implantation

ion implantation

넣어주고 싶은 불순물을 이온화 한 후, 강한 전기장을 이용해서 가속시켜서 주입시키는 방식

이온주입 채널링 Effect를 설명하시오.

이온주입 입사각에 따라 doping 깊이가 달리는 것을 의미한다. 실리콘의 경우 7도 정도 기울여서 도핑을 진행한다.

이온주입 Annealing과 RTP를 설명하시오.

- 이온 주입 후 Silicon 격자는 이온주입에 의한 Damage를 받게 됨

- 열처리를 통해 silicon 격자를 원위치로 돌려 놓는 방식을

annealing이라고 함

RTP(Rapid Thermal Process)

- furnace보다 높은 수준의 온도를 이용

- wafer 표면에 열처리하는 방식으로 거의 1분 만에 끝남

Deposition

CVD와 PVD를 비교하여 설명하시오.

CVD(chemical Vapor Deposition)

- 화학반응을 이용하여 박막을 증착하는 방법

- 두께의 컨트롤이 가능

- uniformity 좋음

- 부산물이 발생하므로 오염측면에서는 불리

PVD(Physical Vapor Deposition)

- 물리적 힘에 의한 증착

- sputtering, evaporation 등

- 두께조절 어려움

- 금속물질의 증착에 많이 이용됨

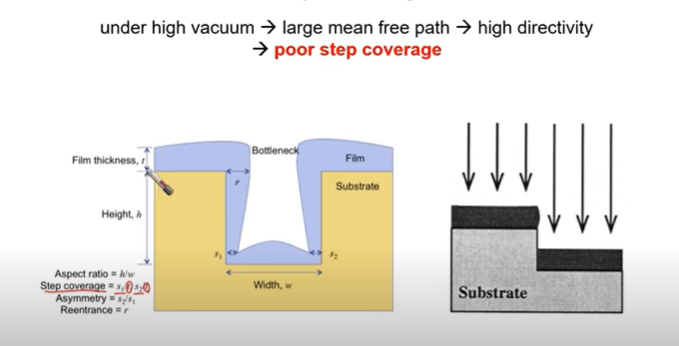

Mean Free Path의 정의를 설명하시오.

- 분자나 금속 내 자유전자가 다른 입자와 충돌하지 않고 움직이는 평균적인 거리

- 따라서 입자가 mean free path만큼 나아가면 평균적으로 1회 충돌한다고 볼 수 있음

- 온도MFP가 커지면 박막의 증착이 더 균일

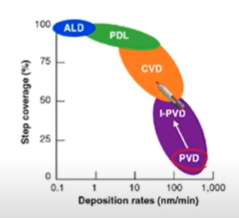

Stemp Coverage의 정의를 설명하시오.

- 박막의 증착 균일도를 표현하는 지표

- 평평한 곳에서의 두께와 측면의 두께의 비율

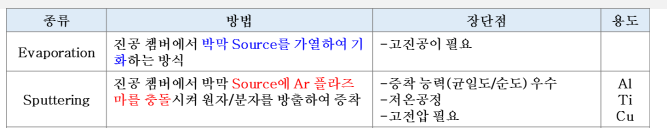

PVD 종류와 Sputtering 방식을 설명하시오.

evaporation

- 진공의 챔버에서 가열하여 증발한 금속물질이 증착되는 방식

- uniformity 매우 낮음

- 높은 진공도 요구

- 매우 높은 직진성을 가져 측벽에는 증착이 잘 안돼 step coverage가 안좋음 ➡️ waper를 회전시키면서 증착

- litf-off process에 적합

Sputtering

- 아르곤을 플라즈마화 하여, 이 이온을 금속소스에 충돌시킨뒤 튕겨져 나오는 금속 소스를 증착하는 방식➡️ dry etching과 유사

- uniformity 좋음

- 금속물질 이외에도 다양한 물질 증착 가능

- step coverage가 좋음

- 낮은 진공 요구 -> 불순물의 위험

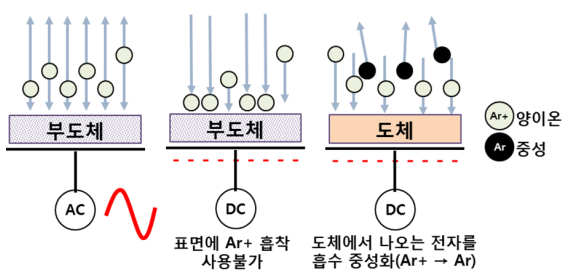

DC Sputter와 RF Sputter 방식을 비교 설명하시오.

DC Sputter

- 플라즈마의 Ar+이온이 DC (-)전압에 의해 가속하여 충돌하고, 금속원자가 충돌에 의해 빠져나와 기판에 증착

- Ar+ 이온은 충돌 후 금속에서 튕겨 나온 전자와 결합하여 중성이 되어 DC(-) 전압에 반응하지 않음

- 부도체 물질의 경우 충돌하더라도 전자가 나오지 않으므로 Ar+는 DC(-)에 의해 잡혀 부도체 물질 위에 쌓이고 이후 Ar+ 충돌 방해

RF(radio frequency) Sputter - 부도체의 증착에 이용됨

- RF를 이용하면 고주파 AC로 전환되는 전원에 의해 Ar+ 이온을 상하 운동시키므로 부도체 위에 Ar+ 이온이 뭉쳐 쌓이지 않음

CVD 메커니즘을 설명하시오.

- 전구체를 포함하는 반응기체들이 챔버 내로 유입되고, 박막증착 표면으로 이 기체들이 확산하고 흡착되면서, 기체들간의 화학반응으로 인해 박막이 증착되는 방식

- 화학 반응에 의한 부산물은 가스 상태로 휘발되어 뽑아냄

AP/LP/PECVD 방식과 특징을 비교하여 설명하시오.

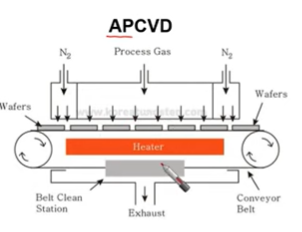

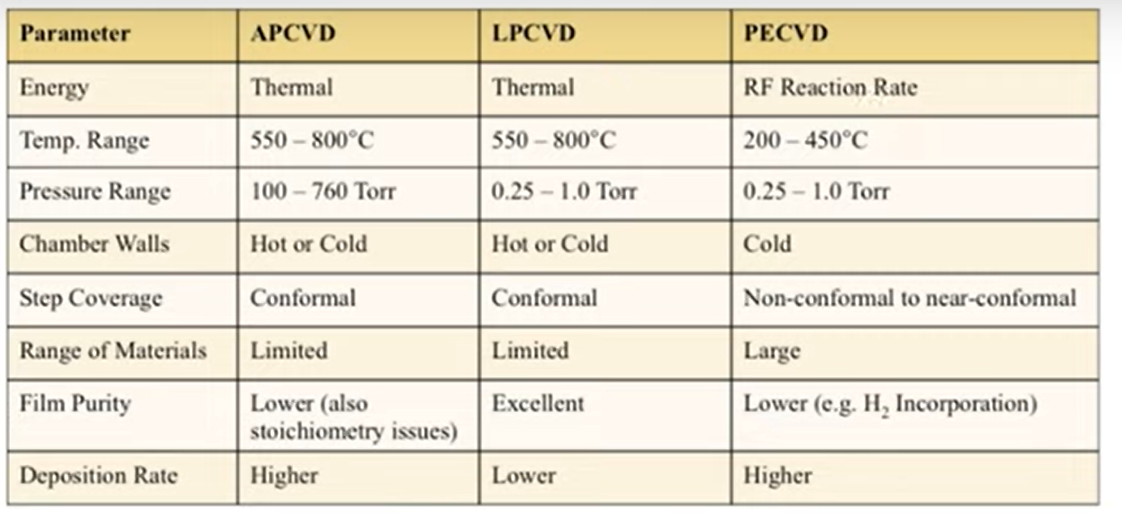

APCVD(Atmosphere Pressure)

- 반응기내 압력이 대기압과 같은 수준에서 박막 증착 방식

- 박막의 오염의 우려가 있음

- Step coverage 좋지 않음

- deposition rate 낮음

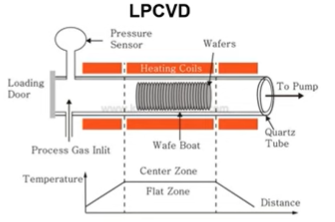

LPCVD(Low Pressure)

- 저압 챔버에서 박막 증착하는 방식

- 순도와 step coverage 좋음

- 고온공정으로 공정속도가 느림

- film quailty가 중요할 때 사용

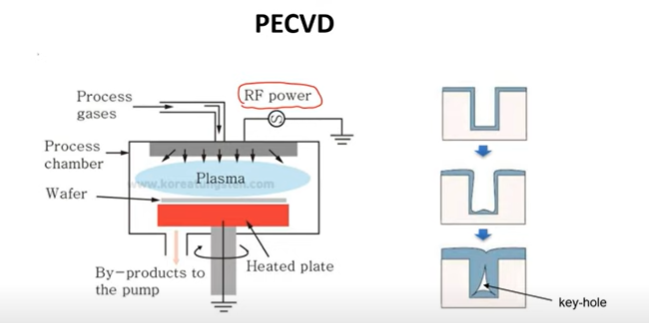

PECVD(Plasma Enhanced CVD)

- 반응기내 전기장을 이용한 Plasma를 만들어, 플라즈마의 도움을 받아 박막을 증착하는 방식

- 저온 공정

- 대량 처리 불가능

- deposition rate 좋음

- 고온증착이 불가능할 때 사용

ALD 방식을 설명하시오.

- Atomic Layer Decomposition, 원자층 한층 한층의 박막을 증착하는 기법

- 반응기체를 넣어 한 층만의 물질이 흡착된 상태에서 잔류 가스를 빼고, 두 번째 반응기체를 넣고 같은 절차를 반복

- 박막의 두께를 정확하게 컨트롤 가능

- step coverage 매우 좋음

- 저온에서 증착 가능

- 거의 대부분의 물질 증착 가능

Metalization

수많은 transistor들을 서로를 연결해서 회로를 만들고 이런 회로들을 연결하는 공정

contact: 서로 다른 물질들의 접합면, 이 부분에서 전기적 신호가 들어가고 나감

interconnection : contact들을 연결한 line

metalization : interconnection을 만드는 공정

IMD(inter metal dielectric) :metal 층 사이의 절연층

via : metal층 사이의 전기적 연결 부위

Al 사용한 이유

- 비싸지 않음

- si, sio2에 대한 adhesion이 좋음

- patterning이 쉬움

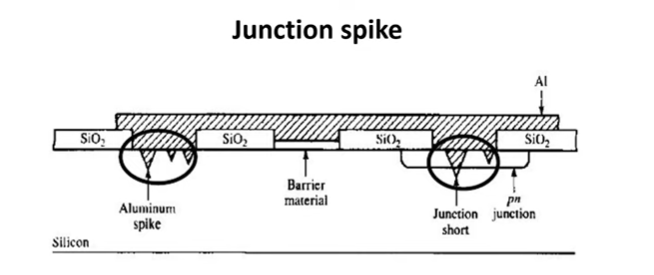

Al 배선의 Junction Spike에 대해 설명하시오.

(공융점)

- si과 al의 contact 저항을 줄이기 위해 annealing 작업 진행

- 공융 현상에 의해 녹는점이 577도 밖에 안되는 비율이 존재함

- Al이 Si을 침투하여 녹이면서 톱니처럼 파고 드는 문제

- 심할 경우 깊숙하게 파고 들어 전기적인 문제를 일으킴

- barrier layer 삽입 -> 저항을 증가시키는 단점

- Al에 Si 성분을 1% 포함하여 증착하면 녹는점이 올라가 해결할 수 있음

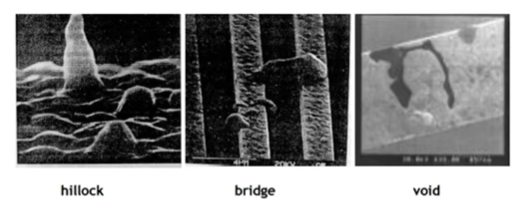

Elecro Migration을 설명하시오.

- Al interconnection에 높은 전류가 흐르면, 전자가 가진 운동량이 커 Al을 실제로 이동시키는 형상

- 밀려나간 금속 원자가 빠져나간 곳은 점점 비워져 void 발생

- 빠져나간 금속원자들이 특정 부분에 모여 쌓이게 되어 Hillock 구조 형성

- Cu와 같이 무거운 금속을 소량 섞어 해결

Metal에 Cu를 적용하는 장점을 설명하시오.

- 공정 미세화로 인해 소자의 크기가 줄고 개수도 급증하고 있음

- 낮은 비저항을 가져 집적도의 증가와 신호지연의 감소를 통한 소자 성능 향상

- Dry etch가 불가능해 Damascene 공정을 이용하며, CMP란 공정을 수반

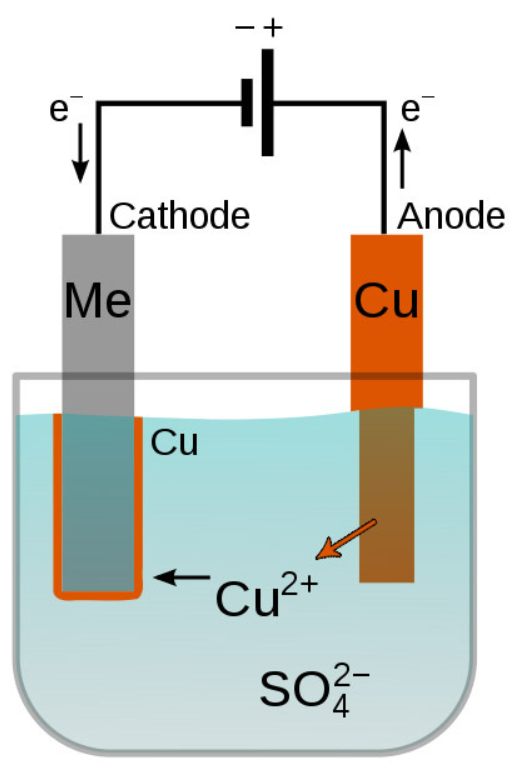

Cu의 electroplating을 설명하시오.

- 구리 이온이 들어 있는 전해질 용액(ex.CuSO4)

- 도금할 금속에 (-)극, 구리 금속(+)극을 연결시킴

- 전원을 키면 전자가 도금할 금속으로 이동

- 구리 이온은 도금할 금속 표면에 도달한 전자를 받아 Cu 금속으로 환원됨

Cu2+(aq) + 2e- ->Cu(s) - 구리가 환원되면, 전해질 용액의 전하 균형을 맞추기 위해 구리 금속이 전해질 용액에 구리 이온 공급

Cu(s) -> Cu2+(aq) + 2e-

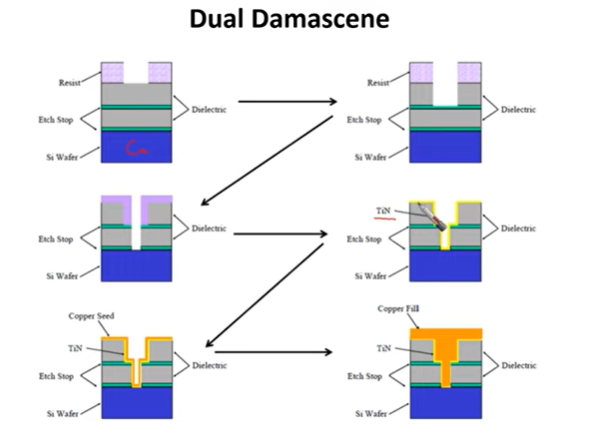

Cu Damascene의 목적과 Dual Damascene 방법을 설명하시오.

구리의 패터닝을 구리를 식각하는 기법이 아니라. 미리 구리의 패턴을 만들 영역을 포토와 식각으로 만들어 놓고, 구리를 채운 후 상부를 연마하는 방식

- 절연물질을 패터닝 공정을 통해 홈을 형성

- barrier layer(metal) 증착

- 금속원자의 절연막으로 오염을 막기위한 확산방지 막

- 금속과 절연막의 접착력을 향상시킴

- Cu seed 증착

- 전기를 흘려줄 수 있는 path 역할

- electroplating 진행

- CMP 공정

PVD: step coverage가 매우 낮음

ALD: 생산성이 낮음

CVD: gap을 완전히 채워도 seam이 남음

Dual Damascene

- single은 배선의 메탈과 배선을 연결하는 Via를 각각 제작

- 메탈과 via를 일체형으로 만드는 것이 공정측면에 유리

- 구리가 들어갈 영역을 포토/에칭, 포트/에칭 연속 2회 실시 후 cu를 한번에 채워 만드는 것을 의미

CMP(Chemical Mechanical Polishing)

막질을 화학적/물리적으로 연마하는 공정으로, 막질을 균일하게 만드는 공정

- 막질들이 증착 후 단차가 발생하면 후속 공정에서 불량이 발생할 수 있음

- 짧은 파장의 빛을 사용하므로 DOF가 매우 좁음

Wafer에 굴곡이 있을 경우 패터닝이 잘 안되므로 모든 영역에서 초점이 잘 맞을 수 있게 평탄화 작업 필요 - Damaecene process에서 필요함

- dishing ,erosion 문제 발생