Counter, Shift Register

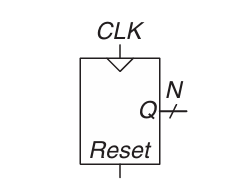

Counter

clock과 reset을 input으로 받고 -bit output Q를 내보내는 sequential arithmetic circuit이다.

매 clock edge마다 출력이 증가한다.

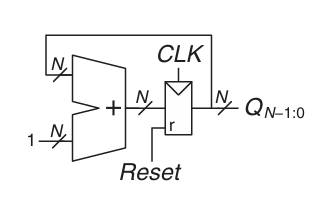

-bit counter는 reset가능한 레지스터와 adder로 구성된다.

매 cycle마다 counter는 레지스터에 저장된 값에 1을 더한다.

컴퓨터의 Program Counter(PC)에도 사용된다.

-bit counter의 msb는 사이클마다 토글된다. 필요에 따라 clock cycle을 으로 나누어 cycle을 느리게 만들 수 있다.

예를들어, 내장 clock이 50MHz인 시스템에 24-bit counter로 신호를 만들어 LED가 깜빡이는 정도를 인간의 눈으로 볼 수 있게 만들 수 있다.

Counter를 이용해 임의의 주파수를 생성하는 장치를 DCO(Digitally Controlled Oscillator)라고 한다.

매 cycle마다 1 대신 를 더하는 -bit counter가 있다고 하자.

이로 인해 발생하는 주파수는 이다.

예제. 인 clock이 있다. 주파수를 signal로 바꿔라.

-

일 경우, ,

-

일 경우, ,

이 커질 수록 더 정밀한 제어가 가능하지만 그만큼 하드웨어를 더 많이 사용한다.

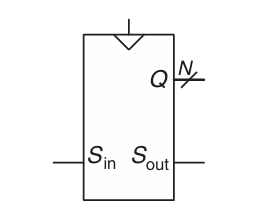

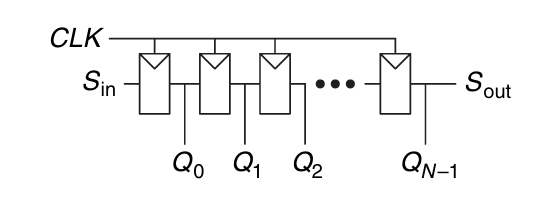

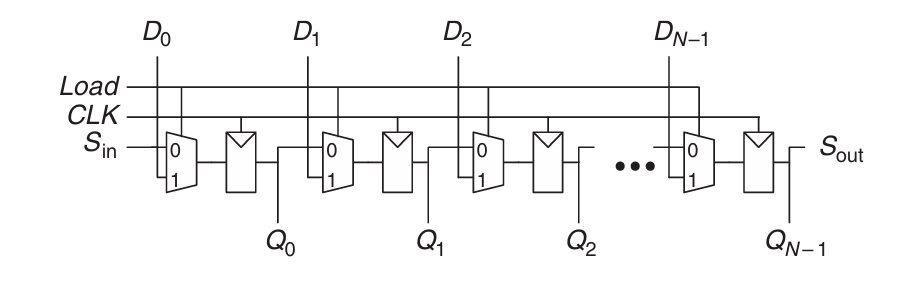

Shift Register

매 clock edge마다 새로운 bit를 shift in/out 한다.

Shift Register는 직렬 입력을 병렬 출력로 변환할 수 있다.

Load 신호가 1일 때는 일반적인 -bit 레지스터지만, Load 신호가 0이 되면 Shift Register로써 수행된다.

과 의 serial-to-parallel converter로도 사용이 가능하고 과 의 parallel-to-serial converter로도 사용이 가능하다.

<참고자료>

Harris & Harris, Digital Design and Computer Architecture, RISC-V Edition, 2022.