페이징 Paging - 보호 (Protection)

페이징 관경에서 메모리 보호는 각 페이지에 붙어있는 보호 비트에 의해 구현된다. 이 비트는 페이지 테이블 내에 존재한다.

각 페이지는 읽기, 쓰기, 읽기 전용임을 각각 정의할 수 있다. 메모리에 대한 모든 접근은 페이지 테이블을 거치므로, 이때 주소 변환과 함께 이 페이지에 쓰기가 허용되는지 안되는지와 같은 검사를 할 수 있다. 읽기 전용 페이지에 관해 쓰기를 시도하면 운영체제가 하드웨어로 트랩(memory protection violation)을 발생시킨다.

페이지 엔트리의 유효비트

페이지 테이블 엔트리는 유효/무효(valid, invalid) 비트라는 하나의 비트가 더 있다. 이 비트가 유효로 설정되면 페이지가 프로세스에 해당되고 있음을 나타내고, 무효라면 해당 페이지는 프로세스의 논리 주소 공간에 속하지 않음을 나타낸다.

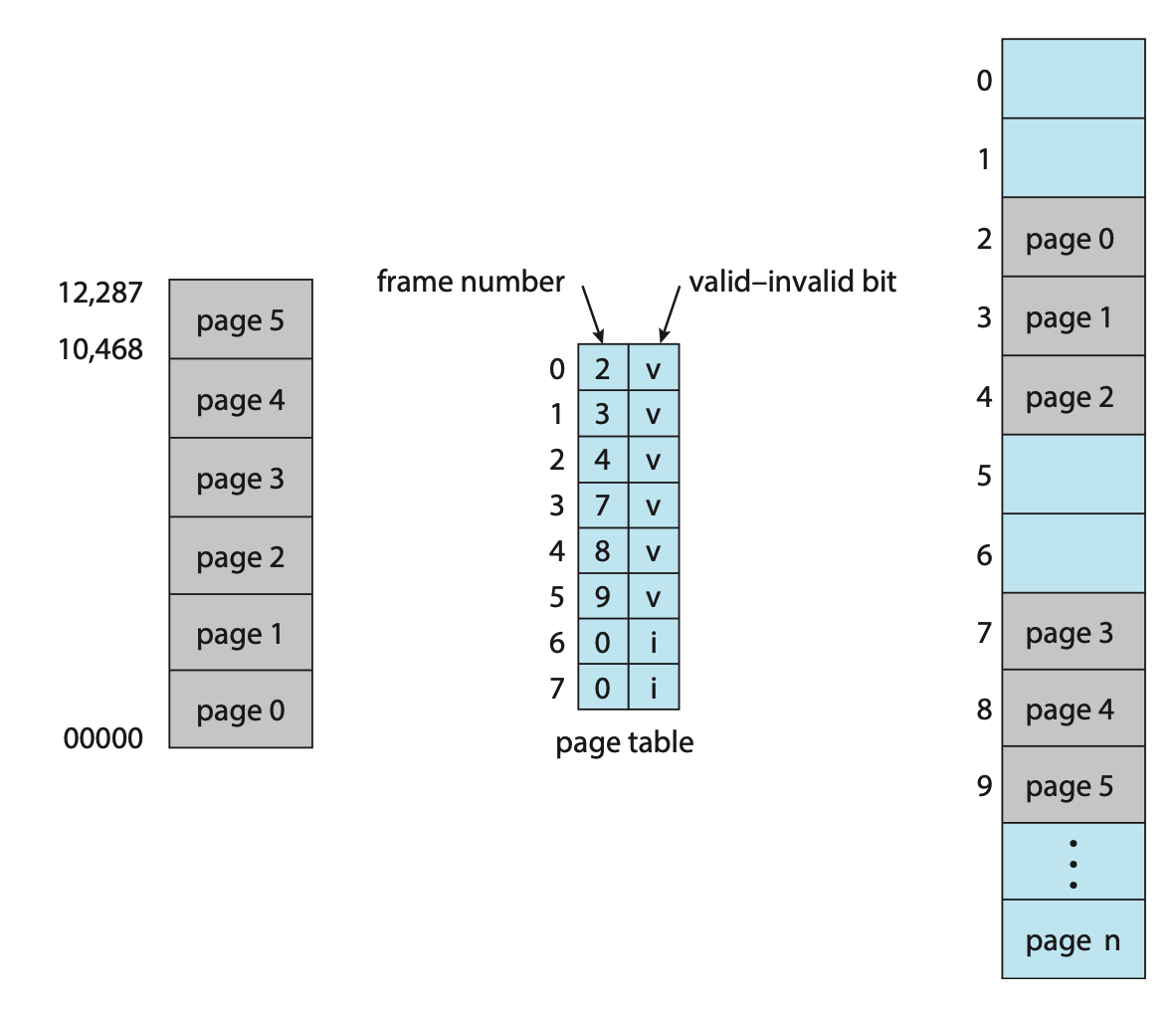

예를 들어 14비트 주소 공간을 갖는 시스템이 있다. 해당 시스템은 0~10468의 주소만을 사용할 수 있다. 페이지 크기가 2KB일때 아래와 같은 상황이 된다.

이때 0,1,2,3,4,5의 주소는 페이지 테이블에 정상적으로 맵핑이 된다. 하지만 페이지 6,7에서 주소를 맵핑하려 시도하면, 비트가 무효로 설정된 것을 발견하여 트랩을 발생시킨다.

페이지 테이블 길이 레지스터 PTLR (Page Table Length Register)

프로세스가 자신의 모든 주소 범위를 사용하는 경우는 매우 드물다. 이런 경우에 모든 페이지에 테이블 항목을 배정하는 것은 낭비이다. 몇몇 시스템은 페이지 테이블 크기를 나타내기 위해 PTLR라는 레지스터를 제공한다. 프로세스가 제시한 주소가 유효 범위 내에 있는지 확인하기 위해 모든 논리 주소 값이 PTLR 값과 비교 된다. 이러한 검사에서 오류가 나타나면 트랩을 발생시킨다.