페이징 Paging - 하드웨어 지원

페이지 테이블은 프로세스별 자료구조이며 페이지 테이블에 대한 포인터는 각자의 PCB에 저장된다. CPU 스케쥴러가 실행할 프로세스를 선택하면 PCB에 저장된 레지스터값을 적재한 후 페이지 테이블에 값에 저장된 사용자 페이지 테이블로부터 적절한 하드웨어 페이지 테이블값을 적재해야한다.

페이지 테이블의 하드웨어 구현

페이지 테이블은 전용 고속 하드웨어 레지스터 세트로 구현되므로 페이지 주소 변환이 매우 효율적이다.그러나 이러한 접근 방식은 각각의 레지스터가 문맥 교환 중에 교체되어야 하므로 문맥 교환 시간을 증가시킨다.

페이지 테이블에 레지스터를 사용하는 것은 페이지 테이블이 작은 경우 적합하다. 대부분 현대 CPU는 훨씬 큰 페이지 테이블을 지원한다.(예를 들어 2^20개 항목을 가지는 테이블) 이러한 컴퓨터들의 페이지 테이블을 구현하기 위해서 위처럼 빠른 레지스터를 사용하는것은 부적절하다.

(예를 들어 빠른 레지스터로 사용한다는것은 어떠한 메모리 저장장치가 있고 그 저장 장치마다 페이지 테이블에 대한 주소를 적재한 후 사용한다는 것이다.)

따라서 대부분의 컴퓨터는 페이지 테이블을 메인 메모리에 저장하고 페이지 테이블 기준 레지스터(PTBR) 로 페이지 테이블을 가르키도록 한다. 다른 페이지 테이블을 사용하려면 이 레지스터만을 변화시키면 되고 문맥시간을 줄일 수 있다.

TLB

위에서 큰 페이지 테이블로 인해 레지스터에 저장하는것이 아닌 메인 메모리에 저장하기로 설명했다. 그러면 메모리 구조를 한번 생각해보자.

페이지 테이블 자료를 레지스터에 저장하는 경우

- CPU는 논리 주소를 요청한다.

- MMU는 레지스터에서 논리 주소에 해당하는 relocation register 값과 limit register 값을 가져 온다.

- MMU는 경계값 조건을 확인 후 올바른 물리주소를 반환한다.

- 물리 주소에 해당하는 메모리에 접근한다.

위 과정에서 우리는 CPU -> 레지스터 -> 메인 메모리 라는 순서로 요청하는것을 알 수 있다.

페이지 테이블 자료를 메인 메모리에 저장하는 경우

- CPU는 논리 주소를 요청한다.

- MMU는 프로세스가 가지고 있는 PTBR의 값과 요청된 논리 주소의 페이지 번호를 더하여 해당 메모리에 접근한다. (이 주소는 페이지 테이블의 프레임 시작 주소를 가지고 있다.)

- 해당 메모리에 있는 프레임 시작 주소, PCB에 있는 limit register, 논리 주소를 MMU로 전달한다.

- MMU는 경계값 조건을 확인 후 올바른 물리주소를 반환한다.

- 물리 주소에 해당하는 메모리에 접근한다.

위 과정에서 우리는 CPU -> 메인 메모리 -> MMU -> 메인 메모리 라는 순서로 요청하는것을 알 수 있다.

문제점

페이지 테이블 자료를 레지스터로 사용할때와 메인 메모리를 사용할때의 차이점은 메인 메모리에 접근하는 횟수이다. 메인 메모리 저장 방법의 경우 메인 메모리를 2번 접근하게 되면서 레지스터 저장 방법에 비해 2배의 시간이 소모 된다. 이러한 문제점을 해결하기 위해 우리는 TLB (Translation lookaside buffer)라는 캐시를 둔다.

TLB 란?

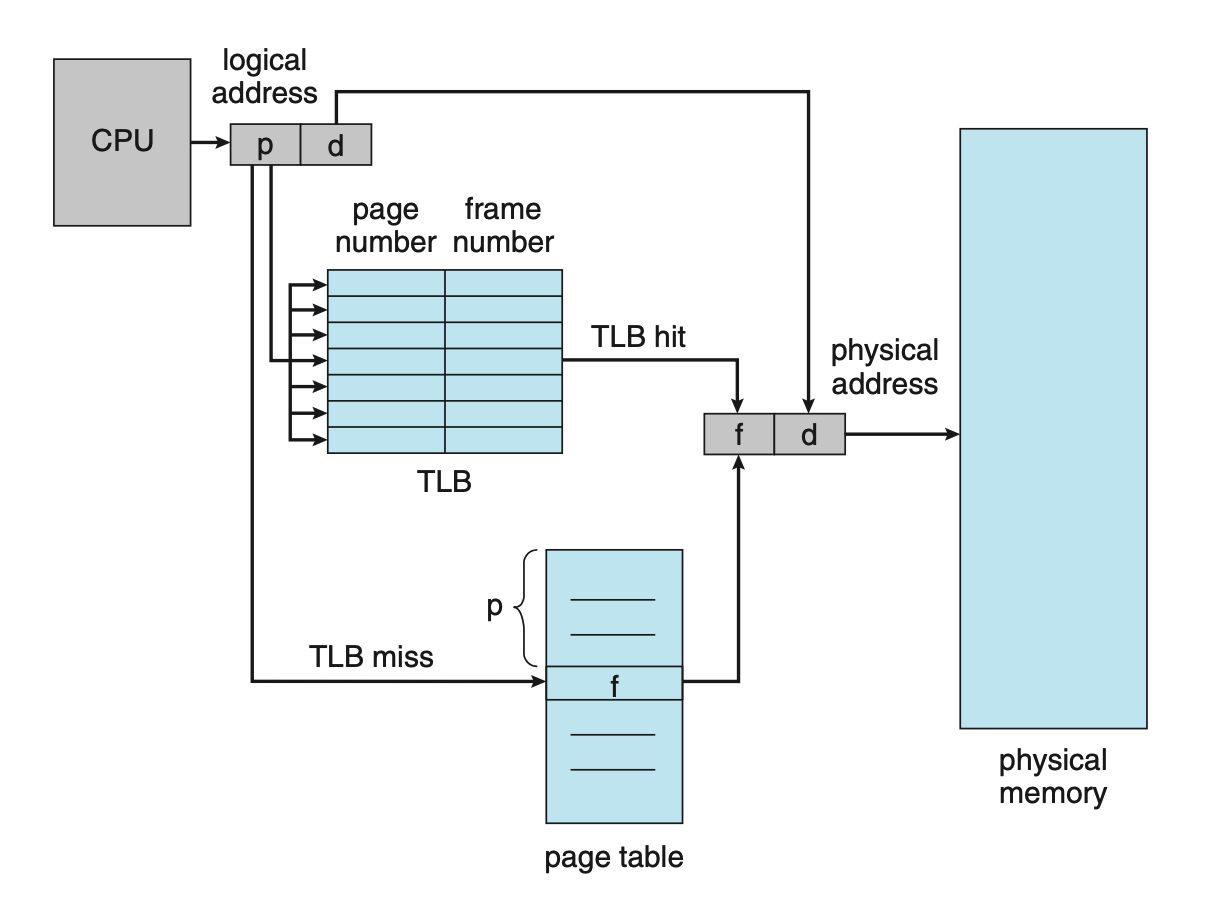

TLB는 key, value로 구성되며 페이지 번호르 프레임 번호로 바로 전환해준다. TLB는 Fully Associative 방식을 사용한다. 간단하게 원하는 곳에 원하는 데이터를 저장할 수 있다. 조회시에는 모든 블럭을 조회한다. 이러한 방식 때문에 너무 큰 크기의 캐시는 성능상 문제가 생기므로 작은 크기를 사용할 수 밖에 없다.

이 TLB는 CPU가 주소를 요청했을때 MMU는 페이지 번호가 TLB에 있는지 확인한다. 발견 된다면 해당 프레임 번호를 즉시 반환한다. 없다면 페이지 테이블을 접근하여 프레임 번호를 찾아 온 후 TLB에 저장한다. TLB가 가득 찼을때는 여러가지 교체 정책으로 구현될 수 있다.

어떠한 TLB는 각 항목에 ASIDs(Address-space identifiers)를 저장하기도 한다. ASID는 그 TLB 항목이 어느 프로세스에 속한 것인지 알려주며, 해당 프로세서의 정보를 보호하기 위해 사용된다. TLB에서 가상 주소를 변환할 때 현재 수행 중인 프로세스의 ASID와 같은지 검사한다. ASID가 맞지 않으면 TLB miss로 간주한다. ASID 지원이 있으면 한 TLB 안에 여러 프로세스 정보를 동시에 보관할 수 있다. ASID 지원이 없다면 새로운 페이지 테이블이 선택될 때 마다 다음 실행 프로세스가 잘 못 변환하지 않도록 하기 위해 TLB는 전부 플러시 되어야한다. 이유로는 그전 프로세스가 실행하던 페이지 번호와 프레임 번호가 남아있기 때문이다.

현대의 TLB

현대의 TLB는 여러 단계를 가지고 있다. 상위 TLB에서 miss가 나면 좀더 크기가 큰 하위 TLB에서 확인하게 된다. 하위 TLB에서도 miss가 나면 메인 메모리에 접근하여 찾게 된다.

정리

가장 중요한점은 TLB의 사용이유와 TLB 적중률이다. TLB의 적중률이 낮고 조회 시간이 메인 메모리에 접근하는 시간보다 적지 않다면 사용하는 의미가 없어진다.

TLB는 운영체제에 영향을 주지 않을것 같지만 하드웨어 플랫폼에 따라 최적의 동작을 하기 위해 그에 따른 페이징 설계가 필요하다.