Memory Hierarchy 2(메모리 계층구조)

메모리 상단부의 Cache memory에 대해 알아보자!

2. Basics of cache

-Direct mapped cache operation

-Handling cache misses

-Write Policy

Cache를 바라볼 때, 우리가 궁금해 하는 점이 두 가지 정도가 있다.

- 우리가 원하는 데이터가 캐시 내에 존재하는 지 어떻게 알 수 있는가?

-> 만약 없다면 lower level로 가서 가져와야 한다. - 데이터가 있다면, 캐시의 어느 위치에 데이터가 있는 지 확인하고 가져올 수 있는가?

우선 캐시가 하드웨어적으로 어떻게 구성되어 있는 지 확인해보자.

크게 세 가지로

1) Direct Mapped

2) Fully Associative

3) N-way Set Associative

가 있다.

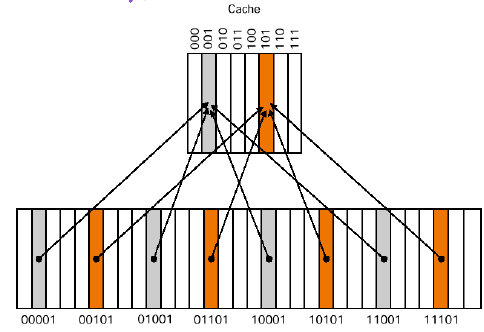

Direct Mapped

메인 메모리는 32

캐시는 8의 용량을 가지고 있다고 하자.

(8개의 block을 가지기에 log2(8)=3 (세 자리))

여기서 modulo연산을 사용한다.

메인메모리의 22번지에 데이터가 있다면, 8개의 공간 중 어디에 매핑시킬 지 이 modulo를 통해 계산한다.

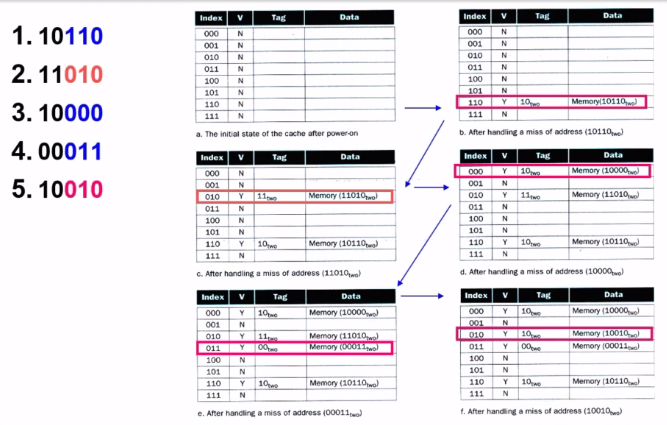

ex) 현재 Cache는 빈 상태

22 mod8 -> 6

: 캐시 메모리의 index 6 자리에 22주소의 데이터를 넣는다.

이렇게 되면 위치를 빠르게 찾을 수 있다는 장점이 생긴다!

하지만 문제가 발생하는데, 여기서 메인메모리의 몇 개의 주소가 캐시의 한 공간에 매핑이 되어 버리는 현상이 발생해 버린다.

=> 메인메모리의 어느 부분에서 온 데이터인지 모른다!

따라서 이를 해결해야 하는데, 우선 두 가지를 고려해 보자.

1) 캐시에 유효한 데이터가 존재하는가?

-> Valid bit (1or0)

2) 그렇다면 어디에서 온 데이터 인가?

-> Tag (00 01 10 11)

Direct Mapped Cache Example

여기서 추가로 10010을 읽고 싶다면, 110에 Y고 Tag10이 맞으니 hit로 이 데이터를 그대로 읽어가면 되는 것이다!

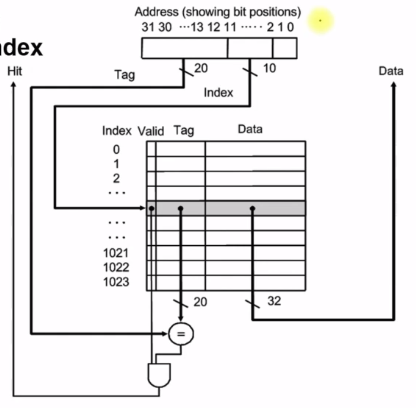

그렇다면 실제 하드웨어적으로 구조를 살펴보자.

주소는 MIPS이기에 32비트이고, 이 중 1)Tag관련 2)index관련 3)byte offset으로 구성되어 있다.

예시로 그림과 같이 1024개의 캐시가 존재한다면, 주로 캐시의 인덱스 크기는 log2를 취한 값을 가지기에 10비트가 할당됨을 확인할 수 있다.

데이터는 32비트로 4바이트이다. 따라서 이 4바이트 중 어떤 정보에 접근할 지 또한 정해줘야 하는데, 이를 byte offset을 통해 결정한다. 데이터가 4바이트이기에 2비트로 할당되어 있다.

마지막으로 Tag관련 비트는 32-(index bit + 2)로 여기서는 20으로 할당된다.