📖캐시 메모리

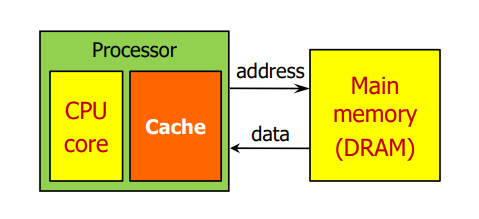

캐시 메모리(cache memory)는 속도가 빠른 장치와 느린 장치 사이에서 속도 차에 따른 병목 현상을 줄이기 위한 범용 메모리이다.

대표적으로, 속도가 빠른 CPU 코어와 속도가 느린 메모리 사이에서 속도 차에 따른 병목 현상을 완화하는 역할을 한다. CPU는 메모리에 저장된 데이터를 읽어오는데, 자주 사용하는 데이터를 캐시 메모리에 저장하면 그 데이터를 다시 사용할 때는 메모리가 아닌 캐시 메모리에서 데이터를 읽어올 수 있다.

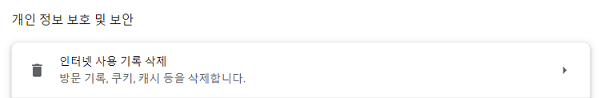

이외에 인터넷에서도 웹 브라우저를 보면 캐시라는 단어를 볼 수 있다. 이때의 캐시는 웹 페이지 상의 이미지 등을 하드디스크에 미리 저장해 두고, 웹 페이지를 재방문했을 때 사이트가 아닌 하드디스크에서 이미지를 불러들여 로딩 속도를 높이는 역할을 한다. 즉, 속도가 빠른 하드디스크와 속도가 느린 웹 페이지 사이에서 병목 현상을 완화하는 것이다.

📁캐시 메모리의 level

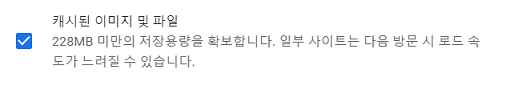

CPU에서는 캐시 메모리가 2~3개 정도 사용되며, 각각을 level로 분류한다. 다음은 Intel의 Core 2 Duo 모델에 대한 캐시 메모리를 나타낸 것이다.

각 CPU 코어마다 독립된 L1 캐시 메모리를 가지고 있는데, 특정 코어만을 위해 사용되는 캐시를 private cache라고 한다. 즉, 여기서 L1 캐시는 private cache이고, 물리적으로 DL1 캐시와 IL1 캐시로 나뉘어져있다. DL1 캐시에는 데이터가 저장되고, IL1 캐시에는 명령어가 저장되어 시간적으로 instruction fetch와 memory access가 겹쳐도(구조 해저드) 진행 가능하다. 이외에 두 코어가 공유하는 L2 캐시 메모리(shared cache)가 있다.

캐시 메모리의 level은 속도와 크기에 따라 분류한 것으로, L1 캐시는 일반적으로 CPU 칩 안에 내장되어 가장 빠르게 접근 가능하다. L1 캐시에서 먼저 데이터를 찾고, 찾지 못하면 L2 캐시로 넘어간다.

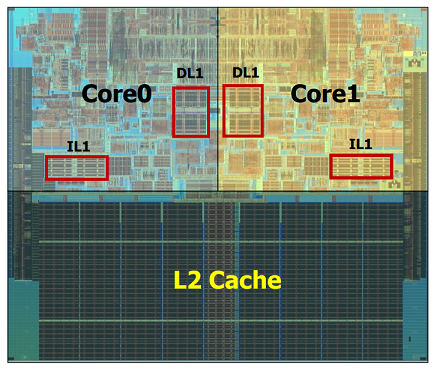

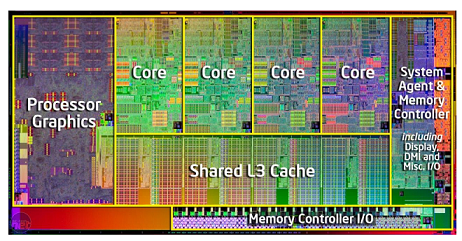

다음은 Core i7 2세대 모델에 대한 캐시 메모리를 나타낸 것이다.

코어 4개가 각각의 L1 캐시와 L2 캐시를 갖고 private하게 사용하며, L3 캐시를 공유한다.

이렇게 주로 마지막 레벨에 해당되는 캐시는 커다랗고 각 코어가 공유할 수 있는 구조로 만든다.

📁지역성의 원리

캐시 메모리는 메인 메모리에 비해 작은 크기의 메모리이다. 메인 메모리에 저장된 많은 데이터 중, CPU가 자주 사용할 것이라고 생각되는 일부의 데이터를 캐시 메모리에 저장하는 것이다. 이때, 캐시 메모리는 지역성의 원리(principle of locality)를 이용한다.

-

시간 지역성(Temporal locality, locality in time)

한 번 참조된 데이터는 잠시 후에 또 참조될 가능성이 높다(Ex. for문, while문 등의 반복문) -

공간 지역성(Spatial locality, locality in space)

참조된 데이터 근처에 있는 데이터가 잠시 후에 사용될 가능성이 높다(Ex. A[0], A[1]과 같은 데이터 배열에 연속으로 접근)

📁캐시 메모리 관련 용어

-

Block(또는 (cache) line) : 캐시 메모리와 메인 메모리 사이 주고받는 데이터의 단위(일반적으로 64byte)

-

Hit : CPU가 읽어오려고 하는 데이터가 캐시에 있는 경우

- Hit rate : CPU가 요청한 데이터 중 캐시에 저장된 비율

- Hit time : 캐시에서 데이터를 읽어오는 데 필요한 시간

-

Miss : CPU가 읽어오려고 하는 데이터가 캐시에 없는 경우

- Miss rate : CPU가 요청한 데이터 중 캐시에 저장되지 않은 비율

(= 1 - Hit rate) - Miss penalty : miss가 발생해 데이터를 block만큼 메인 메모리에서 캐시 메모리로 가져오는 데 필요한 시간

- Miss rate : CPU가 요청한 데이터 중 캐시에 저장되지 않은 비율

📁Cache miss의 종류

cache miss는 크게 3가지의 경우가 발생한다.

-

cold miss : 해당 메모리 주소를 처음 불렀기 때문에 miss가 발생하는 경우이다. cache가 비워져있었기 때문에 어쩔 수 없이 발생한다.

-

conflict miss : 캐시 메모리에 A 데이터와 B 데이터를 저장해야 하는데, A와 B가 같은 캐시 메모리 주소에 할당되어 miss가 발생하는 경우이다.

A 데이터를 저장한 후, B 데이터가 같은 캐시 메모리 주소에 할당되어 저장되면 이후에 A 데이터를 읽어오려고 했을 때 miss가 발생한다. -

capacity miss : 캐시 메모리에 공간이 부족해서 miss가 발생하는 경우이다.

📖캐시 메모리의 구조와 작동 방식

📁Direct mapped Cache

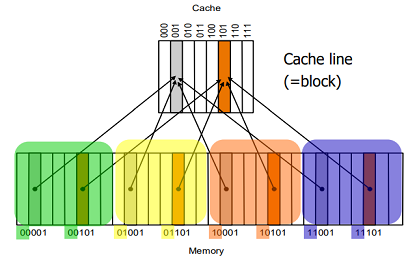

가장 기본적인 캐시 메모리의 구조로, 각 memory block이 cache의 정확히 한 block에만 대응된다. 예를 들어, memory의 00001에 위치한 block은 cache memory의 001에만 저장될 수 있다. 따라서 hit인지 miss인지 판단하기 위해 한 개의 cache block만 확인하면 된다.

memory block이 저장될 cache block의 주소는 (memory block 주소) % (cache의 block 수)로 구할 수 있다. 즉, 00000(0)부터 11111(31)을 111(8)로 나눈 나머지이므로 memory block 주소의 하위 세 자리이다.

그런데, 메모리는 캐시보다 크므로 여러 개의 memory block은 하나의 cache block을 공유한다. 예를 들어, 캐시의 회색 부분(001)에 저장된 데이터가 메모리의 4부분(00001, 01001, 10001, 11001) 중 어디에서 왔는지 알 수 있어야 한다. tag는 이러한 정보를 제공한다.

tag는 memory block 주소를 cache block 수로 나눈 몫으로, 이 경우 memory block 주소의 상위 두 자리이다.

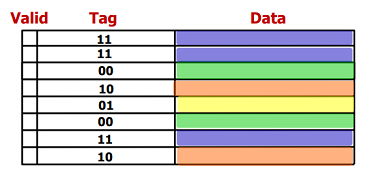

캐시 메모리는 valid, tag, data로 구성된다.

-

valid : 최초에는 0으로 세팅, 실제로 의미있는 데이터 들어오는 순간부터 1로 기록

-

tag : 어떤 memory block이 cache에 저장된 것인지에 대한 정보 저장된 부분

-

data : 실제 데이터가 저장된 부분

📁Fully associative Cache

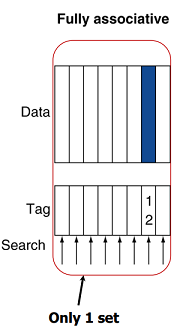

Fully associative cache는 direct mapped cache의 정반대 개념으로, memory block은 캐시 메모리의 비어있는 모든 block에 저장될 수 있다.

따라서 hit인지 miss인지 판단하기 위해 cache의 모든 block을 확인해야한다.

📁N-way set associative Cache

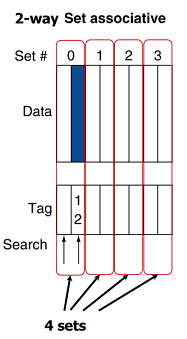

N-way set associative cache는 direct mapped cache와 fully associative cache의 중간쯤 개념이라고 할 수 있다. 캐시 메모리를 n개의 block(way)를 가진 set이라는 단위로 나누고, memory block을 하나의 set에서 비어있는 block에 저장하는 것이다. 다음은 2-way set associative cache이다.

memory block은 하나의 set에서 2개의 block 중 하나에 저장될 수 있으므로 hit인지 miss인지 판단하기 위해서는 block 2개를 모두 확인해야 한다. (memory block 주소) % (캐시의 set 수)를 계산하여 어느 set를 확인해야하는지 구할 수 있다.