전체적인 구상

Verilog는 (.v)라는 source file을 가진다.

그리고 source file의 검증 목적 testbench source file(.v)도 있다.

이 둘을 object code로 컴파일 후 simulation에서 확인하면 verilog 개발 환경이 잘 만들어진다.

컴파일은 Icarus Verilog로, simulation 확인은 gtkwave라는 프로그램을 사용해 확인할 것이다.

정리하자면

Source file

-> (compile)

object code

-> (vvp) : gtkwave가 읽을 수 있는 vcd 파일로 컴파일

VCD FILE 생성

->

시뮬레이션 확인

개발환경

- 기기 : 2023년 LG gram notebook

- CPU : AMD RYZEN 5

- RAM : 8GB

- OS : Windows 11 (UBUNTU WSL로 사용)

환경 구축

1. Icarus verilog 다운

$ sudo apt install -y iverilog버전확인은 간단하게

$ iverilog -V를 통해 확인할 수 있다.

2. gtk wave 다운

$ sudo apt install -y gtkwave3.간단한 source file로 확인

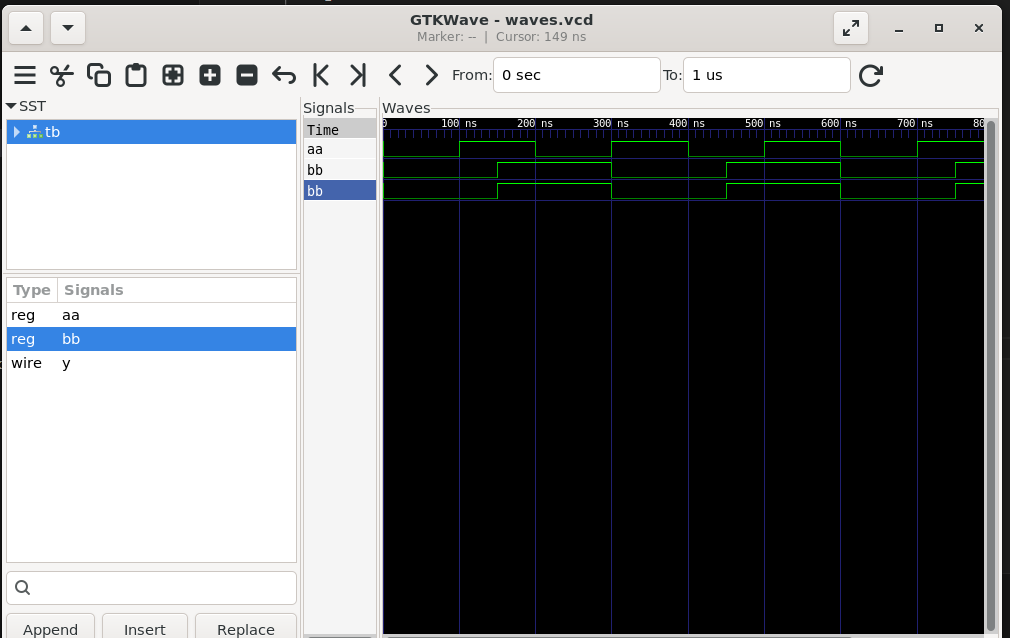

간단한 source file(dut.v)와 testbench (tb.v)로 잘 작동하는 지 확인했다.

// source file

module dut(input wire a, b, output wire y);

assign y = a & b;

endmodule//testbench file

`timescale 1ns/1ps

module tb;

reg aa;

reg bb;

wire y;

dut u_dut(

.a(aa),

.b(bb),

.y(y)

);

initial begin

$dumpfile("waves.vcd");//simv 작동한 wave vcd 파일 만들기

$dumpvars(0, tb);//모든 시간대를 전부 기록

end

initial aa=1'b0;

initial bb=1'b0;

always aa= #100~aa;

always bb= #150~bb;

initial begin

#1000

$finish;

end

endmodule4. 컴파일

$ iverilog -g2005 -o simv tb.v test.v verilog 2005년 버전으로 컴파일해서 목적파일 simv 만들기

$ vvp simvvvp 해석기가 simv 목적 코드 실행

이때 testbench에 시뮬레이션 task들, 예로 inital에 있는 코드들.. 이 실제로 동작

->vcd 파일 만들어짐

$ gtkwave waves.vcdvcd파일 gtakwave로 열어 가시적으로 파형 확인!

잘 나오네~

다음 단계..

이제 환경 구축은 끝났다. 만만한 ISA를 공부하러 가보자..