Designing Object Detection Models for TinyML: Foundations, Comparative Analysis, Challenges, and Emerging Solutions

논문

Hardware-aware NAS

최근 NAS의 발전으로 엄격한 하드웨어 기준의 제약 조건도 충족하도록 설계된 Hardware-aware NAS가 등장

주로 task 성능 향상에 초점을 맞춘 기존의 NAS와 다르게 HNAS는 배포 제약 조건을 NAS의 탐색 프로세스에 통합하여 성능과 효율성을 기반으로 최적의 아키텍처를 선택할 수 있다.

이러한 NAS는 MCU와 같은 리소스 제약이 있는 환경에서 중요하다

-

Micronets : 계산 복잡도를 제한하여 저전력 장치에서 모델을 실행할 수 있게하는 검색 기법 사용

-

MCUNet : 2단계 검색 전략

최적의 작업 성능을 위한 아키텍처 설계 후 MCU 메모리 제한에 맞게 아키텍처를 잘라냄

최근 연구에서는 VIT기반 지식 증류 전략에 LLM을 NAS에 활용하는 프레임워크 있음

3가지 단계로 진행되는 프레임워크

- 탐색 단계 : LLM이 아키텍처 탐색을 안내

- Full training 단계 : 탐색 단계에서 뽑은 최고 후보를 학습해서 성능 올림

- KD 단계 : 사전 학습된 ViT teacher가 student 모델에 지식 증류

탐색 시간을 12.5일에서 1.5으로 단축시키고, SRAM이 320KB인 MCU에서 배포 가능성을 보임

결론 : 임베디드 환경에서 HNAS가 유망하고, 향후 연구 방향을 열었다.

Optimizing Object Detection for TinyML

앞 섹션에서는 다른 컴퓨팅 환경에 맞춰 설계된 객체 탐지 최적화 기법들을 살펴봄

- 클라우드환경

- 엣지 AI

- 모바일 AI

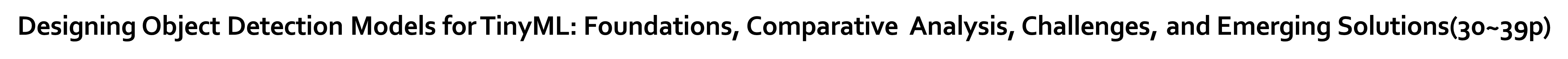

각 환경별로 연산 성능과 메모리 자원 수준이 크게 다르다.

클라우드 AI와 다르게 TinyML은 엄격한 제약 하에서 동작하며, 일반적으로 256~512KB메모리와 1MB 수준의 저장공간 정도만 제공되는 경우가 많다.

TinyML을 위한 객체 탐지 모델 최적화는 연산량을 줄이는 것뿐 아니라, 모델이 MCU의 제한된 메모리 안에 실제로 들어가도록 보장해야 한다.

앞 섹션에서 언급된 최적화 기법들을 적용하면, 객체 탐지 모델은 TinyML 환경 배포에 맞게 효과적으로 설계될 수 있지만, YOLO처럼 원래 GPU급 장치의 실시간 탐지를 위해 설계된 전통적인 모델들은 상당한 수정이 필요하다.

YOLO는 시간이 지나면서 nano/small과 같이 다양한 축소 버전이 등장했지만, 그럼에도 YOLO 계열의 모델들은 TinyML 응용에 부담이 되는 경우가 많다.

TinyML에서는 SRAM이 activation의 크기를 제한하고, Flash 메모리는 모델의 파라미터 크기를 제한한다.

또한 MCU는 일반 노트북의 CPU에 비해 훨씬 느리다.

모델 pruning은 복잡도를 줄이기 위한 핵심 전략으로 떠올랐다.

예를 들어, 필터 pruning을 도입해 구조적인 압축을 가능하게 하고, 성능을 크게 해치지 않으면서 추론 지연시간을 줄여 TinyML 객체 탐지에 적합하다고 말한다.

또한, 보조 네트워크(auxiliary network)를 활용한 depth pruning은 개별 필터가 아닌, 레이어 전체를 제거하고, 보조 네트워크가 정확도 손실을 보완하는 방식이다.

이러한 기법들은 MCU에서도 비교적 성능 저하를 최소화하며 더 정교한 모델을 돌릴 수 있게 한다.

계산 제약 외에도 TinyML 객체 탐지는 학습 데이터가 제한적이라 과적합 및 성능 저하 문제가 있는데, 이를 위해 데이터셋 distillation(데이터셋 증류)가 제안된다.

매우 작지만, 정보가 풍부한 학습 데이터를 합성하여, 저메모리 온디바이스 학습을 가능하게 하고, 큰 데이터셋의 의존을 줄인다.

특히, 연결이 불안정해 클라우드 업데이트를 자주하기 어려운 IoT기반 객체 탐지에 유용하다

MCUNet-YOLO

MCUNet-YOLO는 MCUNetV1 프레임워크를 기반으로 개발되었다.

MCUNetV1은 자원이 제한된 MCU에서 딥러닝 모델을 배포할 수 있도록 TinyNAS와 TinyEngine(추론 엔진)을 통합해 최적화한다.

- TinyNAS는 2단계 NAS 방법으로, 모바일과 임베디드 플랫폼의 자원 제약을 만족하도록 설계된 특수학 탐색 공간을 정교화하면서 시작한다.

이 탐색 공간은 “블록 조합”으로 구성할 수 있게 해서 다음을 선택 가능:

- 다양한 CONV 유형(일반/Depthwise separable/Moblie inverted bottleneck)

- 커널 크기(3x3/5x5)

- Skip connection

- 레이어 수 등

탐색 공간을 커버하는 방식은

- 입력 해상도 R ={48,64,80,...,224}

- 채널 scaling 배수 W={0.2,0.3,...,1.0}

이 조합으로 108개의 설정을 먼저 커버한 뒤, 각 설정 내에는 엄청나게 많은 네트워크 후보가 존재한다.

이렇게 방대한 탐색 공간에서 최적 모델을 효율적으로 찾기 위해, ont-shot NAS를 사용한다.

가능한 모든 서브네트워크를 포함하는 슈퍼넷을 가중치 공유 방식으로 학습하여 각 네트워크의 성능을 빠르게 추정한 후, 진화적 탐색을 통해 정확도와 자원 제약 간 균형이 가장 좋은 모델을 선택한다.

TinyEngine은 MCU용 메모리 efficieny 추론 라이브러리로, 각 후보 네트워크를 평가할 때, TinyEngine을 사용해 메모리 스케줄링을 최적화하고, 최적 피크 메모리 사용량을 측정한다.

일반 엔진은 layer-by-layer로 최적화하는 것과 다르게 TinyEngine은 네트워크 전체 토폴로지 기반으로 최적화한다.

토폴로지 기반:모델 전체를 노드로 보고 각 중간 activation이 언제 생성되고 언제 마지막으로 사용되는지를 전부 파악한뒤 메모리 스케줄링을 결정(어떤 걸 덮어 씌워도 되고, 어떤 걸 먼저 계산하고,,.. 등)

이를 통해, 메모리 사용은 최대 3.4% 감소하고, 추론 속도는 1.7~3.3배까지 증가하였다.

이렇게 만들어진 MCUNetV!을 YOLOv2 백본으로 사용하여 ImageNet 분류에서 70.1%의 성능과 객체 탐지에서 51.4%의 성능을 보임

MCUNetv2

MCUNetv2는 MCU에서 객체 탐지를 더 최적화하기 위해 더 개선하였다.

대표적으로, 패치 기반 추론 전략으로 layer간 메모리 분포 불균형 분제를 해결한다.

일반적인 layer-by-layer 실행은 네트워크 초반부에서 메모리 병목을 유발할 수 있는데, MCUNetv2는 layer를 작은 패치로 나눠 처리한다.

이를 통해 메모리 요구량을 크게 낮추고, 메모리가 제한된 장치에서도 고해상도 처리를 가능하게 한다.

패치기반 추론으로 인한 연산 오버헤드를 완화하기 위해, Receptive field를 재분배하는 방법도 제안하여, 초반 layer의 Receptive field를 전략적으로 줄여 입력 패치 크기와 연산 빈도를 낮추고, 후반부에서 Receptive field를 다시 늘려 성능을 유지하여 대규모 객체 탐지에서 높은 성능을 유지한다.

MCUNetv2는 NAS와 추론 스케줄링을 통합하여, 아키텍처 설계와 실행 전략을 동시에 최적화함으로써 MCU의 엄격한 메모리, 지연시간 제약에 대해 효율적인 성능을 제공한다.

MCUNetv2는 ImageNet에서 71.7%로 더 좋은 결과를 보였고, 객체 탐지에서는 YOLOv3의 백본으로 사용되어 68.3%의 성능을 보였다.

TinyissimoYOLO

TinyissimoYOLO는 MCU의 극단적 자원 제약을 겨냥한 초경량·고효율 객체탐지 모델

설계 특징은 입력 해상도, 탐지 클래스 수, 첫 layer 커널 크기 등을 유연하게 조절가능하여 정확도와 연산량 간 트레이드오프를 하드웨어에 맞게 조정가능하다.

핵심적인 최적화로는 네트워크 전체에 int 8 양자화를 적용하여 32bit 대비 메모리와 모델 크기가 4배 감소하였다.

양자화는 QuantLab 프레임워크를 활용한 QAT를 수행하여

8bit모델이 full-precision 모델에 가까운 정확도를 유지하게 하면서도, 정수 연산만으로 효율적인 배포가 가능하게 한다.

QuantLab은 full-precision모델을 QAT용 fake-quantized 모델로 변환 후 배포 가능한 integer 모델로 자동 변환하여, 다양한 하드웨어에 쉽게 배포할 수 있게 한다.

fake-quantized

학습할 때는 float으로 계싼하지만 양자화된 척 흉내를 내는 것학습 중에 정수로 계산은 안하지만, 정수로 바꿨을 때 생길 오차를 미리 겪게 하는 것

TinyissimoYOLO는 객체 탐지에서는 56.4%의 성능과 연산량은 55MMac을 자랑하며 초저전력 MCU에서 실시간 객체 탐지에 적합하다.

EtinyNet-SSD

EtinyNet-SSD는 MCU에서 효율적인 객체 탐지를 위해 설계된 모델로

- DLB

- ASQ

로 구성되어 있다

-

DLB(Depthwise Linear Block)

Depthwise Conv layer를 linear layer와 자연스럽게 결합하여 모델의 연산량을 크게 줄이면서도 정확도를 유지시킨다.

이러한 설계 덕분에 네트워크가 가볍고 효율적이어서 MCU 배포에 적합

-

ASQ(Adaptive Scale Quantization)

입력 데이터에 따라 가중치와 활성화값의 양자화 스케일을 동적으로 조정하는 양자화 기법으로,

양자화된 파라미터의 정밀도를 상황에 맞게 최적화하여 메모리 사용량과 연산 오버헤드를 최소화한다.

EtinyNet의 백본을 SSD 아키텍처와 결합하여 객체 탐지 성능을 끌어올리며, DLB와 ASQ를 함께 적용하여 MCU 자원 내에서 효율적인 성능 달성

객체 탐지에서 56.4% 성능을 보여준다.

XiNet-YOLOv7

자원이 제한된 장치(MCU 포함)에서의 객체 탐지를 위해

하드웨어 효율을 최우선으로 고려한 YOLOv7 계열 최적화 접근을 제시.

-

연산자(operators) 선택을 하드웨어 관점에서 재설계

표준/Depthwise/Pointwise convolution을 광범위하게 분석해 에너지 효율과 성능이 좋은 연산자 조합을 기반으로 아키텍처를 구성

-

HAS(Hardware-Aware Scaling)

HAS는 RAM, Flash, 연산량(operations)을 서로 독립적으로 스케일링할 수 있게 해주는 기법.

즉, “모델을 줄인다”가 아니라,

어떤 하드웨어는 RAM이 병목이면 RAM 중심으로,

어떤 하드웨어는 Flash가 병목이면 Flash 중심으로,

어떤 하드웨어는 연산량이 병목이면 MACs 중심으로

각 자원 예산에 맞춰 따로 조절 가능하게 만드는 접근.

“S / M / L” 세 가지 변형 제공

S: 저전력·저에너지 소비 중심 (XiNet-YOLOv7-S)

L: 더 높은 정확도 중심 (XiNet-YOLOv7-L)

(M은 중간 지점)

S / M / L이 각각 객체 탐지 성능 54% / 67% / 74.9%를 달성

TinyML 환경에서 에너지/메모리 사용을 크게 줄이면서도 실시간 OD에 적합함을 강조.

Open Challenges and Future Works

최근 객체 탐지(OD)는 대규모 데이터셋에서 SOTA 성능을 낼 만큼 크게 발전했지만, 이를 임베디드 시스템/TinyML에 배포하는 건 여전히 어렵다. 이유는 메모리, 연산량, 에너지 제약이 너무 강하기 때문이다

한편 Transformer 기반 모델, 생성형 AI, VLM, 하드웨어 인지 최적화 같은 최신 기법들이 새로운 가능성을 열고 있지만, 극한 제약 환경에서 실시간성·효율·적응성을 동시에 만족하려면 추가 연구가 필요하다.

이 절에서는 TinyML/임베디드 OD 배포의 미해결 과제를 정리하고, 해결을 위한 연구 방향을 제안한다.

1. 고해상도 이미지 처리

- 문제

해상도를 낮추면 연산은 쉬워지지만 작은/먼 객체 탐지가 어려워짐.

- 미래 방향

상황에 따라 해상도를 바꾸는 적응형 해상도 전략(context/task 기반 동적 조절)

전체 고해상도를 다 처리하지 말고,

특징 수준에서 관심 영역(ROI)만 찾아

그 부분만 고해상도로 처리하는 방식(예: ESOD)

TinyML에서는 “필요한 공간 영역만 켜서” 처리하는 컨텍스트 인지 패치 기반 처리로, MCU에서도 고해상도 처리를 가능하게 하자는 제안

2. 에너지 효율

- 문제

IoT/배터리 장치에서는 전력이 핵심인데, 전통 DNN은 전력 소모가 큼.

- 미래 방향

스파이킹 신경망(SNN) 기반의 객체 탐지 모델을 최적화하고, 일반 뉴런과 스파이킹 뉴런을 섞는 하이브리드 구조를 탐색하는 데 초점을 맞춰야 한다.

SNN

일반적인 신경망은 입력과 feature가 연속적인 실수값으로 매번 계산되지만, SNN은 정보가 0/1과 같은 짧은 이벤트(스파이크)로 전달되어, 뉴런이 이 스파이크를 누적하다가 임계치를 넘으면 스파이크를 다시 전달하는 방식

3. 다양한 환경에서의 강건성

- 문제

조명/날씨 변화, 가림(occlusion) 등 현실 조건이 바뀌면 성능이 쉽게 흔들림.

- 미래 방향

- 전이학습, 도메인 적응으로 환경 차이를 흡수

- 강한 데이터 증강으로 현실의 어려운 조건을 학습 중에 시뮬레이션하여 일반화를 강화한다.

4. 실시간 처리

- 문제

자율주행/감시 같은 응용은 낮은 latency가 필수.

- 미래 방향

인간 뇌 처리방식과 유사한 SN이 빠른 반응에 잠재력이 있어서 SNN을 실시간 객체 탐지에 맞게 최적화한다.

5. 데이터셋 한계와 편향

- 문제

임베디드/TinyML에 특화된 크고 다양한 데이터셋 부족 → 모델 편향/성능 제한.

- 미래 방향

- 합성 데이터 생성 + 데이터 증강으로 다양성과 품질 강화

- 비지도/반지도 학습으로 라벨 의존도를 줄이기

6. 하드웨어-소프트웨어 공동 설계

- 문제

임베디드 OD 최적화는 HW와 SW의 결합이 결정적.

- 미래방향

LLM을 아키텍처 탐색에 활용하면, 특정 하드웨어에 맞는 구조를 찾는 탐색 비용을 줄이고 더 빨리 효율적인 모델을 찾을 수 있다.

7. AI 가속기 칩

- 현황

MCU에 통합되는 전용 가속기가 객체 탐지 효율을 크게 높이고 있는데 GPU나 TPU와 같은 고전력 장치가 아니라 MCU급 배포에 맞춘 latency가 낮고 저전력인 가속이 포인트이다.

- 미래 방향

다양한 가속기에 맞춘 객체 탐지 모델 최적화와 함께 하드웨어의 구성과 메모리 계층 등이 속도와 정확도에 미치는 영향까지 함께 평가해야 한다.

8. 하드웨어 인지 공동 설계와 RISC-V 기회

- 문제 의식

임베디드에서 실시간+고효율 객체탐지를 하려면 알고리즘 설계와 하드웨어를 강하게 결합해야 하는데,

범용적인 알고리즘을 억지로 끼워맞추기보다, 처음부터 하드웨어 제약을 고려한 하드웨어 지향 모델이 중요하다

- 미래 방향

연산 효율과 하드웨어 비용을 함께 최적화하는 HNAS가 주목받는다.

RISC-V 같은 오픈소스 ISA는 모듈성/유연성/저비용 커스터마이징을 제공해 임베디드 AI에 유리하다

ISA는 Instruction Set Architecture(명령어 집합 구조)의 약자로 CPU가 “어떤 기계어 명령을 이해하고”, 그 명령이 “어떤 동작을 한다고 약속하는 규칙(표준)

즉, RISC-V 같은 오픈(표준) ISA는 “CPU가 이해하는 명령어 규칙”을 공개해 둔 거라서, 누구나 그 규칙을 기반으로 자기 목적(예: TinyML)에 맞는 맞춤형 프로세서/가속기를 설계할 수 있게 해준다

9. TinyML을 위한 Transformer 기반 객체탐지 설계

- 배경

Transformer 계열은 여러 비전 과제에서 CNN을 넘어서는 성능을 내면서, 객체탐지(OD)에도 확산되고 있다

- 문제

MCU급 장치에서는 Transformer 기반 탐지기는 연산량/메모리 요구량 때문에 배포가 어렵다.

CNN은 연산이 “국소적(local)”인 반면, Transformer의 self-attention은 입력 크기에 따라 연산/메모리 비용이 대체로 𝑂(𝑁^2)로 커져

제한된 SRAM

제한된 전력 예산

에서 비효율적이다

- 연구 방향

- KD(지식 증류)로 Transformer 표현을 압축 모델로 이전

- TinyML 친화 Transformer 기법 적용 사례: MCUFormer

- 모델 구조와 하드웨어 역량 간 정렬(alignment)을 맞추는 연구가 필요.

- Transformer–CNN 하이브리드, Remote 센싱 OD 등에 적용 및 확장

- 효율적인 어텐션을 도입하여, 전역적인 특징을 사용하는 것은 유지하되, 메모리 오버헤드는 감소시킨다.

- NAS로 TinyML 최적 Transformer 구조 찾기

- MCU용 연산 라이브러리 활용

10. TinyML OD의 다음 단계: 멀티모달 학습 & 생성형 AI

Transformer를 단순히 “가볍게” 만드는 것 외에도, TinyML OD의 다음 목표는 생성형 AI와 멀티모달 AI를 통해 탐지의 능력을 확장하는 것

- 왜?

TinyML 환경은 학습 데이터가 부족하기 쉬워서 작은 탐지기는 쉽게 과적합하거나 일반화가 약해질 수 있음.

- 연구 방향

- 생성형 AI로 데이터 품질/다양성 향상

- 멀티모달 KD : 단순히 모델 크기만 줄이는 distillation이 아니라, VLM/대형 Transformer의 크로스도메인 지식(텍스트·컨텍스트 추론)까지 전달하는 방향이 유망

- Transformer OD 전용 압축을 TinyML 환경에 맞게 재설계해야 함

- 제로샷 VLM이 재학습 없이 새로운 클래스도 탐지하는(open-set) 방향을 가능하게 할 수 있으며, TinyML OD를 더 유연하고 확장 가능한 시스템으로 만들 잠재력이 있다고 봄.

Conclusion

이 논문은 임베디드 환경에서 객체탐지 성능을 높이기 위한

양자화(quantization)

프루닝(pruning)

KD(지식 증류)

NAS

같은 모델 압축/최적화 기법들을 포괄적으로 서베이했다.

또한 소비자 전자기기, IoT, 엣지 컴퓨팅 맥락에서

“정확도를 유지하면서 효율을 올리는 데” 이 기법들이 어떤 효과가 있는지 분석했고,

최적화 성공을 평가하는 핵심 지표들도 정리했으며,

각 방법의 실용적 영향에 대한 비교 인사이트를 제공하였다.

Recent Large Language Models (LLMs) have reached hyperscale dimensions. Consequently, the search space has become prohibitively vast, leading to the observation that Neural Architecture Search (NAS) is losing traction. What is your perspective on this?